Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки информации о состоянии объекта, поступающей в виде совокупности случайных процессов с помехами.

Известно устройство для контроля случайных процессов с помехами.

Однако указанное устройство осуществляет удаление недостоверных значений в выборках ограниченного объема,что приводит к потере информации о контролируемом процессе в моменты времени, соответствующие исключаемым значениям, и, следовательно, к невысокой достоверности результатов контроля при сильном искажении контролируемых параметров помехами.

Известно также устройство для контроля случайных процессов с помехами, содержащее последовательно соединенные первый блок памяти первый блок суммирования if первый блок деления, а также блок умножения, второй блоктсуммирования, второй блок деления, счетчик, второй и третий блок памяти, третий блок суммирования, задатчик числа опрашиваемых датчиков, генератор тактовых импульсов, делителс частоты, соединенный первым управляющим выходом с первыми управляющими входами первого блока деления, второго блока памя i и и со счетным входом счетчика вторым управляющим выходом - с первыми управляющими входами первого и третьего блоков памяти, третьим управляющим выходом - с вторыми управляющими входа 4-N

СЛ

ч

ми первого, второго и третьего блоков памяти, четвертым управляющим выходом - с третьим управляющим входом первого блока памяти, а командным выходом - с входами разрешения обработки сигналом блоков памяти с первого по третий и третьего блока суммирования, информационные вход и выход которого подключены соответственно к второму информационному выходу первого блока памяти и к информационному входу третьего блока памяти, входы первого и второго сомножителей и выход блока умножения связаны соответственно с выходами третьего блока памяти и второго блока деления и с вторым информационным входом первого блока памяти, первый информационный вход которого подключен к входу устройства, кодовый выход счетчика соединен с адресными входами первого и второго блоков памяти, вход делителя и выход первого блока деления подключены соответственно к выходу задатчика числа опрашиваемых датчиков параметра и к информационному входу второго блока памяти, первый и второй информационные выходы второго блока памяти соединены соответственно с выходом устройства и с входом делимого второго блока деления вход делителя которого связан с выходом второго блока суммирования, вход которого подсоединен к третьему информационному выходу второго блока памяти.

Известное устройство осуществляет многоразовое накапливание п значений измеряемого параметра в m выборках с оптимизацией зтих значений, учитывающей их статистические и энергетические характеристики и осуществляемой после каждого цикла накапливания для увеличения отношения сигнал - помеха при контроле случайного процесса.

Недостатком известного устройства является использование фиксированного количества циклов накапливания значений контролируемого параметра (циклов обработки информации), что приводит к необходимости корректировки указанной величины в зависимости от информационно-статистических характеристик контролируемого процесса.

Цель изобретения - повышение производительности и качества контроля за счет автоматического задания количества циклов обработки информации о случайном процессе в зависимости от его информационно-статистических характеристик.

Поставленная цель достигается тем, что в устройство для контроля случайных процессов с помехами, содержащее три блока оперативной памяти, три сумматора, два

блока деления, задатчик количества выборок, генератор тактовых импульсов и блок умножения, вход первого сомножителя которого соединен с выходом второго блока

деления, вход второго сомножителя - с выходом второго блока оперативной памяти, а выход - с первым информационным входом первого блока оперативной памяти, выход которого связан с информационным входом

второго сумматора, выход которого подключен к входу делимого первого блока деления, вход делителя которого соединен с выходом згдатчика числа выборок, а выход

-с информационными входами третьего сумматора и третьего блока оперативной

памяти, первый выход которого связан с входом делимого второго блока деления, вход делителя .которого подключен к выходу третьего сумматора, информационный вход

второго блока оперативной памяти соединен с выходом первого сумматора, введены блок управления и блок анализа результатов контроля, выход которого соединен с входом остановки

блока управления, а информационный вход

-с выходом второго блока деления, вход задания знака произведения блока умножения связан со знаковым выходом первого блока оперативной памяти, второй информационный вход которого и информационный вход первого сумматора подключены к информационному входу устройства, выход генератора тактовых импульсов соединен с тактовым входом блока управления, второй

выход третьего блока оперативной памяти служит информационным выходом устройства, адресные выходы блока управления соединены с адресными входами всех блоков оперативной памяти, а управляющие

выходы - с управляющими входами всех блоков оперативной памяти, сумматоров, блоков деления, блока умножения и блока анализа результатов контроля, вход запуска блока управления является входом запуска

устройства.

Работа устройства основана на том, что с помощью введенных дополнительных блоков производится оценка величины уменьшения энтропии выборки усредненных значений (текущих результатов контроля), полученной в данном цикле обработки информации, по сравнению с энтропией аналогичной выборки в предыдущем цикле: АН

Нк - Нк-1, где Нк - значение энтропии для К-го цикла обработки.

Циклы обработки информации повторяются до тех пор, пока величина АН не достигнет предварительно установленного значения энтропии е, т.е. при процесс обработки завершается.

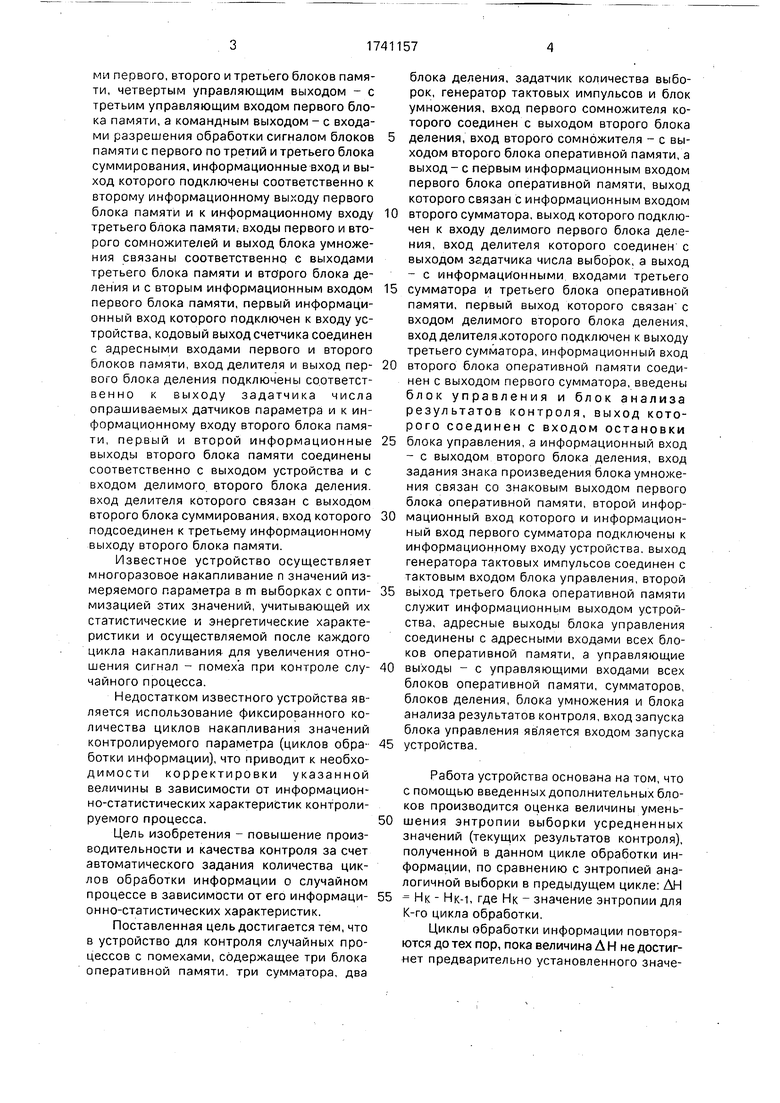

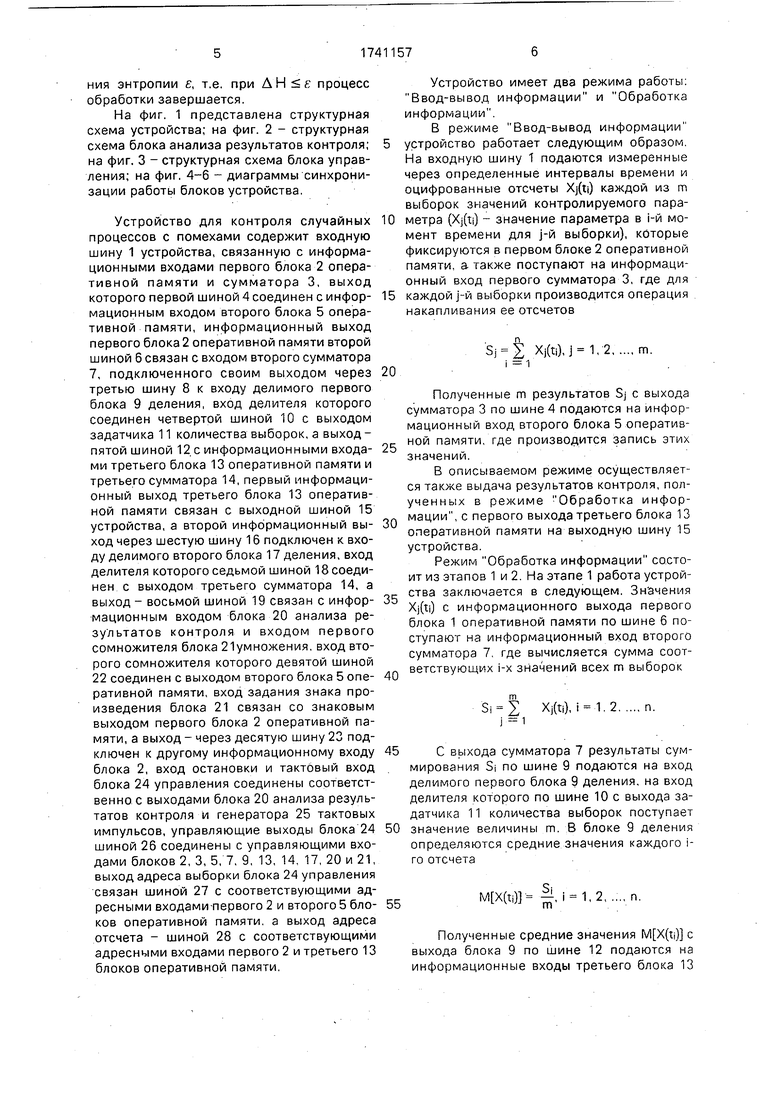

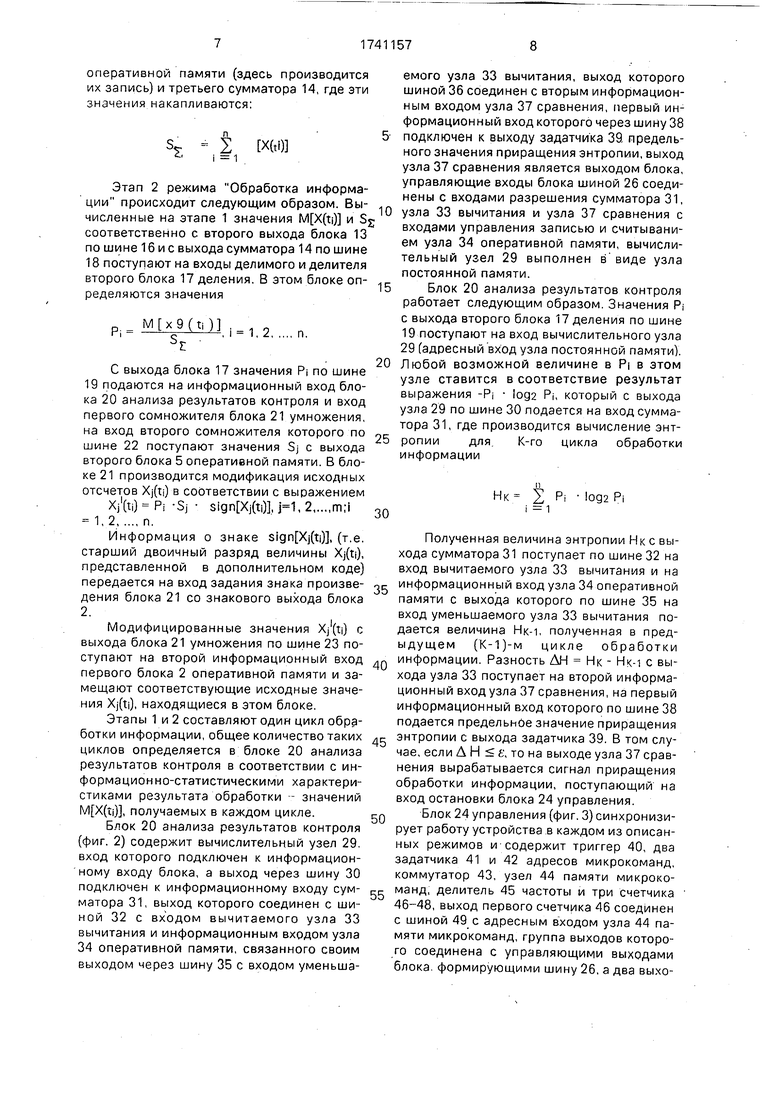

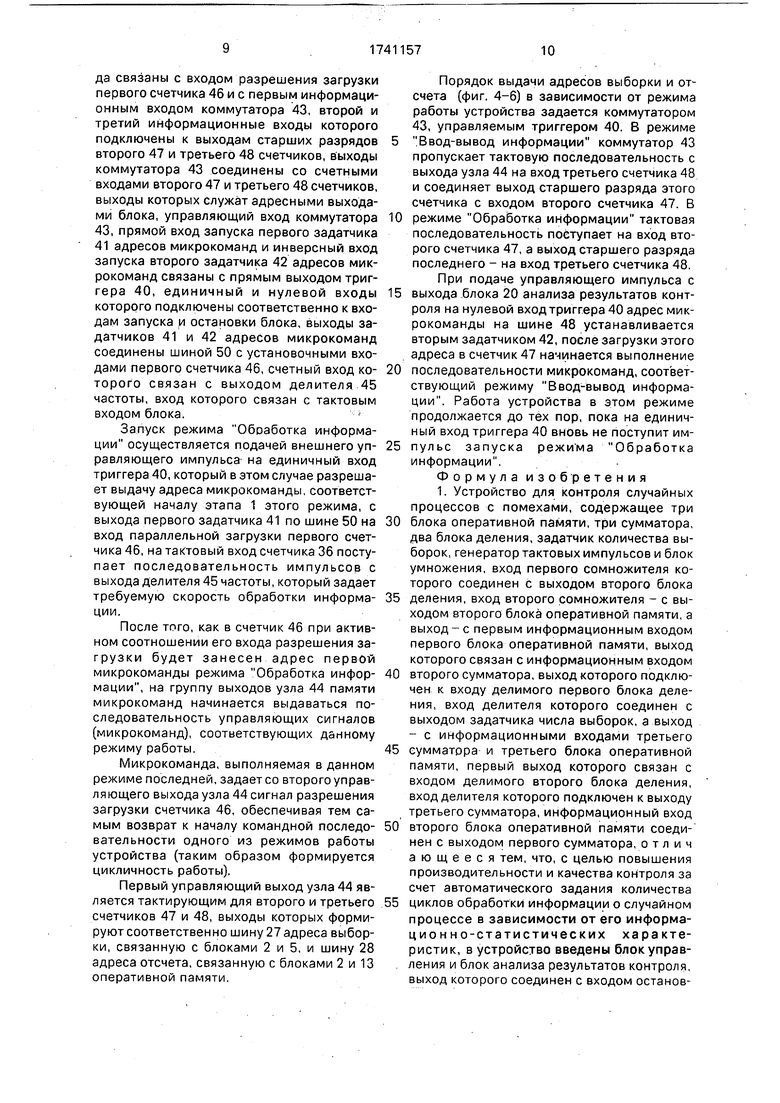

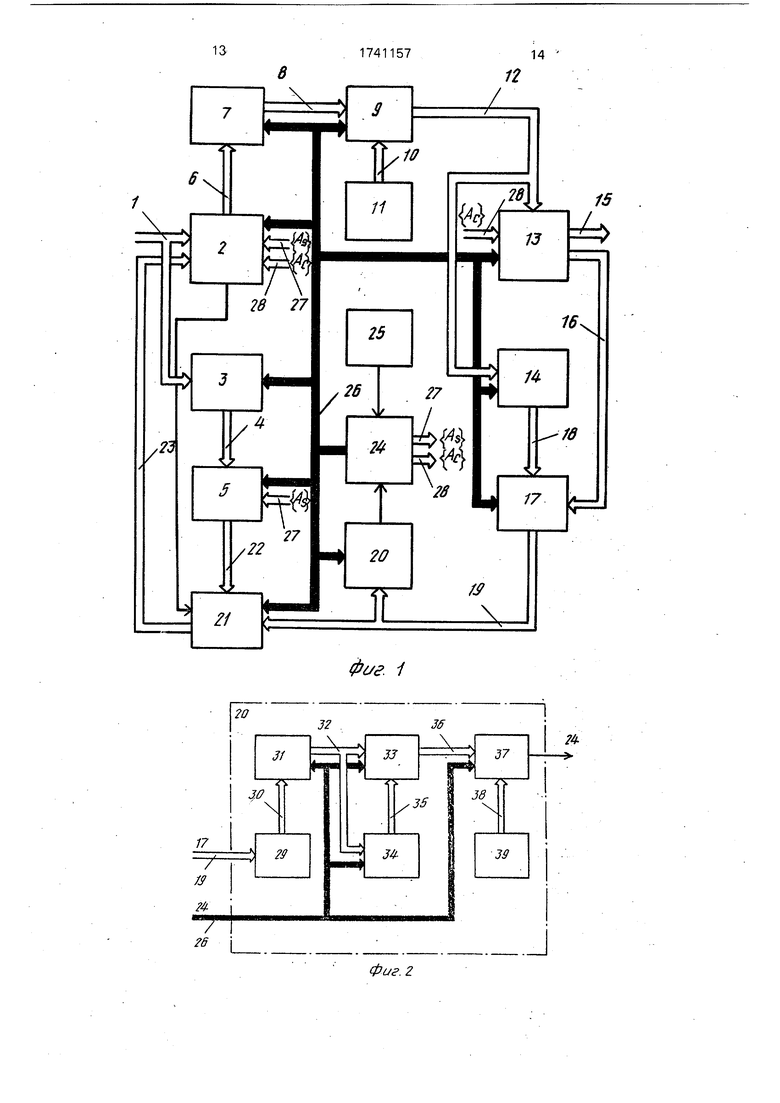

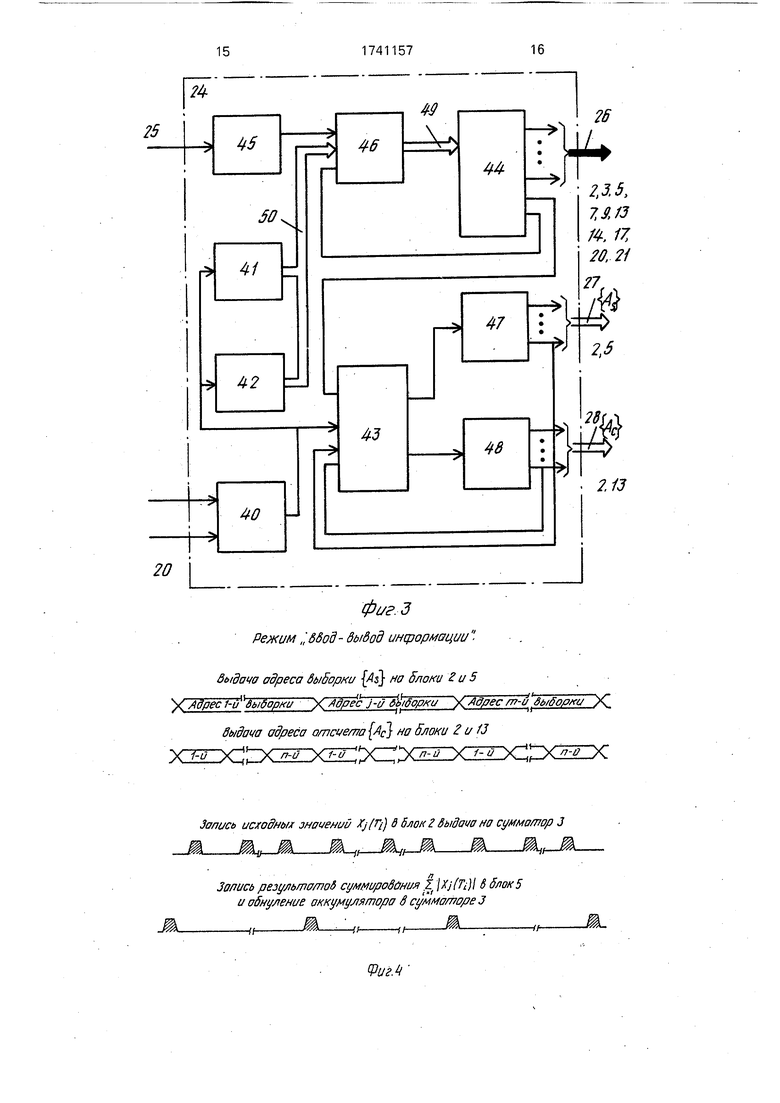

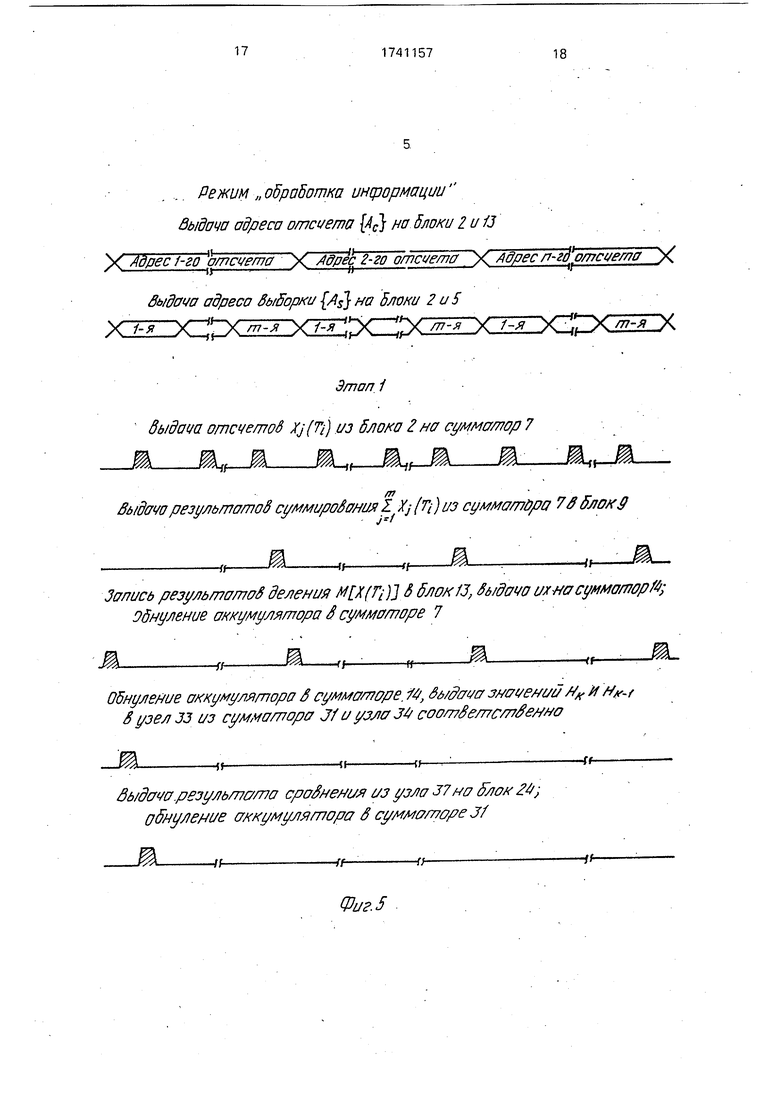

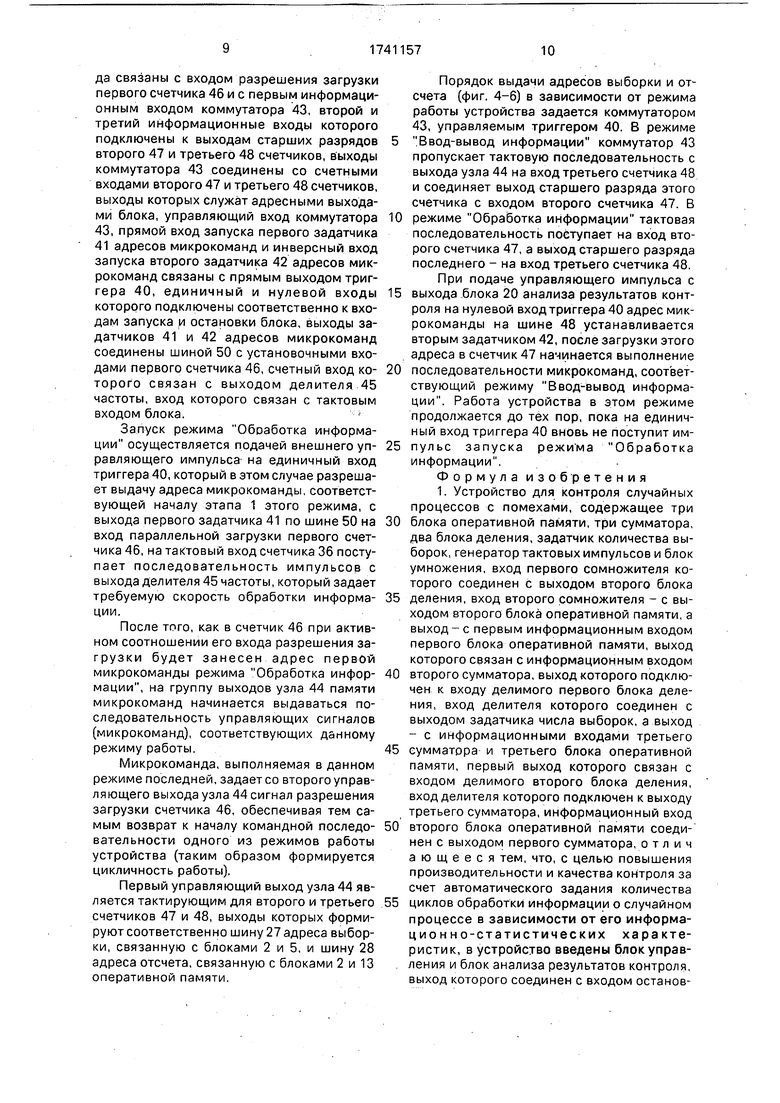

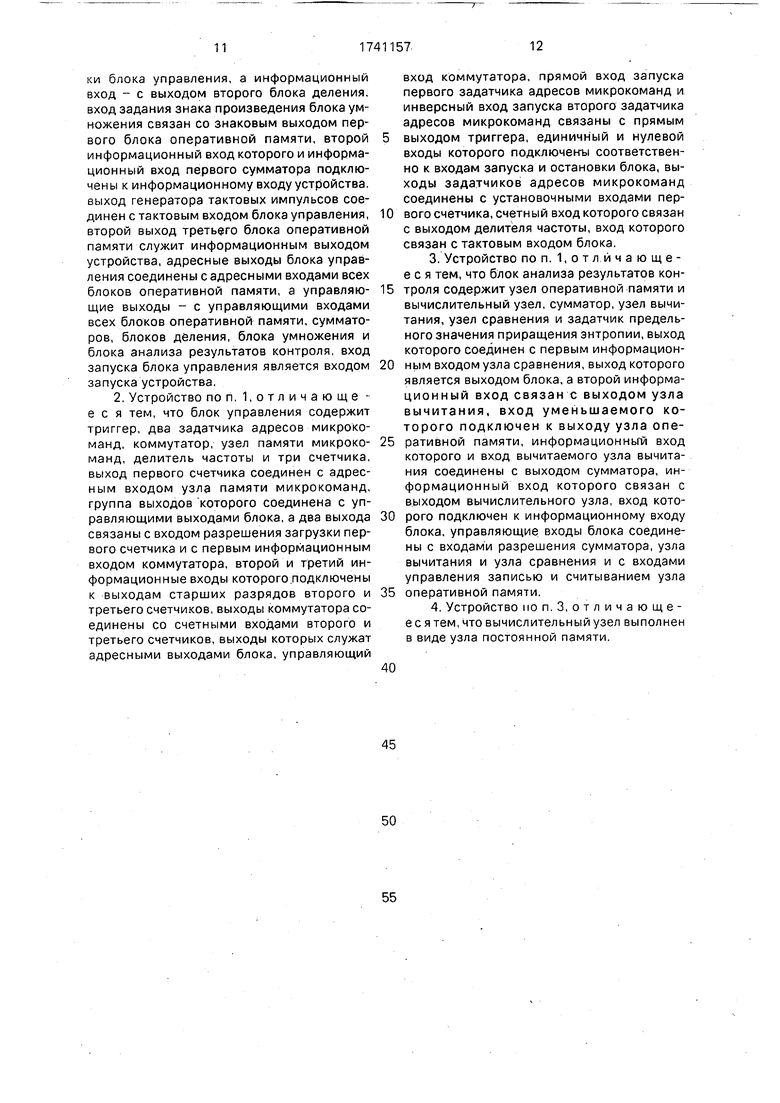

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока анализа результатов контроля; на фиг. 3 - структурная схема блока управления; на фиг. 4-6 - диаграммы синхронизации работы блоков устройства.

Устройство для контроля случайных процессов с помехами содержит входную шину 1 устройства, связанную с информационными входами первого блока 2 оперативной памяти и сумматора 3, выход которого первой шиной 4 соединен с информационным входом второго блока 5 оперативной памяти, информационный выход первого блока 2 оперативной памяти второй шиной 6 связан с входом второго сумматора 7, подключенного своим выходом через третью шину 8 к входу делимого первого блока 9 деления, вход делителя которого соединен четвертой шиной 10 с выходом задатчика 11 количества выборок, а выход- пятой шиной 12с информационными входами третьего блока 13 оперативной памяти и третьего сумматора 14, первый информационный выход третьего блока 13 оперативной памяти связан с выходной шиной 15 устройства, а второй информационный выход через шестую шину 16 подключен к входу делимого второго блока 17 деления, вход делителя которого седьмой шиной 18 соединен с выходом третьего сумматора 14, а выход - восьмой шиной 19 связан с информационным входом блока 20 анализа результатов контроля и входом первого сомножителя блока 21умножения, вход второго сомножителя которого девятой шиной 22 соединен с выходом второго блока 5 оперативной памяти, вход задания знака произведения блока 21 связан со знаковым выходом первого блока 2 оперативной памяти, а выход - через десятую шину 23 подключен к другому информационному входу блока 2, вход остановки и тактовый вход блока 24 управления соединены соответственно с выходами блока 20 анализа результатов контроля и генератора 25 тактовых импульсов, управляющие выходы блока 24 шиной 26 соединены с управляющими входами блоков 2, 3, 5, 7, 9, 13, 14, 17, 20 и 21, выход адреса выборки блока 24 управления связан шиной 27 с соответствующими адресными входами-первого 2 и второго 5 блоков оперативной памяти, а выход адреса отсчета - шиной 28 с соответствующими адресными входами первого 2 и третьего 13 блоков оперативной памяти.

Устройство имеет два режима работы: Ввод-вывод информации и Обработка информации.

В режиме Ввод-вывод информации

устройство работает следующим образом. На входную шину 1 подаются измеренные через определенные интервалы времени и оцифрованные отсчеты Xj(tj) каждой из m выборок значений контролируемого параметра (Xj(ti) - значение параметра в i-й момент времени для j-й выборки), которые фиксируются в первом блоке 2 оперативной памяти, а также поступают на информационный вход первого сумматора 3, где для

каждой j-й выборки производится операция накапливания ее отсчетов

Sj S Xj(ti),j 1,2m.

i 1

Полученные m результатов Sj с выхода сумматора 3 по шине 4 подаются на информационный вход второго блока 5 оперативной памяти, где производится запись этих значений.

В описываемом режиме осуществляется также выдача результатов контроля, полученных в режиме Обработка информации, с первого выхода третьего блока 13 оперативной памяти на выходную шину 15 устройства.

Режим Обработка информации состоит из этапов 1 и 2. На этапе 1 работа устройства заключается в следующем. Значения Xj(ti) с информационного выхода первого блока 1 оперативной памяти по шине 6 поступают на информационный вход второго сумматора 7, где вычисляется сумма соответствующих i-x значений всех m выборок

Si Z

j - 1

Xj(ti), i 1.2п.

С выхода сумматора 7 результаты суммирования Si по шине 9 подаются на вход делимого первого блока 9 деления, на вход делителя которого по шине 10 с выхода задатчика 11 количества выборок поступает значение величины т. В блоке 9 деления определяются средние значения каждого i- го отсчета

55

(ti) |f. 1 1.2п.

Полученные средние значения (ti} с выхода блока 9 по шине 12 подаются на информационные входы третьего блока 13

оперативной памяти (здесь производится их запись) и третьего сумматора 14, где эти значения накапливаются:

ЭГ,

у i 1

X(t0

Этап 2 режима Обработка информации происходит следующим образом. Вы- , численные на этапе 1 значения (ti) и Sj соответственно с второго выхода блока 13 по шине 16 и с выхода сумматора 14 по шине 18 поступают на входы делимого и делителя второго блока 17 деления. В этом блоке оп- ,,- ределяются значения

р (ti)2

i iQ, I I, Ј, ..., II.

ЬЕ

С выхода блока 17 значения PJ по шине 19 подаются на информационный вход блока 20 анализа результатов контроля и вход первого сомножителя блока 21 умножения, на вход второго сомножителя которого по шине 22 поступают значения Sj с выхода второго блока 5 оперативной памяти. В блоке 21 производится модификация исходных отсчетов Xj(ti) в соответствии с выражением

Xj (t,) Pi -Sj (ti), , 2m;i

1,2n.

Информация о знаке (ti), (т.е. старший двоичный разряд величины Xj(ti), представленной в дополнительном коде) передается на вход задания знака произведения блока 21 со знакового выхода блока 2.

Модифицированные значения Xj(ti) с выхода блока 21 умножения по шине 23 поступают на второй информационный вход первого блока 2 оперативной памяти и замещают соответствующие исходные значения Xj(ti), находящиеся в этом блоке.

Этапы 1 и 2 составляют один цикл обработки информации, общее количество таких циклов определяется в блоке 20 анализа результатов контроля в соответствии с информационно-статистическими характеристиками результата обработки - значений (tj), получаемых в каждом цикле.

Блок 20 анализа результатов контроля (фиг. 2) содержит вычислительный узел 29. вход которого подключен к информационному входу блока, а выход через шину 30 подключен к информационному входу сумматора 31, выход которого соединен с шиной 32 с входом вычитаемого узла 33 вычитания и информационным входом узла 34 оперативной памяти, связанного своим выходом через шину 35 с входом уменыиа,-

0

5

емого узла 33 вычитания, выход которого шиной 36 соединен с вторым информационным входом узла 37 сравнения, первый информационный вход которого через шину 38 подключен к выходу задатчика 39 предельного значения приращения энтропии, выход узла 37 сравнения является выходом блока, управляющие входы блока шиной 26 соединены с входами разрешения сумматора 31, узла 33 вычитания и узла 37 сравнения с входами управления записью и считыванием узла 34 оперативной памяти, вычислительный узел 29 выполнен в виде узла постоянной памяти.

Блок 20 анализа результатов контроля работает следующим образом. Значения Pi с выхода второго блока 17 деления по шине 19 поступают на вход вычислительного узла 29 (адресный вход узла постоянной памяти). Любой возможной величине в PI в этом узле ставится в соответствие результат выражения -Pi (092 PI, который с выхода узла 29 по шине 30 подается на вход сумматора 31, где производится вычисление энтропии для К-го цикла обработки информации

30

Нк Ј Р,

i 1

IOQ2 Pi

5

0

5

0

5

Полученная величина энтропии Икс выхода сумматора 31 поступает по шине 32 на вход вычитаемого узла 33 вычитания и на информационный вход узла 34 оперативной памяти с выхода которого по шине 35 на вход уменьшаемого узла 33 вычитания подается величина Нк-1, полученная в предыдущем (К-1)-м цикле обработки информации. Разность ДН Нк - Нк-1 с выхода узла 33 поступает на второй информационный вход узла 37 сравнения, на первый информационный вход которого по шине 38 подается предельное значение приращения энтропии с выхода задатчика 39. В том случае, если Д Н е, то на выходе узла 37 сравнения вырабатывается сигнал приращения обработки информации, поступающий на вход остановки блока 24 управления.

Блок 24 управления (фиг. 3) синхронизирует работу устройства в каждом из описанных режимов и содержит триггер 40, два задатчика 41 и 42 адресов микрокоманд, коммутатор 43, узел 44 памяти микрокоманд, делитель 45 частоты и три счетчика 46-48, выход первого счетчика 46 соединен с шиной 49 с адресным входом узла 44 памяти микрокоманд, группа выходов которого соединена с управляющими выходами блока формирующими шину 26, а два выхода связаны с входом разрешения загрузки первого счетчика 46 и с первым информационным входом коммутатора 43, второй и третий информационные входы которого подключены к выходам старших разрядов второго 47 и третьего 48 счетчиков, выходы коммутатора 43 соединены со счетными входами второго 47 и третьего 48 счетчиков, выходы которых служат адресными выходами блока, управляющий вход коммутатора 43, прямой вход запуска первого задатчика 41 адресов микрокоманд и инверсный вход запуска второго задатчика 42 адресов микрокоманд связаны с прямым выходом триггера 40, единичный и нулевой входы которого подключены соответственно к входам запуска и остановки блока, выходы за- датчиков 41 и 42 адресов микрокоманд соединены шиной 50 с установочными входами первого счетчика 46, счетный вход которого связан с выходом делителя 45 частоты, вход которого связан с тактовым входом блока.

Запуск режима Обработка информации осуществляется подачей внешнего управляющего импульса на единичный вход триггера 40, который в этом случае разрешает выдачу адреса микрокоманды, соответствующей началу этапа 1 этого режима, с выхода первого задатчика 41 по шине 50 на вход параллельной загрузки первого счетчика 46, на тактовый вход счетчика 36 поступает последовательность импульсов с выхода делителя 45 частоты, который задает требуемую скорость обработки информации.

После того, как в счетчик 46 при активном соотношении его входа разрешения за- грузки будет занесен адрес первой микрокоманды режима Обработка информации, на группу выходов узла 44 памяти микрокоманд начинается выдаваться последовательность управляющих сигналов (микрокоманд), соответствующих данному режиму работы.

Микрокоманда, выполняемая в данном режиме последней, задаетсо второго управляющего выхода узла 44 сигнал разрешения загрузки счетчика 46, обеспечивая тем самым возврат к началу командной последовательности одного из режимов работы устройства (таким образом формируется цикличность работы).

Первый управляющий выход узла 44 является тактирующим для второго и третьего счетчиков 47 и 48, выходы которых формируют соответственно шину 27 адреса выборки, связанную с блоками 2 и 5, и шину 28 адреса отсчета, связанную с блоками 2 и 13 оперативной памяти.

Порядок выдачи адресов выборки и отсчета (фиг. 4-6) в зависимости от режима работы устройства задается коммутатором 43, управляемым триггером 40. В режиме

Ввод-вывод информации коммутатор 43 пропускает тактовую последовательность с выхода узла 44 на вход третьего счетчика 48 и соединяет выход старшего разряда этого счетчика с входом второго счетчика 47. В

0 режиме Обработка информации тактовая последовательность поступает на вход второго счетчика 47, а выход старшего разряда последнего - на вход третьего счетчика 48. При подаче управляющего импульса с

5 выхода блока 20 анализа результатов контроля на нулевой вход триггера 40 адрес микрокоманды на шине 48 устанавливается вторым задатчиком 42, после загрузки этого адреса в счетчик 47 начинается выполнение

0 последовательности микрокоманд, соответствующий режиму Ввод-вывод информации. Работа устройства в этом режиме продолжается до тех пор, пока на единичный вход триггера 40 вновь не поступит им5 пульс запуска режима Обработка информации.

Формула изобретения 1. Устройство для контроля случайных процессов с помехами, содержащее три

0 блока оперативной памяти, три сумматора, два блока деления, задатчик количества выборок, генератор тактовых импульсов и блок умножения, вход первого сомножителя которого соединен с выходом второго блока

5 деления, вход второго сомножителя - с выходом второго блока оперативной памяти, а выход - с первым информационным входом первого блока оперативной памяти, выход которого связан с информационным входом

0 второго сумматора, выход которого подключен к входу делимого первого блока деления, вход делителя которого соединен с выходом задатчика числа выборок, а выход - с информационными входами третьего

5 сумматора и третьего блока оперативной памяти, первый выход которого связан с входом делимого второго блока деления, вход делителя которого подключен к выходу третьего сумматора, информационный вход

0 второго блока оперативной памяти соединен с выходом первого сумматора, о т л и ч а ю щ е е с я тем, что, с целью повышения производительности и качества контроля за счет автоматического задания количества

5 циклов обработки информации о случайном процессе в зависимости от его информа- ционно-статистических характеристик, в устройство введены блок управления и блок анализа результатов контроля, выход которого соединен с входом остановки блока управления, а информационный вход - с выходом второго блока деления, вход задания знака произведения блока умножения связан со знаковым выходом первого блока оперативной памяти, второй информационный вход которого и информационный вход первого сумматора подключены к информационному входу устройства. выход генератора тактовых импульсов соединен с тактовым входом блока управления, второй выход третьего блока оперативной памяти служит информационным выходом устройства, адресные выходы блока управления соединены с адресными входами всех блоков оперативной памяти, а управляю- щие выходы - с управляющими входами всех блоков оперативной памяти, сумматоров, блоков деления, блока умножения и блока анализа результатов контроля, вход запуска блока управления является входом запуска устройства.

2. Устройство по п. 1,отличающе - е с я тем, что блок управления содержит триггер, два задатчика адресов микрокоманд, коммутатор, узел памяти микроко- манд, делитель частоты и три счетчика, выход первого счетчика соединен с адресным входом узла памяти микрокоманд, группа выходов которого соединена с управляющими выходами блока, а два выхода связаны с входом разрешения загрузки первого счетчика и с первым информационным входом коммутатора, второй и третий информационные входы которого подключены к выходам старших разрядов второго и третьего счетчиков, выходы коммутатора соединены со счетными входами второго и третьего счетчиков, выходы которых служат адресными выходами блока, управляющий

вход коммутатора, прямой вход запуска первого задатчика адресов микрокоманд и инверсный вход запуска второго задатчика адресов микрокоманд связаны с прямым выходом триггера, единичный и нулевой входы которого подключены соответственно к входам запуска и остановки блока, выходы задатчиков адресов микрокоманд соединены с установочными входами первого счетчика, счетный вход которого связан с выходом делителя частоты, вход которого связан с тактовым входом блока.

3.Устройство по п. отличающееся тем, что блок анализа результатов контроля содержит узел оперативной памяти и вычислительный узел, сумматор, узел вычитания, узел сравнения и задатчик предельного значения приращения энтропии, выход которого соединен с первым информационным входом узла сравнения, выход которого является выходом блока, а второй информа- ционный вход связан с выходом узла вычитания, вход уменьшаемого которого подключен к выходу узла оперативной памяти, информационным вход которого и вход вычитаемого узла вычитания соединены с выходом сумматора, информационный вход которого связан с выходом вычислительного узла, вход которого подключен к информационному входу блока, управляющие входы блока соединены с входами разрешения сумматора, узла вычитания и узла сравнения и с входами управления записью и считыванием узла оперативной памяти.

4.Устройство но п. 3, о т л и ч а ю щ е - е с я тем, что вычислительный узел выполнен в виде узла постоянной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля случайных процессов с помехами | 1988 |

|

SU1550535A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Устройство для деления | 1988 |

|

SU1522199A1 |

| Устройство для быстрого действительного преобразования Хартли-Фурье | 1986 |

|

SU1343424A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для прогнозирования времени восстановления сложного технического объекта | 1989 |

|

SU1661797A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

Изобретение относится к вычислительной технике, предназначенной для контроля за протеканием случайных процессов, смешанных с помехами. Устройство содержит три блока оперативной памяти, три сум- матора, два блока деления, задатчик количества выборок, генератор тактовых импульсов блок умножения, блок управления и блок анализа результатов контроля и обеспечивает повышение производительности и качества контроля за счет автомати- ческого задания количества циклов обработки информации о случайном процессе в зависимости от его информационно- статистических характеристик. 3 з п ф-лы, 6 ил

Фиг. 1

Фиг. 2

фиг.З

Режим, ввод-выдод информации.

выдача адреса дыборт {ds} на блоки 2 и 5 У Аврес1-й выборки У /1дрес j-u($idbp/ u )&fdpec m-u dt,/Sopfru

быдача адреса аттета{Ас на 5локи 2 с/ /J

).

Запись исходных значений Ц/Ъ) 6 блок 2 быдачо на сумматор 3

if

Запись результа/поб суммирования I Xj(Tt) 8 блок5 и обнуление аккумулятора в сумматоре J

Ht-M

-itIIФигА

. Режим „обработка информации Выдачи адреса отсчета Ас} ни 5локи 2 и 13

X Адрес 1-го отсчета ХГ Адрес 2-гд отсче/т7а X Адрес л-г$отсце/псг Х

выдача адреса ЗыВорки {As} на Влоки 2 и 5 X /- м-л

Этап 1 дыдача от с чет од XJ(TI) из блока 2 на сумма/яор 7

мЕ„ Лm tшЧ -М1 ji

Выдачи результатов суммирования, /у fa) из сумматора 705лохЗ

Запись результатов деления ( 6 блок 13, Ыачоихмасумматор%;

Обнуление аккумулятора Ј сумматоре 7

-ffКЯ:fftf Я(fОбнуление аккумулятора S сумматоре 14, fo/tfai/ff знсмем/и м# tf tf/t-f S узел 33 из сумматора Jf и t/j/ia J4 соот етстЯемно

Ж

дь/доча результата сравнения УЗ узла 37 на олох 24; Обнуление аккумулятора 6 сумматоре J/

а

-Uif{}-ffФиг.5

{кэih

jiL.

М-tfЛежим „ о5ра5отка информации продолжение)

Этап 2

Выдача результата суммирования. S и значений M{X{Ti} на 5лох f7 из сумматора М и блока fJ соо/ггЯетственно

Ж.

,(ЫЛIIМпча В блок 21 результатов суммирования Sj, значений Pi и (Ti) из блоков 5, Пи 2 соответственно

т тк м т . m4tj

Запись результатов произведения Xj (Т модисрицированнб/х значений) в 5мок 2 из блока 21

Г Г Пя П А А/; Л

Выдача значений PI 8 узел 9 из блока 17

Т „„Л«Jl

4tвыдача значений 1одгР{ из узла 9на сумматор 31

йП„„ Лff-Л.

Фиг.6

| Устройство для контроля случайных процессов с помехами | 1983 |

|

SU1141423A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля случайных процессов с помехами | 1988 |

|

SU1550535A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-15—Публикация

1989-12-22—Подача