Изобретение относится к вычислительной технике и может быть использовано в специализированных устройствах для обработки сейсмических, акустических, видеосигналов и других сигналов.

Целью изобретения является расширение функциональных возможностей за счет реализации функции z

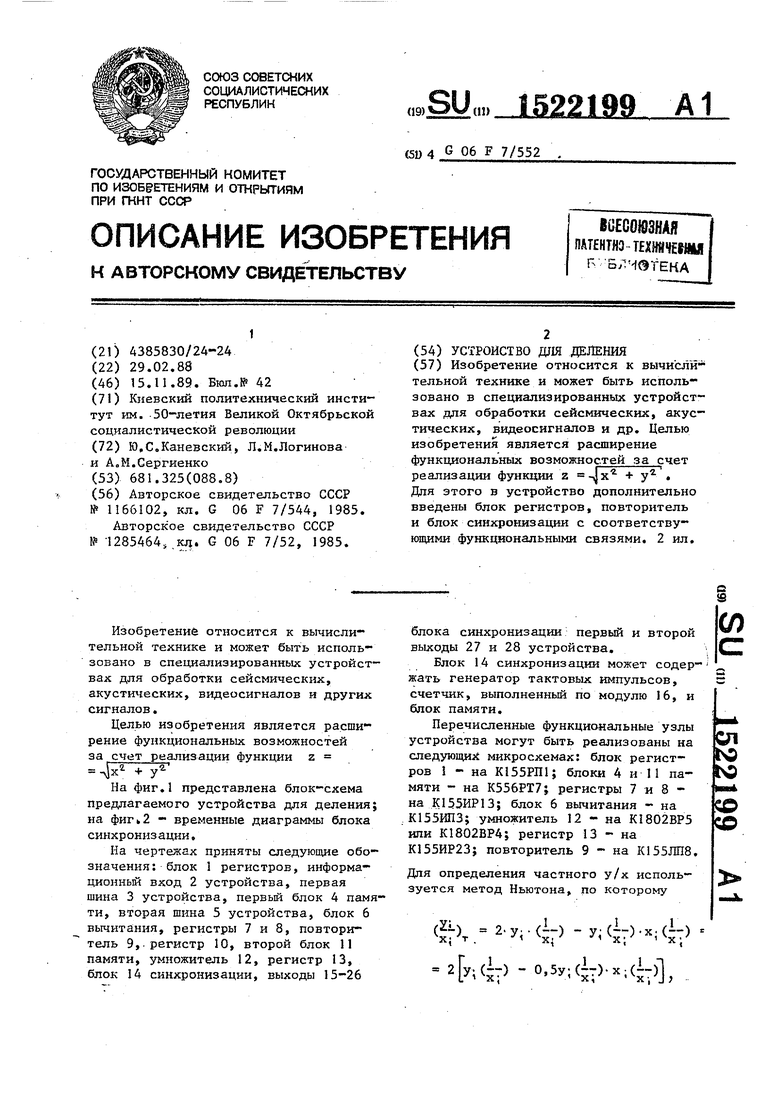

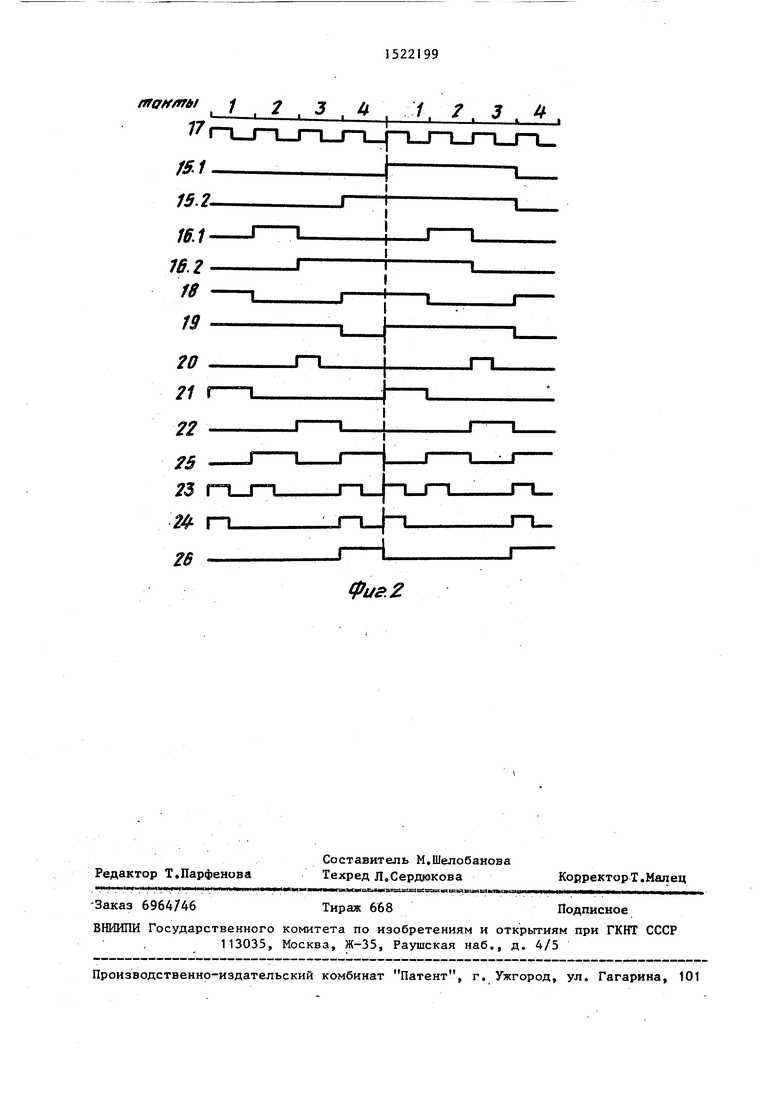

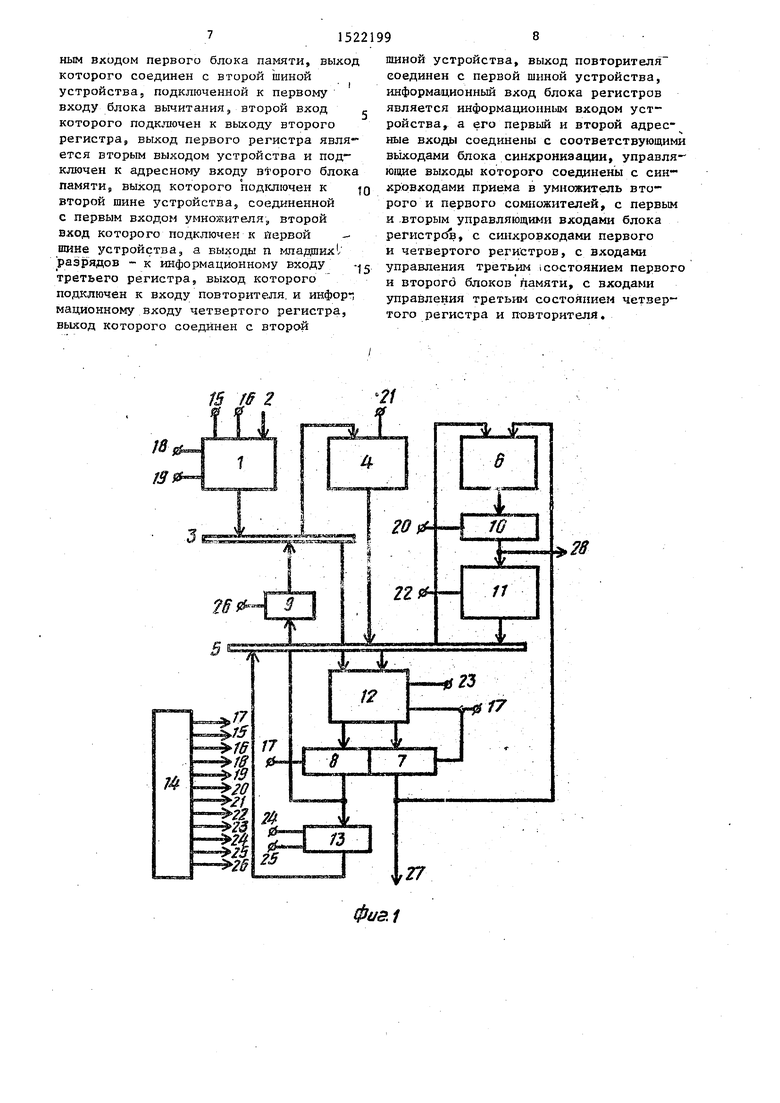

На фиг.1 представлена блок-схема предлагаемого устройства для деления; на - временные диаграммы блока синхронизации.

На чертежах приняты следующие обозначения: блок 1 регистров, информа- ционньй вход 2 устройства, первая шина 3 устройства, первьй блок 4 памяти, вторая шина 5 устройства, блок 6 вьгчита:ния, регистры 7 и 8, повторитель 9,.регистр 10, второй блок 11 памяти, умножитель 12, регистр 13, блок 14 синхронизации, выходы 15-26

блока синхронизации первый и второй выходы 27 и 28 устройства.

Блок 14 синхронизации может содержать генератор тактовых импульсов, счетчик, выполненный по модулю 16, и блок памяти.

Перечисленные функциональные узлы устройства могут быть реализованы на следующиг микросхемах: блок регистров 1 - на К155РП1; блоки 4 и 11 памяти - на К556РТ7; регистры 7 и 8 - на К155ИР13; блок 6 вычитания - на К155Ш13; умножитель 12 - на KI802BP5 ипи К1802ВР4; регистр 13 - на К155ИР23} повторитель 9 - на К155ЛП8.

Для определения частного у/х используется метод Ньютона, по которому

сл

с:

(i-), 2.y,.(i-)-y;(i-).x;(i-) ,(i-)-0,5y;(i-).x;(i-),

где (у/х)- точное значение У /Xj ;

входнь е отсчеты.

Предлагаемое устройство выполняет вычисление функции z дующим образом

+ у еле

4

х -ьу

с|Т

(при

.4

X. у)

Нахождение обратной величины 1/х

1 +

ф

выполняется табличным

способом. Таблицы этих функций зане сены соответственно в блоки. 4 и П 15 памяти

На вход блока 4 памяти, в котором хранится таблица значений 1/х, по ступают, например, 11 старших разрядов х; (что определяется емкостью блока 20 памяти) Тогда максимальному значению

х;

1 с учетом масштабирования соответствует значение

Х1.3(

-Л.Г U; J; 2 -ч „-11 25

Пусть в исходном состоянии адрес записи в блок 1 регистров установле в состояние 01. В блоке 1 регистров по адресу 00 записано первое значен входного отсчета X , а по адресу 10 предыдущее значение x., Адрес чте ния в исходном состоянии установлен в состояние 00.

В первом такте работы устройства на вход 2 поступает второе значение входного отсчета у , которое записы вается в блок 1 регистров по адресу

, а минимальному х . 2 .

значение -- I, Для получения пол- L Х-, J д,

норазрядного значения у;- 1/х и

х; 1/х; соответствующие значения xj QJ Одновременно происходит чтение

и У; подаются с выхода блока 1 регист

ров на вход второго сомножителя JTMHO

жителя 12 со сдвигом на ,3 разряда

влево, Тое, х; 2 и у; . Полу°

ченные на выходе умножителя результа-

значения xj, записанного по адресу По значению адреса х из блока 4 памяти считывается значение 1/х{. В этом же такте в регистр первого cof

множителя умножителя 12 принимается

ты имеют знача,щие .разряды только в младших разряда.,, так как при

Ч 9 - - Ь т -Поэтому результат принимается в регистр 8 с младших разрядов выхода. умножителя 12. ,-,

При вычислении z -и х + у чере

таблицу - + (-) Х; подается на вх

к/т ,

умножителя без сдвига, и результат в регистр 7 принимается со старших разрядов выхода умножителя 12

С целью упрощения описания работы устройства будем считать, что прием информации во все регистры осуществляется положительным перепадом синхр импульса, на первый и второй адресны входы блока 1 регистров поступают«соответственно адреса записи и чтения, первый и второй управляющие входы блока 1 регистров являются соответственно входом управления записью и вхдом управления чтением, причем запи

0

5

0

5

си и чтению соответствует единичное значение на этих входах, нулевое значение на входе управления чтением переводит выход блока 1 регистров в третье состояние; нулевое значение на входах управления третьим состоя- нием блоков 4 и 11 памяти, регистра 13 и повторителя 9 также переводит выходы в третье состояние, при этом может независимо происходить прием информации в регистры.

Рассмотрим работу устройства при вьиислении значений у; /х j и TJX + У; , Цикл работы устройства равен 4 тактам работы умножителя 12 (или 8 полутактам)

Пусть в исходном состоянии адрес записи в блок 1 регистров установлен в состояние 01. В блоке 1 регистров по адресу 00 записано первое значение входного отсчета X , а по адресу 10 - предыдущее значение x., Адрес чте- . ния в исходном состоянии установлен в состояние 00.

В первом такте работы устройства на вход 2 поступает второе значение входного отсчета у , которое записывается в блок 1 регистров по адресу

QJ Одновременно происходит чтение

значения xj, записанного по адресу 00. По значению адреса х из блока 4 памяти считывается значение 1/х{. В этом же такте в регистр первого cof

множителя умножителя 12 принимается

. ;. .- I значение Х с выхода регистра

JJC 1V i

13, а в регистр второго сомножителя - 2jiL

с выхода регистра 8. Одновре

менно в регистре 7 с выхода умножите- I ля 12 принимается зна чение х,

-11.4 (--J) , которое поступает на

X ,2

-выход 27 устройства. Для обеспечения Передачи соответствующей информации через шину 3 в первом такте повторитель 9 Устанавливается в третье состояние (нулевое значение на выходе 26 блока 14 синхрониз ации) Для пере дачи значения I/x, .считанного из блока 4 памяти; на первый вход умножителя 12 через шину 5, блок 11 памяти и регистр 13 устанавливается в ., третье состояние (выходы 22 и 25 блока 14 синхронизации), В этом же такте в регистр 13 принимается значение

J х;.

с выхода регистра 8.

515221

Во втором такте работы по адресу 01 считывается значение у из блока 1 регистров, а в регистры первого и второго co ffloжитeлeй умножителя 12. принимаются соответственно значения 1/х и x. считанные в-предыдущем такте. Повторитель 9 остается в третьем состоянии. Одновременно в регистр 7 принижается с выхода старших разря- ю

дов умножителя 12 значение JLbl.. dL::: V V

л,, X ,,

которое поступает на второй вход блока 6 вычитания. Значение у;,, /х ;, поступает с выхода регистра 13 на первый 15 вход блока 6 вычитания. При этом выходы блоков 4 и 11 памяти находятся в третьем состоянии (выходы 21 и 22 блот ка 14 синхронизации). Результат с выхода блока 6 вычитания20

о. У- - г . SiiJ-

х;,

х;(-1

х;.

поступает на вход регистра 10.

В третьем такте работы устройства 25 по адресу 10 из блока 1 регистров считывается значение х;, . В регистр второго сомножителя принимается значение у J с выхода блока 1 регистров, считанное в предыдущем такте. В регистре первогоЗО сомножителя остается в том такте без изменения значение l/x-, В регистр 8 принимается с выхода младших разрядов умножителя 12 значение х j1/х;. Повториуель 9 остается в третьем сое- 35 тоянии. В регистр 10 принимается полученное в предыдущем такте точное зна- чеиие

r2i:J - Yb-.SJjil

(

х;..

-),

х:.,

х,1 х;.,

5

/ 40

которое поступает затем на выход 28 устройства на адресный вход блока 11 памяти, откуда считывается срответст( . в третьX

ми. J

f

вующее значение , , || , X ,.,

ем такте регистр 13 и блок 4 памяти .. находится в третьем состоянии (выходы 25 и 21 блока 14 синхронизации).

В четвертом такте в регистр nepBoro сошюжителя умножителя 12 принимаетзиачение -л 1 +

I

ся значение -лП (---) , считанное Ч х;.,

в предыдущем такте из блока 11 памяти, В регистр второго сомножителя принимается значение х

1-1

регистров принимается значение

с выхода блока 1 Одновременно в регистр 8

Xi Jti

с выхода млад96

ших разрядов умножителя 12, В регистр 13 принимается значение х; 1/х с выхода регистра 8. В этом же такте в блок 1 регистров по адресу 10 записывается очередное значение входного отсчета х;, . Повторитель 9 выходит из третьего состояния и на его выход поступает значение х 1/х ; с регистра 8, которое в первом такте следующего цикла будет принято в регистр первого сомножителя умножителя 12, В этом же такте блок 1 регистров находится в третьем состоянии.

Со следующего, пятого такта цикл работы устройства повторяется, Исключение- составляют адреса чтения и записи блока 1 регистров. Если в первом цикле и во всех нечетных циклах у; записывается по адресу 01, а х- - 10, то во втором цикле и во всех четных циклах запись происходит в те же такты, но по другим адресам:

y;+( ° j i+2 ° Аналогичным образом чтение происходит в пер вом цикле (м во всех нечетных) по адресам: х; - 00; у - 01; х;., - . 10, а во втором цикле и во всех четных циклах: х j ц.,, - 10; у; - 11; х;- - 00.

Таким образом, через 7 тактов после поступления на вход отсчетов х; и У; на выходе регистра 10 появляется результат деления (у;/х;)., а через 8 тактов - на выходе регистра 7 значение

Я

+ У I

40

, 45

jg

Фо рмула из о бретения

Устройство для деления, содержащее первый и второй блоки памяти, с первого по четвертьй регистры, блок вычиг тания и умножитель, причем выход блока вычитания подключен к информационному входу первого регистра, выходы п старших разрядов умножителя соединены с информационным входом второго регистра, выход которого является первым выходом устройства, отличающее г с я тем, что, с целью расширения функциональных возможностей за счет реализации функции z ijx + , в него введены блок регистров, повторитель и блок синхронизации, причем выход блоки, регистров подключен к первой шине устройства, соединенной с адресным входом первого блока памяти, выход которого соединен с второй шиной устройства, подключенной к первому входу блока вычитания, второй вход которого подк,шочен к выходу второго регистра, выход первого регистра является вторым выходом устройства и подключен к адресному входу второго блока памяти, выход которого подключен к JQ второй шине устройства, соединенной с первым входом умножителя, второй вход которого подключен к йервой - шине устройства, а выходы п младших ; разрядов - к информационному входу -jc третьего регистра, выход которого подключен к входу повторителя, и инфор- маднонному входу четвертого регистра, выход которого соединен с второй

шиной устройства, выход повторителя соединен с первой шиной устройства, информационный вход блока регистров является информационным входом уст ройства, а его первый и второй адресные входы соединены с соответстБующимн выходами блока синхронизации, управля-- ющие выходы которого соединены с син хровходами приема в умножитель второго и первого сомножителей, с первым и .вторым управляющими входами блока регистрс5в, с синхровходами первого и четвертого регистров, с входами управления третьим (состоянием первого и второго блоков памяти, с входами управления третьим состоянием четвертого регистра и повторителя,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1986 |

|

SU1387015A1 |

| Цифровой фильтр | 1988 |

|

SU1555826A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Устройство для вычисления функции арктангенса | 1989 |

|

SU1661760A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных устройствах для обработки сейсмических, акустических, видеосигналов идр. Целью изобретения является расширение функциональных возможностей за счет реализации функции Z=√X2+Y2. Для этого в устройство дополнительно введены блок регистров, повторитель и блок синхронизации с соответствующими функциональными связями. 2 ил.

/5 /6 2

21

1

jm

тт

±

28

11

ф1/а1

| Устройство для вычисления функции @ | 1984 |

|

SU1166102A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1985 |

|

SU1285464A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-29—Подача