(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1985 |

|

SU1287154A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1062701A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для отладки программ | 1988 |

|

SU1661771A1 |

Изобретение относится к вычислительной технике и может быть использовано в ВС с микропрограммным управлением. Цель изобретения - уменьшение объема оборудования за счет сокращения объема блока памяти микрокоманд, уменьшения разрядности регистра адреса, сумматора приращения и дешифратора. Устройство микропрограммного управления содержит первый мультиплексор 1, регистр 2 адреса, блок 3 памяти микрокоманд, блок 4 оперативной памяти, сумматор 5 приращения, дешифратор 6, триггер 7, реверсивный счетчик 8, группу элементов И 9 и второй мультиплексор 10. Новым в устройстве микропрограммного управления является наличие второго мультиплексора и изменение связей между блоками. 2 ил.

СП

ОЭ Оэ

с$

00

31

Изобретение относится к вычисли- Уепьной технике и может быть использовано в микропроцессорных системах С микропрограммным управлением.

Цель изобретения - уменьшение Объема оборудования.

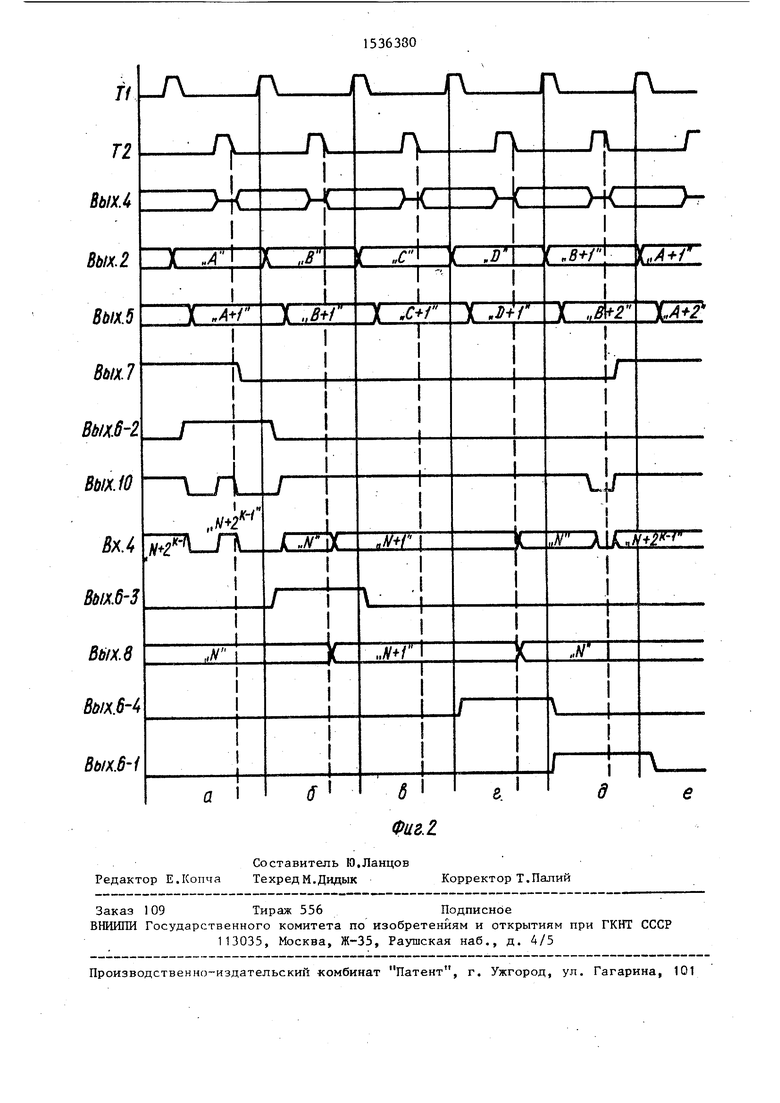

На фиг. 1 представлена функциональная схема устройства; на фиг. 2- йоследовательность синхроимпульсов, Необходимая для синхронизации устройства.

Устройство микропрограммного управления содержит (фиг. 1) мульти- рлексор , регистр 2 адреса, блок 3 Памяти микрокоманд, блок 4 оператив- Ной памяти, сумматор 5 приращения, дешифратор 6, триггер 7, реверсивный четчик 8, группу элементов И 9 и Мультиплексор 10.

Устройство работает следующим образом.

Предполагается, что переход из Главной программы в рабочую осуществляется поЈле завершения некоторых Операций, связанных с обращением к Подпрограммам в главной программе. |При этом на момент перехода из главной программы в рабочую число микро- Команд в главной программе Переход К подпрограмме равно числу микрокоманд Возврат из подпрограммы. Каждая микрокоманда перехода занимает в блоке 3 памяти микрокоманд одно слово и содержит код микрооперации и адрес первой микрокоманды подпрограммы

Синхронизация работы устройства осуществляется двумя синхропоследо- вательностями TJ и Т2 (фиг. 2), По фронту Т1 производится запись в регистр 2 адреса очередной микрокоманды. На протяжении положительного импульса Т2 блок 4 находится в режиме записи и переписьюает содержимое регистра 2, увеличенное на единицу. Все остальное время блок 4 находится в режиме считывания.

Увеличение или уменьшение содержимого реверсивного счетчика 8, а также установка в состо н е логической 1 или логического О триггера 7 осуществляется спадом импульса Т2.

Рассмотрим работу устройства при переходе из рабочей программы в главную. Допустим, выполняется программа рабочей программы N-ro уровня вложек ности. По адресу А этой подпрограммы находится микрокоманда Переход в

1

гла вную программу. По фронту TI код

0

5

0

5

0

5

0

5

0

адреса А заносится в регистр 2 и с некоторой задержкой на выходе блока 3 памяти микрокоманд появится код операции микрркоманды Переход в главную программу. На вход дешифратора 6 поступает кодовая комбинация, при которой на втором выходе дешифратора 6 на один такт появляется сигнал логической 1, разрешающий установку триггера 7 в состояние логического О в конце цикла.

На вход блока 4 оперативной памяти поступает из регистра 2 через сумматор 5 приращения код адреса А+1 следующей микрокоманды подпрограммы рабочей программы. По положительному сигналу Т2 он записывается в (N+2 )-ю ячейку блока 4 оперативной памяти, где К - число разрядов кода адреса блока оперативной памяти, поскольку с триггера 7 на старший разряд адресных входов блока 4 оперативной памяти поступает сигнал логической 1, а содержимое реверсивного счетчика 8 равно N и на вторые входы элементов И 9 группы поступает сигнал логической J (фиг. 2а). I

В начале следующего такта (фиг.26) считывания содержимого блока 4 оперативной памяти триггер 7 находится в состоянии логического О, а на второй информационный вход второго мультиплексора 10 поступает сигнал логической ) с дешифратора 6. На управляющий вход второго мультиплексора 10 поступает сигнал нулевого уровня синхросигнала 12, Поэтому в момент времени, определяемый дизъюнкцией этих сигналов, на выходе второго мультиплексора JO появляется сигнал логического О, запрещающий поступление содержимого реверсивного счетчика 8 через группу элементов И 9 на адресные входы блока 4 оперативной памяти. При этом на старший разряд адресных входов блока 4 оперативной памяти поступает сигнал логического О с триггера 7, а на остальные разряды - сигнал логического О с группы элементов И 9. Таким образом, в следующем такте из блока 4

55

оперативной памяти считывается код адреса микрокомалды, хранимый в ячейке блока 4 оперативной памяти с нулевым адресом. Пусть этот код адреса возврата в главную программу равен В.

По фронту Т1 этот код заносится в регистр 2 адреса и начинается выполнение действий в главной программе. Допустим, в главной программе по ад- . ресу В (фиг.2б) находится микрокоманда Переход к подпрограмме, т.е. в слове этой микрокоманды содержится код микрооперации и адрес первой микрокоманды подпрограммы. Пусть адрес первой микрокоманды подпрограммы равен С. При этом содержимое реверсивного счетчика 8 равно N, а триггер 7 обнулен, что соответствует выбору в блоке 4 оперативной памяти ячейки с адресом N.

Сумматор 5 приращения производит приращение содержимого регистра 2, и на информационный вход блока 4 оперативной памяти поступает код В+1. Во время положительного импульса Т2 этот код записывается в ячейку 4 оперативной памяти с номером N, что соответствует запоминанию адреса возврата (фиг. 26). С выхода поля типа микроопераций блока 3 памяти микрокоманд на вход дешифратора 6 поступает комбинация, соответствующая решению приращения реверсивного счетчика 8 на единицу. По спаду Т2 содержимое счетчика 8 становится равным N + 1.

В этом же такте с появлением на выходе блока 3 памяти микрокоманд микрокоманды Переход к подпрограмме мультиплексор 1 переключает вход регистра 2 с выхода блока 4 оперативной памяти на выход поля адреса блока 3 памяти микрокоманд. Тогда в следующем цикле в регистр 2 по фронту Т 1 будет загружен код С , а в (N+l)-io ячейку блока 4 оперативной памяти запишется код С+1 и произойдет обратное переключение мультиплексора 1 (фиг. 2в).

Таким образом, за один цикл работы устройства произошло запоминание адреса возврата в ячейке с номером И блока 4 оперативной памяти и переход к первой микрокоманде подпрограммы главной программы. Переход из этой подпрограммы в следующую реализуется аналогично. При этом адреса возврата будут храниться в ячейках блока 4 оперативной памяти с адресами N и N+1, а содержимое реверсивного счетчика 8 станет равным N+2. Число уровней вложенности подпрограмм ограничивается лишь длиной реверсивного счет0

5

0

5

0

5

0

5

0

5

чика 8 и числом ячеек блока 4 оперативной памяти.

Возврат из подпрограммы главной программы, так же, как и в рабочей программе, происходит по микрокоманде Возврат из подпрограммы, являющейся последней микрокомандой подпрограммы.

Допустим., обрабатывается подпрограмма первого уровня вложенности, а- микрокоманда Возврат из подпрограммы находится по адресу D. По фронту Т1 (фиг. 2г) код адреса микрокоманды Возврат из подпрограммы D заносится в регистр 2, и на вход дешифратора 6 поступает кодовая комбинация, соот- ветствующая разрешению уменьшения содержимого реверсивного счетчика 8 на единицу. Тогда в начале следующего такта (фиг. 2д) из блока 4 оперативной памяти будет считываться содержимое ячейки с адресом N, в которой хранится адрес возврата, для нашего примера равный В+1, который по фронту Т1 запишется в регистр 2. Далее коды адреса, пройдя через сумматор 5 приращения, будут записываться в ячейку блока 4 оперативной памяти под номером N.

После выполнения действий в главной программе можно вернуться в подпрограмму рабочей программы, из которой был осуществлен переход в главную программу. Это происходит по микрокоманде Возврат в программу, которая, предположим, находится по адресу В+1, При выполнении этой команды дешифратор 6 вырабатывает на первом выходе сигнал, разрешающий установку триггера 7 в состояние логической 1. При этом на первый информационный вход второго мультиплексора 10 поступает с дешифратора 6 сигнал логической , на управляющий вход второго мультиплексора 10 - положительный сигнал Т2, а на выходе второго мультиплексора JO появится сигнал логического 0й, поэтому в момент записи в блок 4 оперативной памяти на адрес-1 ные входы блока 4 через группы элементов И 9 будут поданы сигналы логического О. Триггер 7 также до конца цикла находится в состоянии логического О. Поэтому запись последнего адреса главной программы, увеличенного на единицу В+2, произойдет в ячейку блока 4 оперативной памяти с адресом 0 (фиг. 2д). В конце цикла

По спаду Т2 триггер 7 устанавливается в состояние логической 1 и считывание следующего адреса микрокоманды из блока 4 оперативной памяти (фиг. 2е) будет осуществляться из ячейки с номером , поскольку |код в реверсивном счетчике 8 сохра- ил свое значение, равное N, а на старший разряд входа адреса блока 4 шеративной памяти поступает логи- 1еская 1 с триггера 7. В этой ячейке хранится код адреса, для данного гримера равный А+1„ Далее этот код адреса по фронту Т1 заносится в ре- гтистр 2 и выполняются операции в рабочей программе.

- 1

Переход на подпрограммы и возвра из них в рабочей программе осущест- вляется точно так же, как и в глав- ой программе, с той лишь разницей, что адреса возврата записываются в ячейки блока 4 оперативной памяти с такими номерами, в которых старший разряд адреса ячейки равен логической

Формула изобретения

Устройство микропрограммного управления, содержащее первый мультиплексор, регистр адреса, блок, памяти микрокоманд, блок оперативной памяти, сумматор приращения, дешифратор, триггер, реверсивный счетчик, группу элементов И, причем первый информационный вход первого мультиплексора соединен с выходом поля адреса блока памяти микрокоманд, второй информаци- онный вход первого мультиплексора соединен с выходом блока оперативной памяти, выход первого мультиплексора соединен с информационным входом ре0

5

0 5

0

Q

гистра адреса, выход которого соединен с адресным вкодом блока памяти микрокоманд, а также с входом сумматора приращения, выход которого подключен к информационному входу блока оперативной памяти, выход поля микроопераций блока памяти микрокоманд является выходом устройства, выход поля типа микрокоманды блока памяти микрокоманд соединен с входом дешифратора, первый и второй выходы дешиЛратора соединены соответственно с входами установки в 1 и в О триггера, третий и четвертый выходы дешифратора соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, выходы которого соединены с первыми входами элементов И группы, выходы которых соединены с адресными входами младших разрядов блока оперативной памяти, первый тактовый вход устройства подключен к синхровходу регистра адреса, второй тактовый вход устройства подключен к синхровходам триггера и реверсивного счетчика, а также к входу чтения-записи блока оперативной памяти, отличающееся тем, что, с целью уменьшения объема оборудования, оно содержит второй мультиплексор, причем выход триггера соединен с адресным входом старшего разряда блока оперативной памяти, управляющий вход первого мультиплексора соединен с третьим выходом дешифратора, первый и второй выходы цешифра гора соединены соответственно с первым И вторым информационными входами второго мультиплексора, управляющий вход которого соединен с вторым тактовым входом устройства, выход второ1о мультиплексора соединен с вторыми входами элементов И группы.

7/

П Вых.4

Вых. 2

Вых.5

Вш.7

Вых.6-2

Вых. 10

to. 4

Вб/х.6-3

Вых. В Вш.6-4

Вых.6-1

Редактор Е.Копча

Составитель Ю.Ланцов Техред М.Дидык

Фиг.2.

Корректор Т.Палий

| Устройство для управления обращением к стандартным подпрограммам | 1974 |

|

SU544965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-25—Подача