Изобретение относится к вычислительной технике, а именно к устройствам для отладки программ, и может быть использовано в многомашинных вычислительных, комплексах (ВК) для автоматической отладки взаимодействующих, параллельно выполняемых в реальном масштабе времени (РВ) программ.

Целью изобретения является расширение области применения устройства для отладки программ за счет обеспечения его работоспособности при отладке произвольного числа взаимодействующих параллельно выполняемых в реальном масштабе времени программ на многомашинных вычислительных комплексах.

Сущность изобретения состоит в том, что новая совокупность конструктивных

признаков позволяет расширить область применения устройства для отладки программ за счет обеспечения возможности совместной отладки взаимодействующих параллельно выполняемых в реальном времени программ на многомашинных ВК и недопущения ситуаций взаимной блокиров ки (тупика) нескольких ЭВМ ВК в режиме совместной отладки программ.

Тупиковая ситуация может возникнуть при отладке программ на многомашинном ВК в том случае, если часть работ по обеспечению отладки должна производиться одной из ЭВМ ВК или внешней инструментальной ЭВМ (ПЭВМ), в модельном (псевдо- реальном) масштабе времени. Эти инструментальные операции не должны приводить к рассинхронизации отлаживавvl

-N ho

00

ho «о

мых программ, поэтому, все процессы по отладке программ, которые могут выполняться на фоне инструментальных операций, должны быть остановлены на время выполнения этих операций. В частности, при выполнении инструментальных операций одной из ЭВМ должны быть остановлены остальные ЭВМ (полностью блокированы элементы реального времени во всех ЭВМ В К и процессоры ЭВМ ВК, за исключением выполняющей инструментальный такт).

Таким образом, при совместной отладке нескольких взаимодействующих параллельно выполняемых программ, предназначенных для последующей работы в реальном масштабе времени, на многомашинном ВК, необходимо: обеспечить синхронную отладку программ в реальном масштабе времени; недопустить возникновение тупиковых ситуаций в процессе отладки программ на многомашинных ВК.

Отладка программ на каждой ЭВМ В К производится в течение рабочего такта, длительность которого определяется логической завершенностью программы, или потребностью в дополнительных данных для отлаживаемых программ, а также необходимостью выдачи данных во внешнюю (инструментальную) ЭВМ для анализа, чем обуславливается асинхронность их выполнения по отношению к рабочим тактам других ЭВМ ВК.

Таким образом, рабочий такт по отладке программы на любой из ЭВМ ВК может быть прерван, на время выполнения вспомогательных операций (инструментальный такт), по сигналу Конец рабочего такта, выдаваемого любой из ЭВМ ВК. После выдачи указанного сигнала все ЭВМ блокируются, затем осуществляется выбор той ЭВМ, из совокупности требующих выполнения инструментальных операций, которая .имеет максимальный приоритет, т.е. ЭВМ с минимальным номером. После этого на процессор выбранной ЭВМ разрешается выдача тактовой сетки для выполнения инструментального такта. По окончании инструментального такта (сигнал Конец инструментального такта) производится полная блокировка ЭВМ, отработавшей инструментальный такт, и снова, при наличии запросов на выполнение инструментальных тактов, производится приоритетный выбор одной из требующих выполнения инструментальных операций ЭВМ ВК. После завершения инструментальных тактов всеми ЭВМ ВК, которым они были необходимы, по очередному сигналу Конец инструментального такта, (начало рабочего такта) синхронно для всех ЭВМ ВК разрешается

разблокировка цепей выработки последовательностей для синхронизации процессов и элементов реального времени.

Таким образом обеспечивается совместная отладка взаимодействующих параллельно выполняемых программ в псевдореальном масштабе времени, предназначенных, в последующем, для работы в масшабе реального времени, на многомашинных ВК.

Ввиду того, что рабочие такты, выполняемые ЭВМ ВК, асинхроны, возможны ситуации взаимной блокировки ЭВМ. При возникновении такой ситуации отладка программ становится невозможной. Поэтому с применением предлагаемого устройства для отладки программ такие ситуации допускаются за счет синхронного останова всех ЭВМ ВК и упорядоченного обслуживания

выдавших запрос на выполнение инструментальных операций ЭВМ ВК, что обеспечивает автоматизацию процесса отладки.

Принцип действия устройства основан на реализации решения задач, перечисленных выше. При этом триггеры режима и триггеры управления выполняют функции по управлению процессом совместной отладки программ на ЭВМ ВК (определяют режимы рабочего, инструментального тактов или полной блокировки).

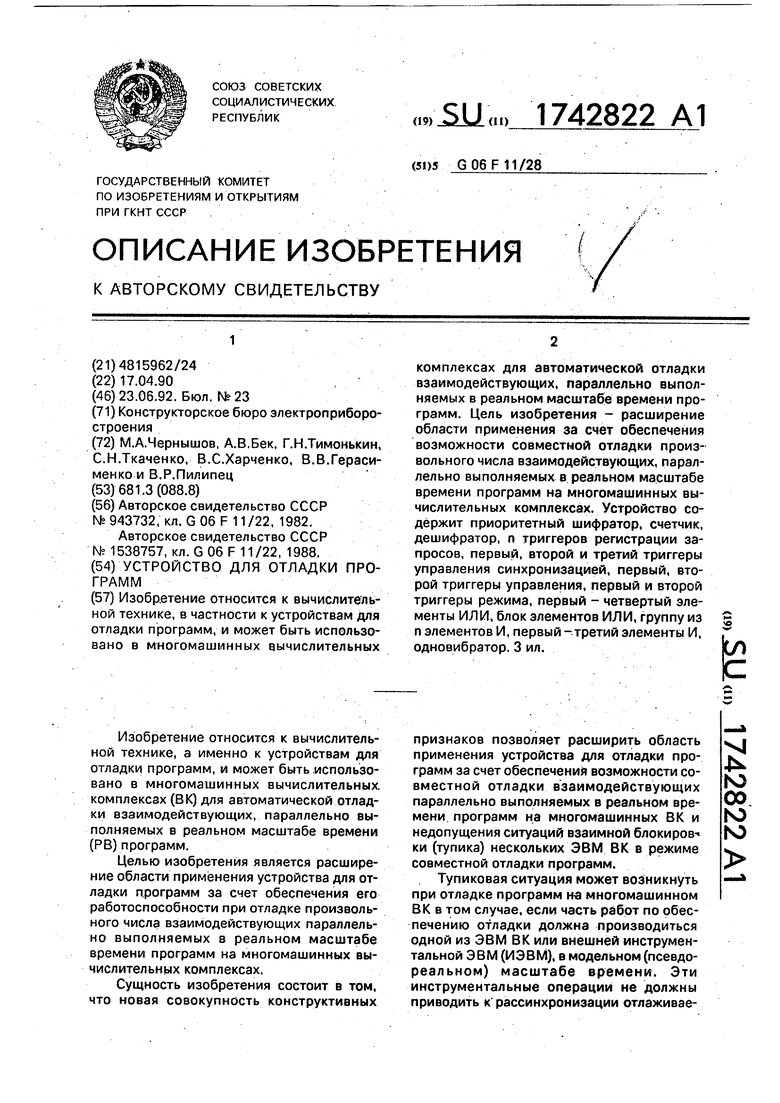

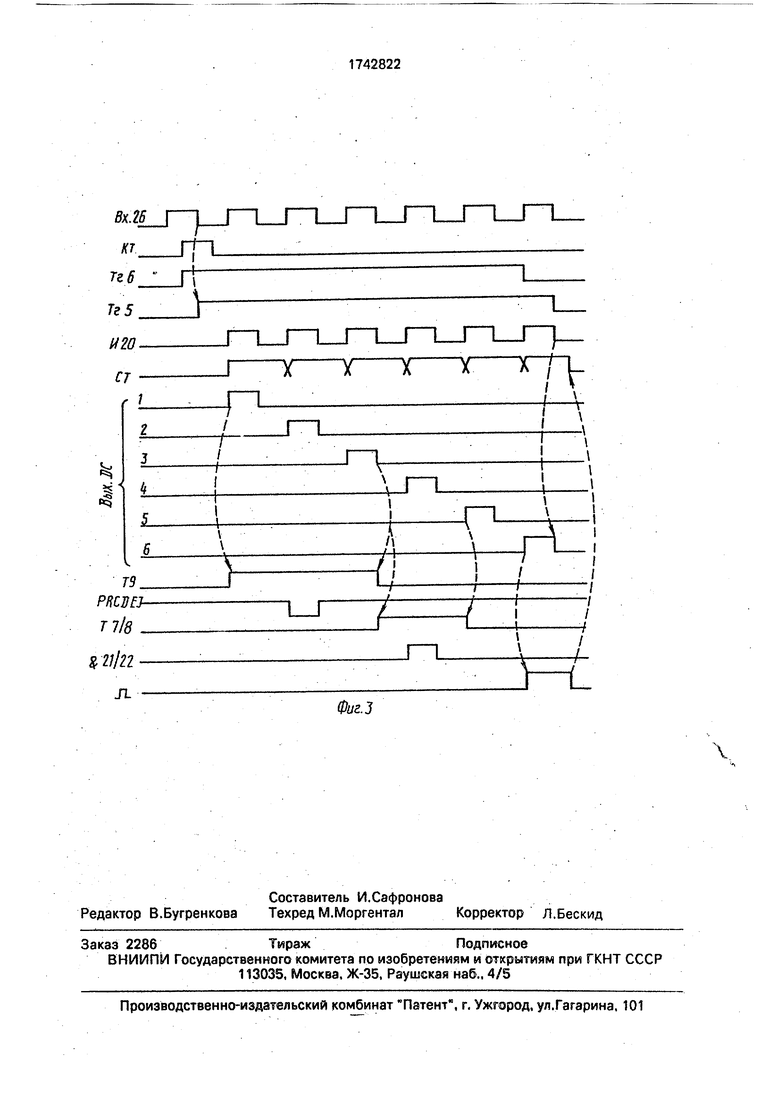

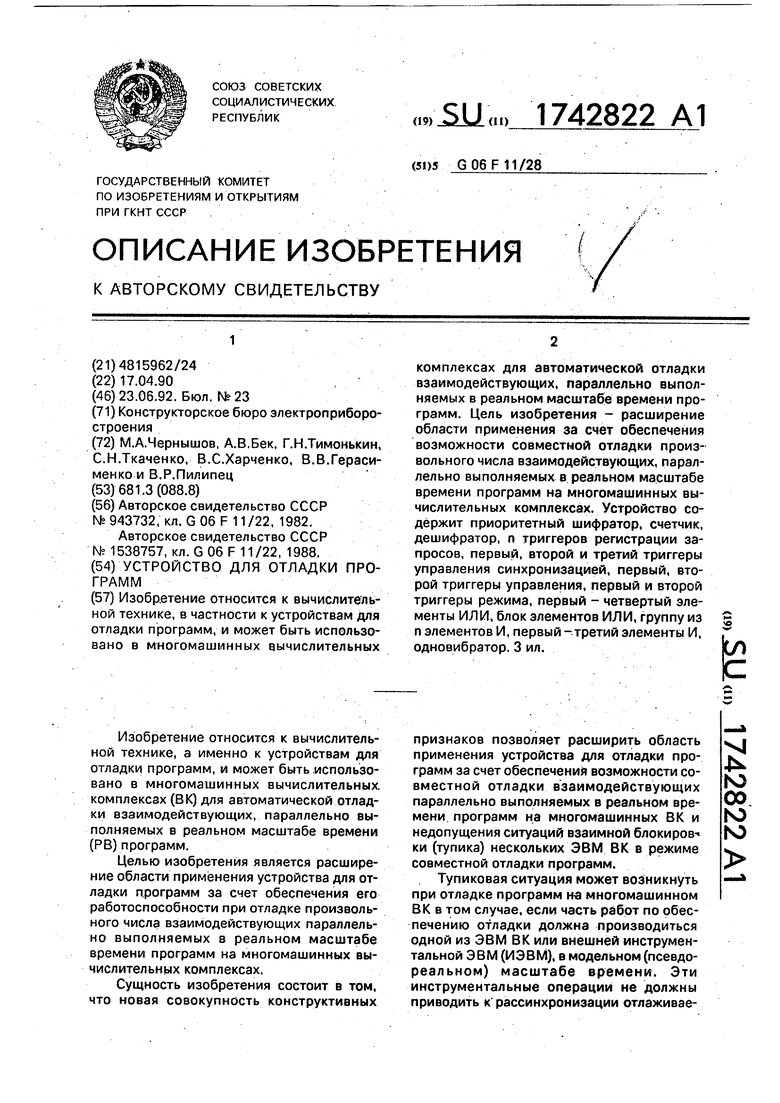

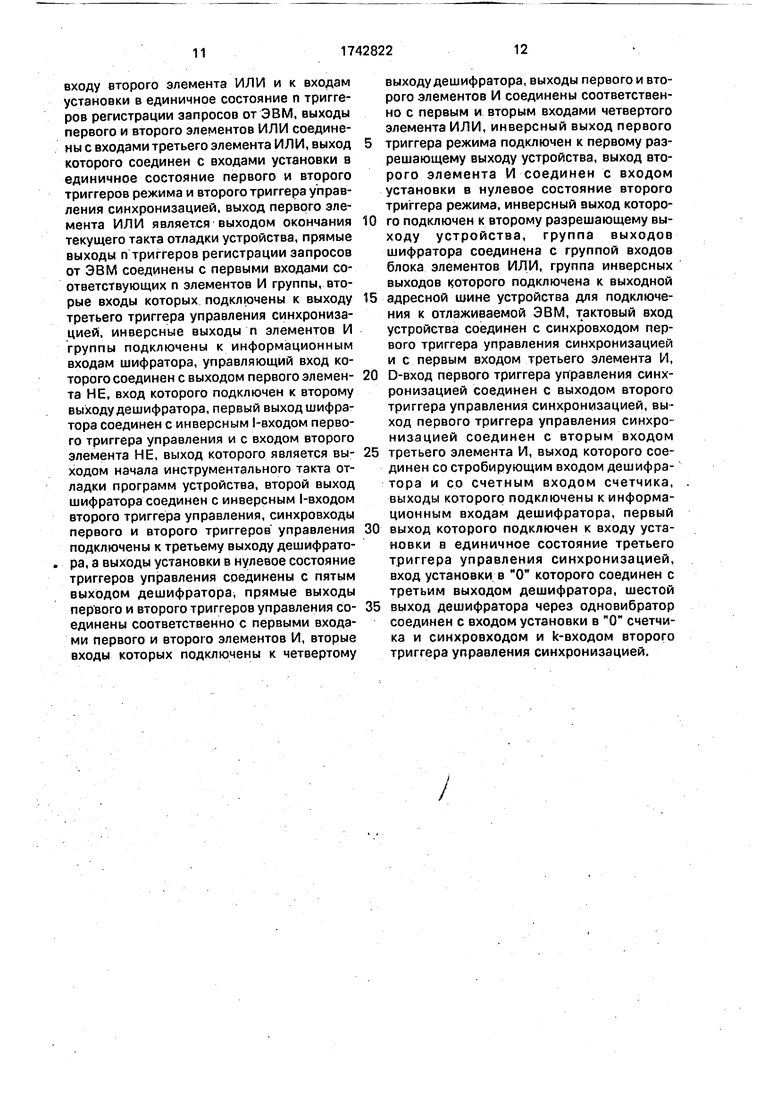

На фиг.1 представлена функциональная

схема устройству для отладки программ, а пример схемы его сопряжения с многомашинным ВК и ИЭВМ; на фиг.2 и 3 - временные диаграммы работы устройства/

Устройство для отладки программ содержит шифратор 1, счетчик 2, дешифратор 3, п триггеров 4.1-4.П регистрациийапросов от ЭВМ, триггеры управления сивхронизацией 5, 6, управления 7, 8 и управления синхронизацией 9, первый 10 и второй 11 триггеры режима, элементы ИЛИ 12-15, первый 16и второй 17элементыНЕ,блок18 элементов ИЛИ, группу из п элементов И

19.1-19.п, элементы И 20-22, одновибратор 23, шины 24 и 25 управления, тактовый вход 26, выход 27 окончания текущего такта отладки программ, выход 28 начала инструментального такта отладки программ,

первый 29 и второй 30 разрешающие выходы, выходную адресную шину 31.

Рассмотрим назначение элементов предлагаемого устройства для отладки про- грамм (фиг.1).

Шифратор 1 предназначен для преобразования кода, содержащего информацию о запросах от ЭВМ ВК на выполнение инструментальных операций, в инверсный код, задающий адрес ЭВМ, которая выбирается

(в соответствии с установленным приоритетом) для удовлетворения своего запроса.

Счетчик 2, дешифратор 3, первый 5, второй 6 и третий 9 триггеры управления синхронизацией, третий элемент И 20, первый элемент НЕ 16 и одновибратор 23 предназначены для выработки серии из шести импульсов, синхронизирующих работу элементов устройства для отладки программ в процессе обработки одного запроса, поступившего от ЭВМ ВК.

Триггеры 4.1-4.П регистрации запросов предназначены для приема, хранения и изменения информации о запросах от ЭВМ ВК на выполнение инструментальных тактов.

Триггеры 7 и 8 управления предназначены для кратковременного хранения сигналов с выходов GS и ЕО шифратора 1 соответственно.

Триггеры 10 и 11 режима предназначены для формирования на разрешающих выходах 29 и 30 устройства сигналов, задающих режимы работы ЭВМ ВК.

Элементы ИЛИ 12-14 предназначены для приема сигналов Конец инструментального такта и Конец рабочего такта соответственно с входных шин 24 и 25 управления и выработки в зависимости от комбинации поступивших: двух сигналов Конец текущего инструментального такта и Конеч такта, или одного только последнего на выходе элемента ИЛИ 14.

Элемент НЕ 17 предназначен для формирования путем инвертирования на выходе 28 устройства сигнала Начало инструментального такта, поступающего с первого выхода шифратора-1.

Блок 18 элементов ИЛИ предназначен для инвертирования разрядов кода, поступающего с группы выходов А.1-А.ГТ1 шифратора 1, с целью выдачи на выходную адресную шину 31 устройства адреса ЭВМ, которая выбирается для выполнения инструментального такта.

Элементы И 19.1-19.п предназначены для синхронной передачи на выходы а.О- а.п-1 шифратора 1 информации, хранящейся в триггерах 4.1-4.П регистрации запросов.

Элементы И 21,22 и ИЛ И 15 предназначены для выработки сигналов, разблокирующих триггеры 10 и 11 режима.

Входные шины 24 и 25 управления предназначены для приема сигналов-запросов от ЭВМ на выполнение инструмен- или рабочего тактов. Тактовый вход 26 устройства предназначен для приема тактовых сигналов от задающего генератора.

Выходы 27 и 28 предназначены для выдачи в инструментальную ЭВМ сигналов соответственно об окончании текущего и начале инструментального такта отладки 5 программ.

Разрешающие выходы 29 и 30 предназначены для передачи к ЭВМ сигналов, разрешающих выработку синхропоследовательностей, для процессоров и элементов реального вре0 мениЭВМ.

Выходная адресная шина 31 устройства предназначена для передачи к ИЭВМ и ЭВМ ВК адреса той ЭВМ, которая выбрана устройством для выполнения инструмен5 тального такта.

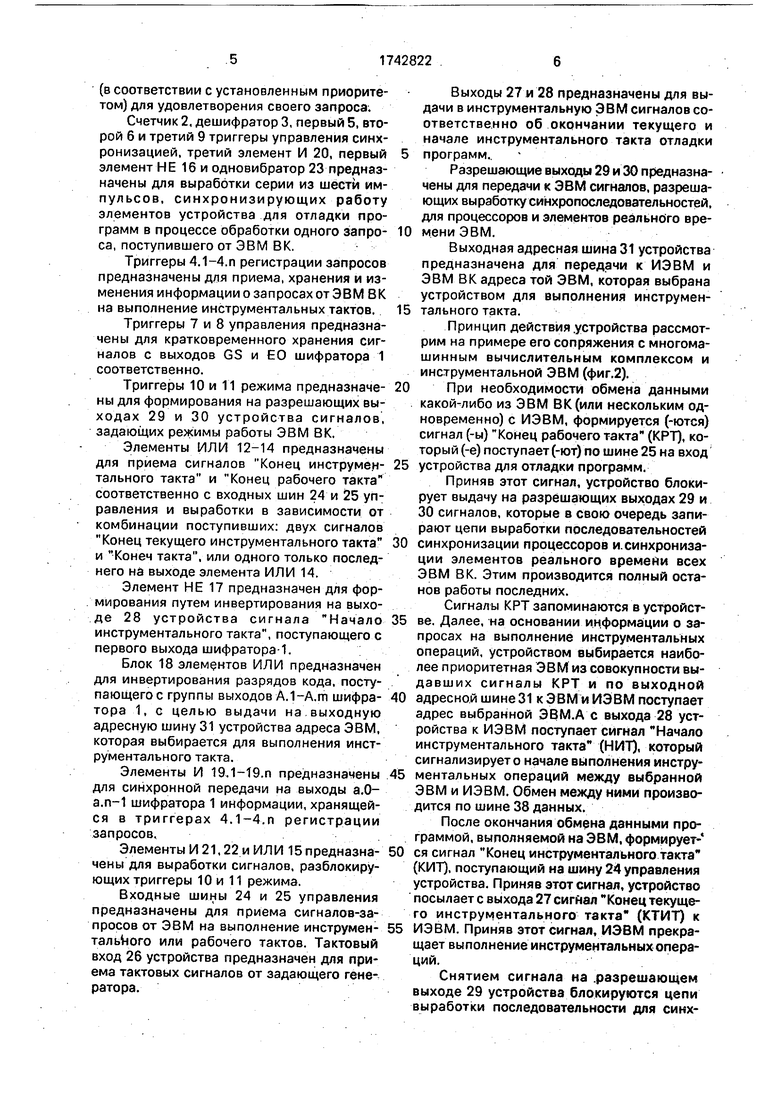

Принцип действия устройства рассмотрим на примере его сопряжения с многомашинным вычислительным комплексом и инструментальной ЭВМ (фиг.2).

0 При необходимости обмена данными какой-либо из ЭВМ В К (ил и нескольким одновременно) с ИЭВМ, формируется (-ются) сигнал (-ы) Конец рабочего такта (КРТ), который (-е) поступает (-ют) по шине 25 на вход

5 устройства для отладки программ.

Приняв этот сигнал, устройство блокирует выдачу на разрешающих выходах 29 и 30 сигналов, которые в свою очередь запирают цепи выработки последовательностей

0 синхронизации процессоров и синхронизации элементов реального времени всех ЭВМ В К. Этим производится полный останов работы последних.

Сигналы КРТ запоминаются вустройст5 ве. Далее, на основании информации о запросах на выполнение инструментальных операций, устройством выбирается наиболее приоритетная ЭВМ из совокупности вы- давших сигналы КРТ и по выходной

0 адресной шине 31 к ЭВМ и ИЭВМ поступает адрес выбранной ЭВМ.А с выхода 28 устройства к ИЭВМ поступает сигнал Начало инструментального такта (НИТ), который сигнализирует о начале выполнения инстру5 ментальных операций между выбранной ЭВМ и ИЭВМ, Обмен между ними производится по шине 38 данных.

После окончания обмена данными программой, выполняемой на ЭВМ, формирует0 ся сигнал Конец инструментального такта (КИТ), поступающий на шину 24 управления устройства. Приняв этот сигнал, устройство посылает с выхода 27 сигнал Конец текущего инструментального такта (КТИТ) к

5 ИЭВМ. Приняв этот сигнал, ИЭВМ прекращает выполнение инструментальных операций.

Снятием сигнала на .разрешающем выходе 29 устройства блокируются цепи выработки последовательности для синхронизации процессора ЭВМ, выполнившей инструментальный такт.

После этого в устройстве начинается новый цикл обработки запросов на выполнение инструментальных операций. Работа устройства при этом синхронизируется последовательностью импульсов с опорного генератора ПЭВМ, поступающей на тактовый вход 26 устройства.

В случае, когда устройство определило, что запросы от ЭВМ на выполнение инструментальных тактов отсутствуют, то на выходной адресной шине 31 формируется код адреса, содержащий все нули, а на разрешающих выходах 29 и 30 устройства формируются сигналы разблокировки цепей выработки последовательностей синхронизации процессоров и элементов реального времени всех ЭВМ. В данном случае возобновляется выполнение рабочего такта по отладке программ, прерванного на время выполнения инструментальных операций.

Таким образом, для обеспечения отладки программ в режиме РВ устройством, при выполнении инструментального такта какой-либо из ЭВМ, разблокируются цепи выработки последовательностей синхронизации только процессора выбранной ЭВМ, работа процессоров всех остальных ЭВМ заблокирована.

Выработка последовательностей синхронизации элементов реального времени заблокирована для всех ЭВМ, в том числе и для выполняющей инструментальные операции.

Возможная ситуация взаимной блокировки двух или нескольких ЭВМ, т.е. возникновения тупиковой ситуации (описана выше), не допускается следующим порядком действия устройства: при поступлении запросов в устройство, блокируется работа всех ЭВМ. Затем выбирается одна ЭВМ из совокупности выдавших запросы. Соответ- ствующий сигнал с выхода устройства разблокирует работу процессора этой ЭВМ. Выполняется инструментальный такт, после чего снимается запрос от этой ЭВМ и ее процессор блокируется. Выполняется обслуживание запроса следующей ЭВМ по приоритету.

Когда все запросы от ЭВМ ВК выполнены, сигналами с соответствующих выходов устройства разблокируются процессоры и элементы РВ всех ЭВМ. Работа комплекса по отладке программ в РВ может быть продолжена.

Устройство для отладки программ работает следующим образом.

Все элементы памяти в исходном положении находятся в нулевом состоянии (цепи

начальной установки на чертеже условно не показаны).

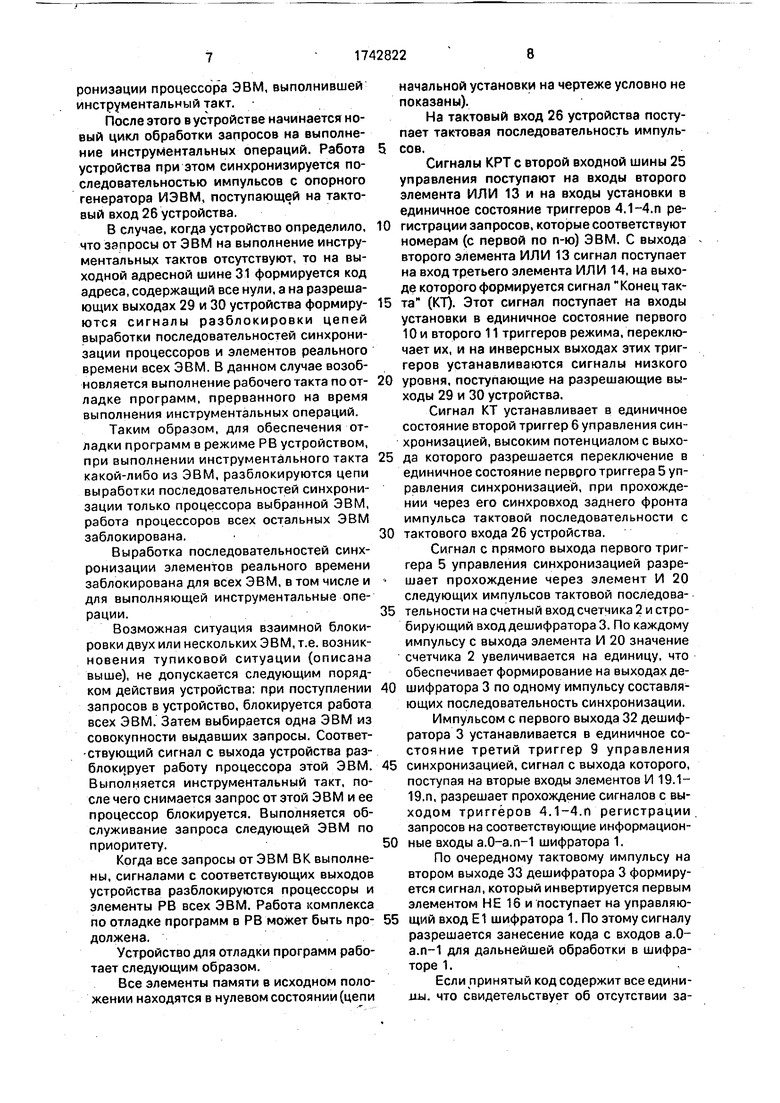

На тактовый вход 26 устройства поступает тактовая последовательность импуль. сов.

Сигналы КРТ с второй входной шины 25 управления поступают на входы второго элемента ИЛИ 13 и на входы установки в единичное состояние триггеров 4.1-4.П ре0 гистрации запросов, которые соответствуют номерам (с первой по n-ю) ЭВМ. С выхода второго элемента ИЛИ 13 сигнал поступает на вход третьего элемента ИЛИ 14, на выходе которого формируется сигнал Конец так5 та (КТ). Этот сигнал поступает на входы установки в единичное состояние первого 10 и второго 11 триггеров режима, переключает их, и на инверсных выходах этих триггеров устанавливаются сигналы низкого

0 уровня, поступающие на разрешающие выходы 29 и 30 устройства.

Сигнал КТ устанавливает в единичное состояние второй триггер 6 управления синхронизацией, высоким потенциалом с выхо5 да которого разрешается переключение в единичное состояние первого триггера 5 управления синхронизацией, при прохождении через его синхровход заднего фронта импульса тактовой последовательности с

0 тактового входа 26 устройства.

Сигнал с прямого выхода первого триггера 5 управления синхронизацией разрешает прохождение через элемент И 20 следующих импульсов тактовой последова5 тельности на счетный вход счетчика 2 истро- бирующий вход дешифратора 3. По каждому импульсу с выхода элемента И 20 значение счетчика 2 увеличивается на единицу, что обеспечивает формирование на выходахде0 шифратора 3 по одному импульсу составляющих последовательность синхронизации. Импульсом с первого выхода 32 дешифратора 3 устанавливается в единичное состояние третий триггер 9 управления

5 синхронизацией, сигнал с выхода которого, поступая на вторые входы элементов И 19.1- 19.п, разрешает прохождение сигналов с выходом триггеров 4.1-4.П регистрации запросов на соответствующие информацион0 ные входы а.О-а.п-1 шифратора 1.

По очередному тактовому импульсу на втором выходе 33 дешифратора 3 формируется сигнал, который инвертируется первым элементом НЕ 16 и поступает на управляю5 щий вход Е1 шифратора 1. По этому сигналу разрешается занесение кода с входов а.0 а.п-1 для дальнейшей обработки в шифраторе 1.

Если принятый код содержит все едини- иы. что свидетельствует об отсутствии запросов от ЭВМ. то на выходах А.1-А.П шифратора 1 формируется код, содержащий все единицы, он инвертируется блоком элементов ИЛИ 18 и поступает на выходную адресную шину 31 устройства, а на втором выходе ЕО шифратора 1 формируется сигнал, поступающий на вход установки в единичное состояние триггера 8 управления.

Если же в коде имеется хотя-бы один ноль, т.е. имеются запросы от ЭВМ, то на выходах А. 1-А.п шифратора 1 формируется инверсный код адреса ЭВМ с максимальным приоритетом, а на первом выходе GS- низкий потенциал, поступающий на инверсный 1-вход первого триггера 7 управления и на вход второго элемента НЕ 17. с инверсного выхода которого сигнал поступает на выход 28 устройства.

Сигнал с третьего выхода 34 дешифратора 3 задним фронтом обнуляет третий триггер 9 управления синхронизацией, низкий потенциал с выхода которого запирает элементы И 19.1-19.п.

. Кроме того, устанавливается в единичное состояние первый 7 или второй 8 триггеры управления, с прямых выходов которых сйкналы поступают на первые входы, соответственно первого 21 или второго 22 элементов И.

Сигналом с четвертого выхода 35 дешифратора 3 открывается один из элементов И 21 или 22, так как на первом входе одного из них установлен сигнал высокого уровня.

Если установлен в единичное состояние триггер 7 управления, то на выходе элемента И 21 формируется сигнал, который через элемент ИЛИ 15 обнуляет триггер 10 режима, с инверсного выхода которого потенциал высокого уровня поступает на первый разрешающий выход 29 устройства.

Таким образом иницируется инструментальный такт для обмена информацией между ПЭВМ и ЭВМ, адрес которой установлен на выходной адресной шине 31 устройства.

Если же установлен в единичное состояние триггер 8 управления, то на выходе элемента И 22 формируется сигнал, устанавливающий в нулевое состояние триггер 11 режима, а также через элемент ИЛИ 15 триггер 10 режима.

На выходах этих триггеров вырабатываются высокоуровневые потенциалы, поступающие на первый и второй разрешающие выходы 29 и 30 устройства. Это означает, что все ЭВМ могут продолжать выполнение рабочего такта.

По очередному синхроимпульсу на пятом выходе 36 дешифратора 3 формируется

сигнал, устанавливающий в нулевое состояние триггеры 7 и 8 управления.

По сигналу с шестого выхода 37 дешифратора 3 одновибратором 23 формируется

импульс, по переднему фронту которого ус- танавлива ется в нулевое состояние триггер управления синхронизацией, низкий потенциал с выхода которого поступает на D-вход триггера 5.

0 По заднему фронту текущего синхроимпульса триггер 5 устанавливается в нулевое состояние и низким потенциалом с прямого выхода запирает элемент И 20, по заднему фронту импульса с выхода одновибратора

5 23 обнуляется счетчик 2. С этого момента устройство переходит в режим ожидания.

Возобновление работы устройства происходит по сигналу КИТ, формируемому в разряде входной шине 24 управления, соот0 ветствующем ЭВМ, выполнявшей инструментальный такт. При этом обнуляется соответствующий триггер из группы триггеров 4.1-4.П, что свидетельствует о снятии удовлетворительного запроса, а на выходе

5 элемента ИЛИ 12 формируется сигнал КТИТ, поступающий на выход 27 окончания текущего такта отладки программ. Этим же сигналом, через элемент ИЛИ 14, формируется сигнал КТ.

0 Описанная выше последовательность работы элементов устройства осуществляется при обработке одного запроса от любой ЭВМ комплекса на выполнение инструментальных операций.

5 Формула изобретения

Устройство для отладки программ, содержащее первый и второй триггеры режима, первый элемент ИЛИ, выход которого соединен с нулевым входом первого тригге0 ра режима, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения его работоспособности при отладке взаимодействующих параллельно выполняемых в реальном вре5 мени программ на многомашинных комплексах, в него дополнительно введены шифратор, счетчик, дешифратор, п триггеров регистрации запросов от ЭВМ (п-число ЭВМ в комплексе), первый, второй, третий триг0 геры управления синхронизацией, первый и второй триггеры управления, три элемента ИЛИ, два элемента НЕ, блок элементов ИЛИ, группа из п элементов И, первый, второй, третий элементы И, одновибратор, при5 чем первая входная шина управления отладочной ЭВМ соединена с входом первого элемента ИЛИ и с входами установки в нулевое состояние п триггеров регистрации запросов от ЭВМ, вторая входная шина управления отладочной ЭВМ подключена к

входу второго элемента ИЛИ и к входам установки в единичное состояние п триггеров регистрации запросов от ЭВМ, выходы первого и второго элементов ИЛИ соединены с входами третьего элемента ИЛИ, выход которого соединен с входами установки в единичное состояние первого и второго триггеров режима и второго триггера управления синхронизацией, выход первого элемента ИЛИ является выходом окончания текущего такта отладки устройства, прямые выходы п триггеров регистрации запросов от ЭВМ соединены с первыми входами соответствующих п элементов И группы, вторые входы которых подключены к выходу третьего триггера управления синхронизацией, инверсные выходы п элементов И группы подключены к информационным входам шифратора, управляющий вход которого соединен с выходом первого элемента НЕ, вход которого подключен к второму выходу дешифратора, первый выход шифратора соединен с инверсным 1-входом первого триггера управления и с входом второго элемента НЕ, выход которого является выходом начала инструментального такта отладки программ устройства, второй выход шифратора соединен с инверсным 1-входом второго триггера управления, синхровходы первого и второго триггеров управления подключены к третьему выходу дешифратора, а выходы установки в нулевое состояние триггеров управления соединены с пятым выходом дешифратора, прямые выходы пер вого и второго триггеров управления соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых подключены к четвертому

выходу дешифратора, выходы первого и второго элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, инверсный выход первого

триггера режима подключен к первому разрешающему выходу устройства, выход второго элемента И соединен с входом установки в нулевое состояние второго триггера режима, инверсный выход которого подключен к второму разрешающему выходу устройства, группа выходов шифратора соединена с группой входов блока элементов ИЛИ, группа инверсных выходов которого подключена к выходной

адресной тине устройства для подключения к отлаживаемой ЭВМ, тактовый вход устройства соединен с синхровходом первого триггера управления синхронизацией и с первым входом третьего элемента И,

D-вход первого триггера управления синхронизацией соединен с выходом второго триггера управления синхронизацией, выход первого триггера управления синхронизацией соединен с вторым входом

третьего элемента И, выход которого соединен со стробирующим входом дешифратора и со счетным входом счетчика, выходы которого подключены к информационным входам дешифратора, первый

выход которого подключен к входу установки в единичное состояние третьего триггера управления синхронизацией, вход установки в 0й которого соединен с третьим выходом дешифратора, шестой

выход дешифратора через одновибратор соединен с входом установки в О счетчика и синхровходом и k-входом второго триггера управления синхронизацией.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для контроля последовательности выполнения программ | 1988 |

|

SU1674134A1 |

| Система отладки микропроцессорных устройств | 1989 |

|

SU1700559A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство приоритетного прерывания для микро-ЭВМ | 1982 |

|

SU1113803A1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для отладки программ | 1988 |

|

SU1594546A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

| Устройство для отладки и контроля хода программ | 1989 |

|

SU1691843A2 |

Изобретение относится к вычислительной технике, в частности к устройствам для отладки программ, и может быть использовано в многомашинных вычислительных комплексах для автоматической отладки взаимодействующих, параллельно выполняемых в реальном масштабе времени программ. Цель изобретения - расширение области применения за счет обеспечения возможности совместной отладки произвольного числа взаимодействующих, параллельно выполняемых в реальном масштабе времени программ на многомашинных вычислительных комплексах. Устройство содержит приоритетный шифратор, счетчик, дешифратор, п триггеров регистрации запросов, первый, второй и третий триггеры управления синхронизацией, первый, второй триггеры управления, первый и второй триггеры режима, первый - четвертый элементы ИЛИ, блок элементов ИЛИ, группу из п элементов И, первый - третий элементы И, одновибратор. 3 ил.

/

r

ЭВМ

1

29

и

1

26

27

28

U3BM

Фиг

Вх.25

U20

ст

г 1

Л

Фиг,3

п

| Устройство для контроля выполнения тестовой программы | 1979 |

|

SU943732A1 |

| Авторское свидетельство СССР № 1538757, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-23—Публикация

1990-04-17—Подача