(St) УСТРОЙСТВО для КОНТРОЛЯ ВЫПОЛНЕНИЯ ТЕСТОВОЙ ПРОГРАММЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности сигналов | 1980 |

|

SU1096650A1 |

| Устройство для контроля выполнения тестовой программы | 1986 |

|

SU1317442A1 |

| Устройство для индикации отказов в трехканальной вычислительной системе | 1989 |

|

SU1721608A1 |

| Устройство для контроля времени выполнения программы | 1983 |

|

SU1140124A1 |

| Устройство для тестового диагностирования цифровых блоков | 1987 |

|

SU1622884A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Устройство для контроля радиотехническихОб'ЕКТОВ | 1979 |

|

SU796859A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

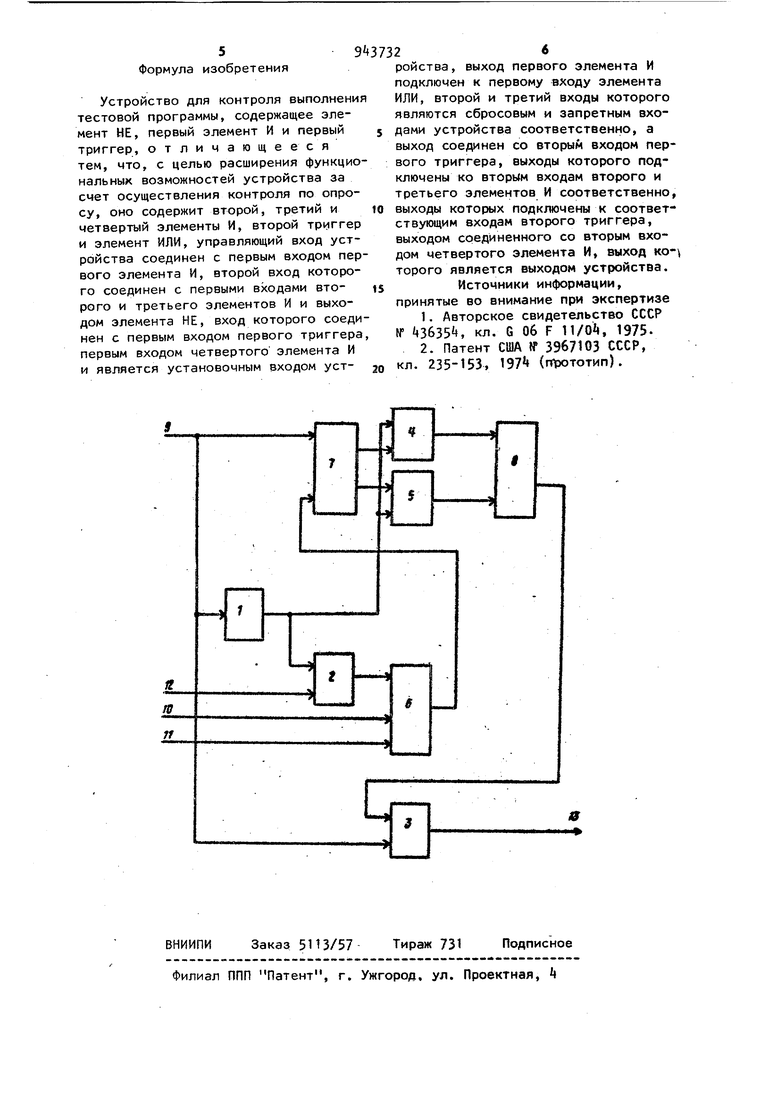

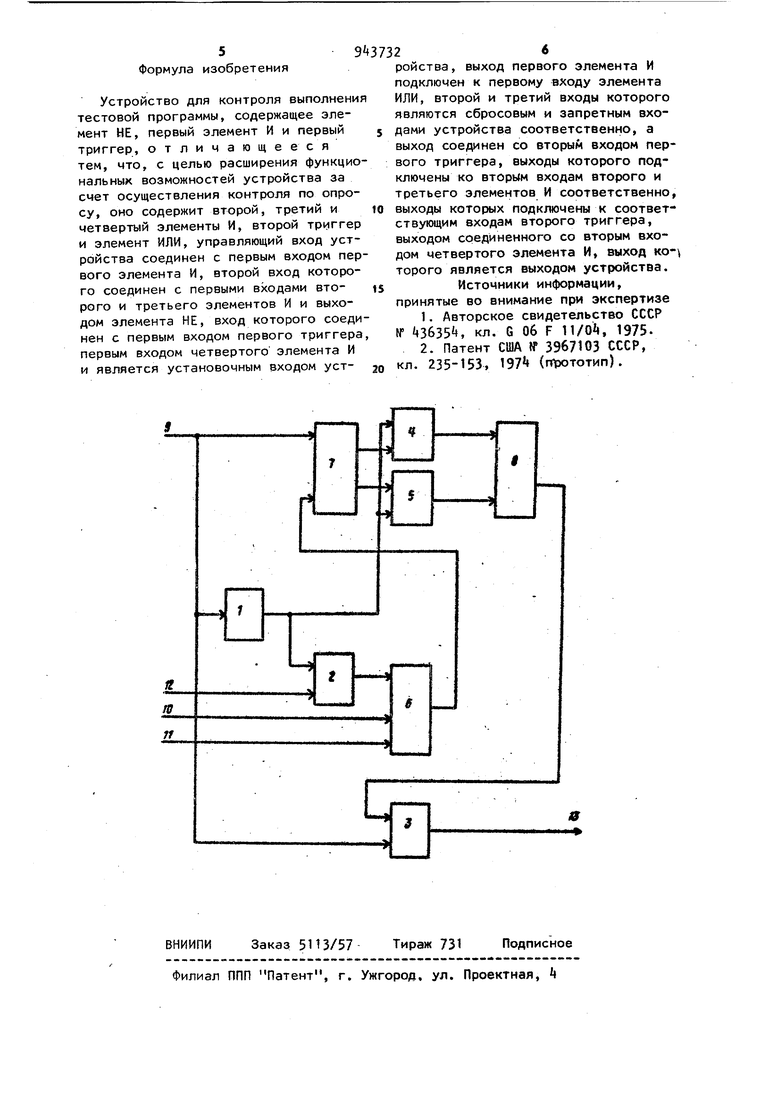

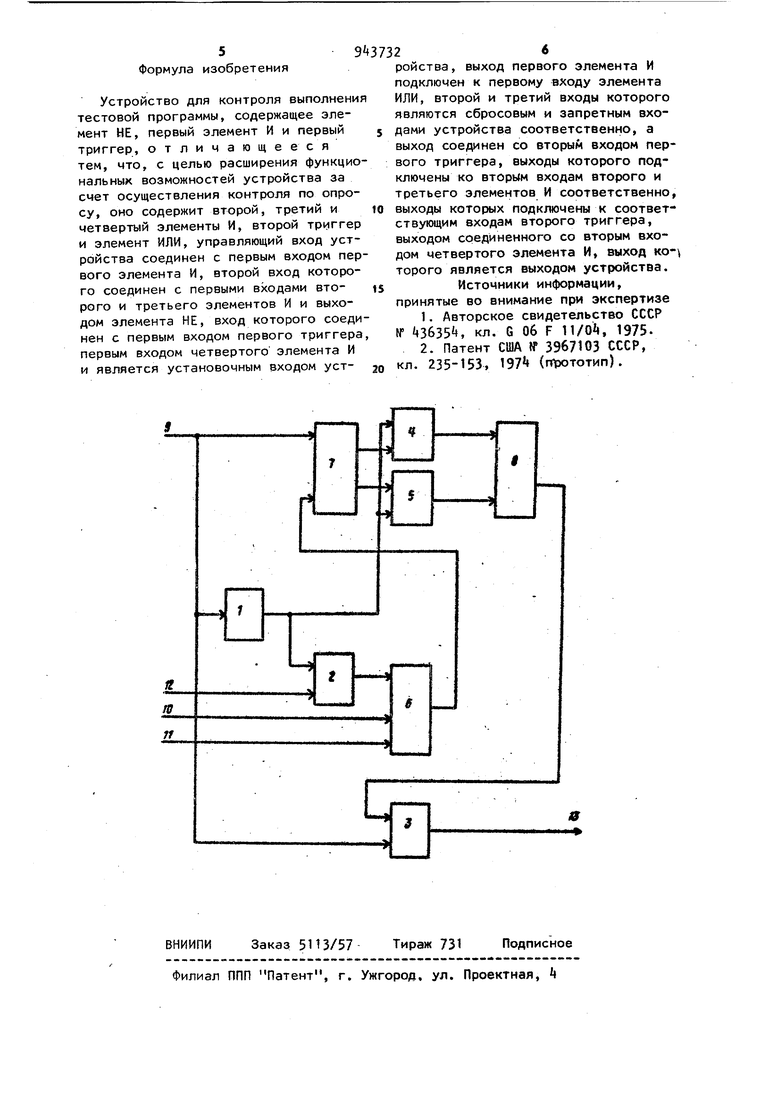

.Устройство относится к вычислительной технике и может быть исполь вано в автоматизированных системах, созданных на базе ЭВМ. Известно устройство, в котором контроль правильности функционирова ния системы осуществляется за счет введения дополнительныхч регистров Для буферизации поступающих сигнало и соответствующих схем сравнения, обнаруживающих неразрешенные ситуации l . Недостатком устройства является его сложность. Наиболее близким по технической сущности к предлагаемому является устройство для контроля, содержащее элемент НЕ, первый элемент И и пер вый триггер. В этом устройстве тестовые программы выполняются ЭВМ на самом высоком приоритете сразу же за временной меткой. После тестовой программы решаются целевые задачи системы до появления следующей метк Сигнал об удовлетворительном прохождении теста сравнивается с предварительно задержанным сигналом временной метки 2 . Недостатком устройства являются ограниченные функциональные возможности , которые обусловлены невозможностью принятия и обработки системой срочных сигналов, поступакзщих извне во время выполнения тестовых программ, имеющих самый высокий приоритет и жестко привязанных к временным меткам (отсутствие гибкости при работе системы в реальном масштабе времени); необходимость точного расчета временной задержки временной метки и, как следствие, сложностью ее схемной реализации; необходимость изменения схемы устройства при изменении длительности тестовых программ. Целью изобретения является расширение функциональных возможностей устройства за счет осуществления контроля по опрюсу. Поставленная цель достигается те что устройство содержит элемент НЕ, первый, второй, третий и четвертый элементы И, первый и второй триггер и элемент ИЛИ, управляющий вход уст ройства соединен с первым входом первого элемента И, второй вход которого соединен с первыми входами второго и третьего элементов И и выходом элемента НЕ, вход которого соединен с первым входом первого триггера, первым входом четвертого элемента И и является установочным входом устройства, выход первого элемента И подключен к первому вход элемента ИЛИ, второй и третий входы которого являются сбросовым и запре ным входами устройства соответственно, а выход соединен со вторым входом первого триггера, выходы которого подключены ко вторым входам второго и третьего элементов И соответственно выходы которых подключены к соответствующим входам второго триггера, выходом соединенного со вторым входом четвертого элемента И, выход которого является выходом устройства. На чертеже представлена блок-схе ма устройства. Устройство содержит элемент НЕ 1 первый, второй, третий и четвертый элементы И 2-5, элемент ИЛИ 6, первый и второй триггеры 7 и 8, установочный сбросовый, запретный, и управляющий входы и выход устройства 9-U. Устройство работает следующим об разом. .На вход 9 поступает временная ме ка и устанавливает триггер 7 в состояние О. После.окончания времен ной метки содержимое триггера 7 переписывается в триггер 8 элементы И k и 5. Причем перепись осуществля ется в течение всего интервала межд временными метками и прерывается сигналом метки, приходящим с элемента .НЕ 1. Если триггер 7 в интервале между метками изменяет свое со стояние, то изменяет свое состояние соответственно и триггер 8. Тестовая программа выполняется в любой части временного интервала между двумя соседними метками. Результатом правильного прохождения тестовой программы является появле4ние импульса реакции на тесты на входе 12. Если этот импульс поступает в интервале между метками (в противном случае он блокируется на элементе И 2 сигналом наличия метки, снимаемом с выхода элемента НЕ 1) он устанавливает триггер 7 в состояние 1 по цепи: вход 12, элемент И 2, элемент ИЛИ 6, вход триггера 7Это влечет за собой установку три|- гера 8 в состояние 1. Если импульс на входе 12 в интервале между метками не пришел, то триггеры 7 и 8 остаются в состоянии 6. Приход метки фиксирует состояние триггера 8 до следующего интервала. Элемент И 3, выход которого соединен с выходом 13, формирует сигнал непрохождения тестов (сигнал неисправности в системе) из сигнала метки и сигнала с инверсного плеча триггера 8. Сигнал непрохождения тестов вырабатывается только при наличии временной метки И условии,- что триггер 8 находится в СОСТОЯНИИ О. Для того, чтобы устройство не выдавало сигнала непрохождения тестов при начальном пуске системы, который асинхронен к временным меткам, вход 10 соединен с первым входом элемента ИЛИ 6. Начальный сброс устанавливает триггер 8 в состояние 1, что равносильно приходу сигнала реакции на тесты по входу 12. Для исключения появления сигнала непрохождения тестов при программном останове или для возможности отключения устройства используется вход 11, который соединен с входом элемента ИЛИ 6. Работа устройства при появлении сигнала на входе 11 аналогична работе устройства при появлении сигнала на входе 10. Изобретение дает положительный эффект за счет расширения функцйьнальных возможностей, а именно позволяет обнаруживать неисправность в системе даже при неисправном процессоре, т.е. в условиях, когда тестовые программы в принципе не могут выполняться, позволяет выполнять тестовые программы в любой части временного интервала между двумя соседними временными метками, не требует формирования временных задержек, схема устройства не меняется при изменении длительности тестовых про грамм.

формула изобретения

Устройство для контроля выполнения тестовой программы, содержащее элемент НЕ, первый элемент И и первый триггер, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет осуществления контроля по опросу, оно содержит второй, третий и четвертый элементы И, второй триггер и элемент ИЛИ, управляющий вход устройства соединен с первым входом первого элемента И, второй вход которого соединен с первыми входами второго и третьего элементов И и выходом элемента НЕ, вход которого соединен с первым входом первого триггера первым входом четвертого элемента И и является установочным входом уст.2. W

9t3732

ройства, выход первого элемента И подключен к первому входу элемента ИЛИ, второй и третий входы которого являются сбросовым и запретным входами устройства соответственно, а выход соединен со вторым входом первого триггера, выходы которого подключены ко вторым входам второго и третьего элементов И соответственно выходы которых подключены к соответствующим входам второго триггера, выходом соединенного со вторым входом четвертого элемента И, выход которого является выходом устройства.

Источники информации, принятые во внимание при экспертизе

8

Авторы

Даты

1982-07-15—Публикация

1979-04-05—Подача