Устройство относится к области вычислительной техники и можег быть использовано для контроля правильности выполненич программ ЭВМ и других устройств и систем программного управления, а также для автоматизированной отладки программ и контроля очередности следования модулей программ.

Целью изобретения является расширение области применения устройства путем реализЈ,-1и контроля последовательности выполнения программ на каждой парал- /,°льной ви вычислительного процесса.

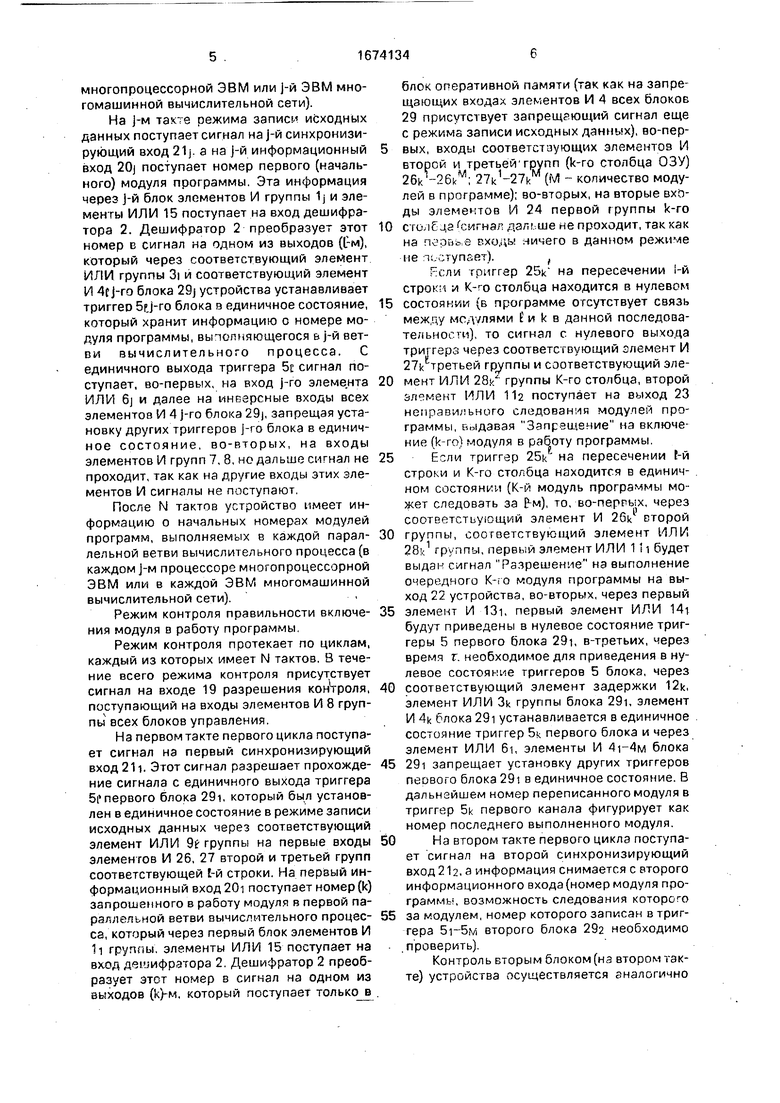

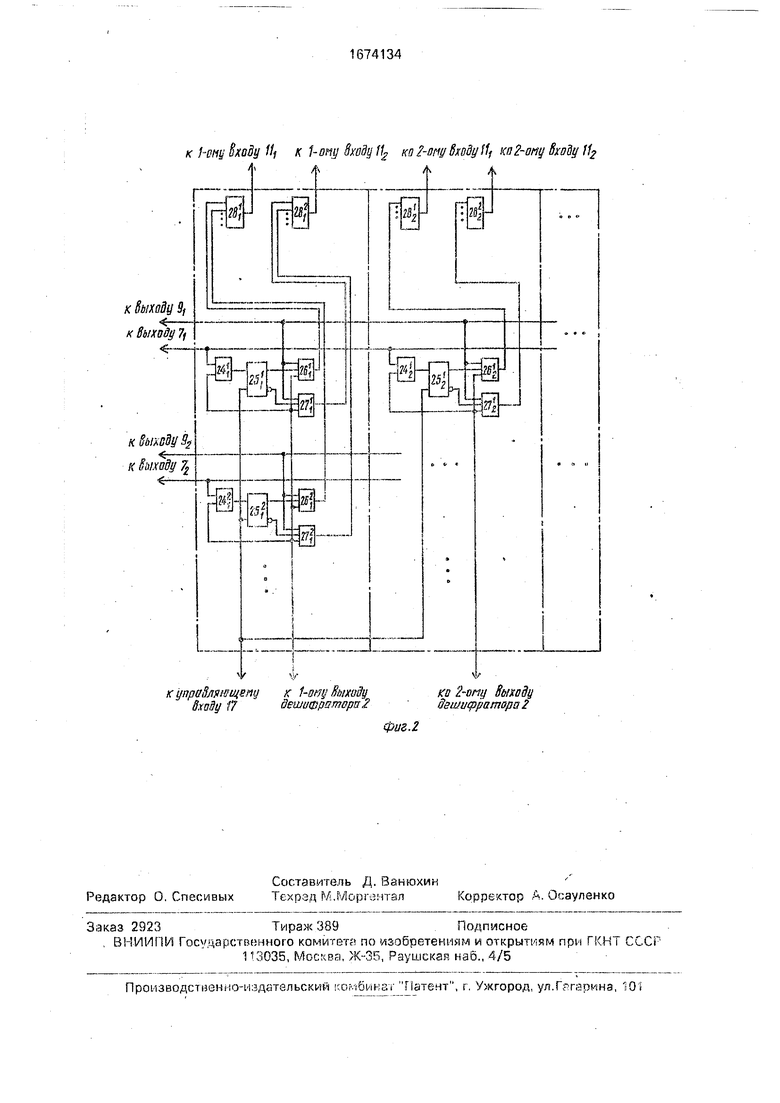

Ня фиг.1 л;жа общап функциональная схома устройстоа; на фиг.2 - функциональ- нгя схемл блоха оперативной памяти.

Устройство содержит группу блоков элементов И 1, дешифратор 2, группу элементов ИЛИ 3 блока управления, вторую группу элементов И 4 блока управления, группу триггеров 5 блока управления, второй элемент ИЛИ 6 блока управления, первую группу элементов И 7, первую группу элементов И 8 блока управления, первую группу элементов ИЛИ 9, блок 10 оперативной памяти, первый 11.1 -л второй 11.2 элементы ИЛИ, группу элементов задержки 12, элемент И 13 блока управления, первый элемент ИЛИ 14 блока управления, вторую группу элементов ИЛИ 15, первый 16 вход установки устройства, второй 17 вход уста- нопкоуп ройствз, вход 18 разрешения запиО

ы

CJ

си устройства, вход 19 разрешения контроля устройства, группу информационных входов 20 устройства, группу входов синхронизации 21 устройства, выходы правильного 22 и неправильного 23 следования модулей программы устройства Каждая ячейка блока оперативной памяти содержит элемент И 24, триггер 25, элементы И 26 и 27. Блок оперативной памяти включает группу элементов ИЛИ 28. Устройство содержит N бпоков 29 управления оперативной памятью,

Устройство функционирует в четырех режимах: 1) подготовительный режим; 2) режим записи зависимостей модулей программы; 3) режим записи исходных данных; 4) режим контроля правильности включения модуля в работу программы. Подготовительный режим. Во время подготовительного режима поступают сигналы на вход 16 устройства для приведения в нулевое состояние триггеров 5 и Hd вход 17 устройства для приведения в нулевое состояние триперов 25. Триггеры 5 и триггеры 25 устанавливаются р нулевое состояние.

Режим записи зависимостей модулей программы.

На протяжении всего режима записи присутствуют сигнал на входе 18 разрешения записи, который поступает на входы группы элементов И 7, а также сигнал на первом синхронизирующем входе 211, который поступает, во-первых, на вход первого блока элементов И 11 группы, во-вторых, на входы элементов И 4 блока 291, в-третьих, на элементов И 8 группы первого блока 291, в-четвертых, на-вход элемента И 13 первого блока 29i В режиме записи информация поступает только но первый информационный вход 20i, т.е. работает только первый блок 29i.

Режим записи делится на циклы, а циклы в свою очередь на такты.

На первом такте первого цикла на первый информационный вход 20 подается номер модуля (i), который через первый блок элементов И 1i группы и элементы ИЛИ 15 поступает на вход дешифратора 2. Дешифратор 2 преобразует номер в сигнал на одном из выходов, который через соответствующий элемент ИЛИ 3| группы первого блока 29т и соответствующий элемент И 4| первого блока управления устанавливает в единичное состояние 1-й триггер 5| первого блока управления С единичного выхода установившегося в единичное состояние триггера 5i первого блока управления сигнал поступает, во-первых, через элемент ИЛИ 6 группы первою блока

управления на первые инверсные входы группы элементов И 4 первого блока управления, запрещая установку других триггеров первого блока управления в единичное

состояние, во-вторых, через соответствующий элемент И 1 группы на первые входы элементов И 24 первой группы 1-й строки блока 10 оперативной памяти.

На втором такте на первый информаци0 онный вход 20i устройства последовательно подаются номера модулей, которые могут быть включены в работу после 1-го модуля. Эта информация через первый блок элементов И 1i группы и элементы ИЛИ 15 посту5 пает на вход дешифратора 2. Дешифратор 2 каждый последовательно поступающий номер преобразует в сигнал на одном из выходов, который поступает только в блок оперативной памяти (так как на инверсные

0 входы всех элементов И 4 первого блока управления поступает запрещающий сигнал 1) и через вход соответствующего (К-го столбца блоков) элемента И 24к первой группы 1-й строки и К-го столбца ус5 танавлигзает соответствующий триггер 25к в единичное состояние.

Единичное состояние триггера 25к на пересечении i и строки и К-го столбца хранит информацию о возможности следова0 нгя за I м модулем программы К-го модуля.

На третьем такте поступает сигнал на вход 16 устройства для приведения в нулевое состояние триггеров 5 блоков управле5 ния. Триггеры 5 первого блока управления (триггеры 5 остальных блоков приведены в нулевое состояние на подготовительном режиме) устанавливаются в нулевое состояние, на ичворсные входы всех элементов И

0 4 запрещающий сигнал 1 не поступает.

Далее устройство переходит ко второму циклу режима записи (к первому такту) и т.д. пока не будет записаны все зависимости модулей программ.

5Режим записи исходных данных.

В режиме записи исходных данных последовательно в каждый из N блоков управления записываются номера первых модулей программы, которые начинают вы0 полняться на соответствующих параллельных ветвях вычислительного процесса (процессорах многопроцессорной ЭВМ или ЭВМ многомашинной вычислительной се- ти).

5Дачный режим протекает за N тактов.

На каждом j-м такте в триггеры 5 j-ro блока 9j записывается номер первого (начального) модуля программы, который начинает выполняться в j-й параллельяой ветви вычислительного процесса (j-м процессоре

многопроцессорной ЭВМ или )-й ЭВМ многомашинной вычислительной сети).

На j-м тач. е режима записи исходных данных поступает сигнал на j-й синхронизирующий вход 21 j. а на j-й информационный вход 20) поступает номер первого (начального) модуля программы. Эта информация через J-й блок элементов И группы 1t и элементы ИЛИ 15 поступает на вход дешифратора 2. Дешифратор 2 преобразует этот номер с сигнал на одном из выходов (1-м), который через гоответствующий элемент ИЛИ группы 3| и соответствующий элемент И 4f J-ro блока 29j устройства устанавливает триггер 5pj-ro блока в единичное состояние, который хранит информацию с номере модуля программы, выполняющегося ь j-й вет- пи вычислительного процесса. С единичного выхода триггера 5с сигнал поступает, во-первых, на вход j-ro элемента ИЛИ 6 и далее на ингергные входы всех элементов И 4 j-ro блока 29j, запрещая установку других триггеров блока в единичное состояние, во-вторых, на входы элементов И групп 7, 8, но дальше сигнал не проходит, так как на другие входы этих -,ле- ментов И сигналы HP поступают.

После N тактов устройство имеет информацию о начальных номерах модулей программ, выполняемых в каждой параллельной ветви вычислительного процесса (в каждом j-м процессоре многопроцессорной ЭВМ или в каждой ЭВМ многомашинной вычислительной сети).

Режим контроля правильности включения модуля в работу программы

Режим контроля протекает по циклам, каждый из которых имеет N тактов. В течение всего режима контроля присутствует сигнал на входе 19 разрешения контроля, поступающий на входы элементов И 8 группы всех блоков управления.

На первом такте первого цикла поступает сигнал на первый синхронизирующий вход 211. Этот сигнал разрешает прохождение сигнала с единичного выхода триггера 5ilпервого блока 29i. который был установлен в единичное состояние в режиме записи исходных данных через соответствующий элемент ИЛИ 9ir группы на первые входы элементов И 26, 27 второй и третьей групп соответствующей 1-й строки. На первый информационный вход20.1 поступает номер (k) запрошенного в работу модуля в первой па- раглешной ветви вычислительного процесса, который через первый блок элементов И 11 гругн.ы элементы ИЛИ 15 поступает на вход дешифратора 2. Дешифратор 2 преобразует этст номер в сигнал на одном из выходов (k/-м, который поступает только в

блок оперативной памяти (так как на запре щ эющих входах элементов И 4 всех блоков 29 присутствует запрещ ющий сигнал еще с режима записи исходных данных), во-пер- 5 вых, входы соответствующих элементов И второй и третьей групп (k-ro столбца ОЗУ) 26к 26kM; 27k -27k (M - количество модулей в программе); во-вторых, на вторые входу элементов И 24 первой группы k-ro

0 cio.if да (сигнал дал1 ше пе проходит, так как на сходы -tnsero в данном режиме не и отупеет).t

сли триггер 25k на пересечении 1-й строги и К-го столбца находится в нулевом

5 состоянии (в профамме отсутствует связь межцу модулями Е и k в данной последовательности), то сигнал с нулевого выхода три герз через соответс i ВУЮЩИЙ слемент И 27k третьей группы и соответствующий эле0 мент ИЛИ 28k rp/ппы К-го столбца, второй :,-.г1омент ИЛИ 112 поступает на выход 23 неправильного следования модулей программы, Е1гЭ|давая Запрещение на включение fk rot модуля в работу программы.

5Рели триггер пересечении 1-й

строки и К-го столбца находится в единичном состоянии (К- модуль программы может следовать за Р-М) то, ьо-пергых, через соответствующий элемент И 2Gk второй

0 группы, соответствующий элемент ИПИ 28. группы, первой элемент ИЛИ 1 i 1 будет сыдаи сигнал Разрешение на выполнение очередного K-i о модуля программы на выход 22 устройства, во-вторых, через первый

5 элемент И 13i, первый элемент ИЛИ 14i будут приведены в нулевое состояние триггеры 5 первого блока 29к в-третьих, через времч г. необходимое для приведения в нулевое состояние триггеров 5 блока, через

0 соответствующий элемент задержки 12k, элемент ИЛИ 3k группы блока 29i, элемент И 4k блока 29т устанавливается в единичное состояние триггер 5t первого блока и через элемент ИЛИ 6i, элементы И блока

5 29i запрещает установку других триггеров псового блока 291 в единичное состояние. В дальнейшем номер переписанного модуля в триггер 5k первого канала фигурирует как номер последнего выполненного модуля.

0 На втором такте первого цикла поступает сигнал на второй синхронизирующий вход 212. а информация снимается с второго информационного входа (номер модуля программы, возможность следования которсго

5 за модулем, номер которого записан в триггера 5г-5м второго блока 292 необходимо проверить).

Контроль вторым блоком(н9 втором гак- те) устройства осуществляется диалогично

контролю в первом блоке (на первом такте), и т д. по следующим тактам цикла

Если на j-м такте отсутствует информация на j-м информационном входе 20j, то через время, равное продолжительности такта, устройство переходит к Q 11)-му гякту

По окончании N-ro такта первого цикла устройство переходит к 1-му такту второго цикла и т д.

Формупч изобретение Устройство для контроля передо 1 i тельности выполнения программ, щее блок оперативной памяти, первую ipynny элементов И, группу элементов задержки дешифратор, первый и в .рои эле менты ИЛИ, порныи блок упрэнлр.шп оперативной памятью ьключающии группу элементов ИЛИ блока управления псовую и вторую группы элементов И блока управления, группу триггеров блока управления, первый элемент ИМИ блока управления, причем первая i руппа выходов блока опгра тивной памяти соединена с группой входов первого элемента ИЛИ входами элементов зпдерл ки группы, вторая групп., выходое блока ос еративной ппмяти соединена с фуппои вхгсрв второго элемент, ИЛИ выходы первою и второго элементоп Им И являются соответственно выходами правильного и неправильного следования модулей программы устройства выходы дешифратора соединены с группой входов признака записи информации блока опера тивной памяти выходы эпементов И первой групгты соединены с группой входов записи блока оперативной памяти, первые чходы элементов И первой группы подключены i- входу разрешения записи устройства вторые входы элементов И первой группы соединены с выходами соответствующих триггеров группы первого блока управления, нулевые входы триггеров группы блока управления соединены с выходом первого элемента ИЛИ блока управления, перрме входы элементов И первой групчи бгока управления соединены с выходами оотьет ствующих триггеров группы блока уппавле- ния, отличающееся тем, ч i о, ; лью расширения области применения яа счет реализации контроля последовательности выполнения программ на каждой чарэл- лельной ве1ви вычислительною прпч 5соа, оно содержит ipynny блоков .ТПБ И,

первую и вторую группы элементов ИЛИ и N-1 бпокон управления оперативной памятью во все N блоков управления оперативной памятью введены элемент И блока

управления и второй элемент ИЛИ блока управления, причем в каждом j-м блоке уп- рсшления оперативной памятью (j Г N) выход элемента И блока управления соединен с первым входом первого элемента ИЛИ

0 блокз уппавпения, выходы триггеров груп- п блока управления соединены с группой входов второго элемента ИЛИ блока управления, коюрсго соединен с инверсными ьходами элементов И второп группы

5 бпока управления первые входы которых соединены с уходами соотве хтзующих элементе ИЛИ группы опока управления, выходы элементов И второй группы блока управления соединены с единичными вхо0 дамп соответстьующил триггеров группы блока управление, вторые нходы элементов И первой труппы олока управления соеди- НРНЫ с входом разрешении контроля устройства третьи входы элементов И первой

5 групп i Гипка упртвлепия, входы jjiOMerroR lyi второй rpvnnbi блока управле- нпя и r.fpf 1 1-1 ii/од тломента И бпока управ- соединены с . м входом группы нхи/ов синхронизации устройства первые

0 и вторые входы элементов ИЛИ блика уп- соодинень, соответственно с выходами соответствующих эпементов задержки группы и г соответствующими вы- лодчми д(-ш/фр тора вторые входы эле5 мента И блока управления и первого элемента Л МИ блока управления соединены QOiBuiCTi енно с выходом первого элемен т ИЛИ и первым установочным входом устройства, второй установочный вход

Q которого подключен к группе входов начальной установки блока оперативной памяти, выходы - че снтор И первой группы блока управпеиия соединены с j-ми входами соответствующих элементов ИЛИ первой груп5 пы, выходы которых соединены с группой входов опроса Спока оперативной памяти, управляющие блоков элементов И i оупги1 точены к группе входовсинхро- низаиии устройства, гоуппа информационО Hbi слотов устроит гва соединена с информационными входами блоков элементов И группы ныходы которых соединены с ссответстг./к.щими входами элементов И ПИ второй fpy-Liu, выходы которых среди

j IK-HI,, Ц уппои входов дешифратора

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности выполнения программ с оперативной корректировкой зависимостей | 1989 |

|

SU1665379A1 |

| Устройство для контроля последовательности выполнения программ | 1985 |

|

SU1254493A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1310832A1 |

Изобретение относится к области вычислительной техники и может быть использовано для контроля правильности выполнения программ ЭВМ и других устройств и систем программного управления, а также для автоматизированной отладки программ и контроля очередности следования модулей программ. Цель изобретения - расширение области применения устройства путем контроля последовательности выполнения программ на каждой ветви вычислительного процесса (в каждом процессоре многопроцессорной ЭВМ или же в каждой ЭВМ многомашинной вычислительной сети) за счет организации нескольких каналов контроля, введения схемы синхронизации каналов и последовательного использования всеми каналами одного ОЗУ при контроле последовательности выполнения программ. Устройство для контроля последовательности выполнения программ содержит N блоков управления оперативной памятью, блок оперативной памяти, дешифратор, группу блоков элементов И, группы элементов ИЛИ, группу элементов И, группы элементов задержки и элементы ИЛИ. 2 ил.

а

01

to

0/

сг

°-mi- и

г д

1«Нг/ 7/

-о

К

:

5

г

Щ tg

f

teiu.91

к 1-ому ftxody HI к 1-ому входу 11 ко -ощ входу }1t ко 8ходу Iff

к выходу 9,

к Выходу 7j к 8шсду 92 к Выходу 72

:

к управляющему к 1-ому Выходу Входу ftдешифратора 2

ко 2-ому Выходу дешифратора 2

| Устройство для контроля выполненияпРОгРАММы | 1979 |

|

SU842823A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля последовательности выполнения программ | 1985 |

|

SU1254493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1988-12-19—Подача