to

Изобретение относ,:тся к вычислительной технике, в частности к запо- ьтнающим устройствам.

Целью изобретения является повышение достоверности контроля и упрощение устройства.

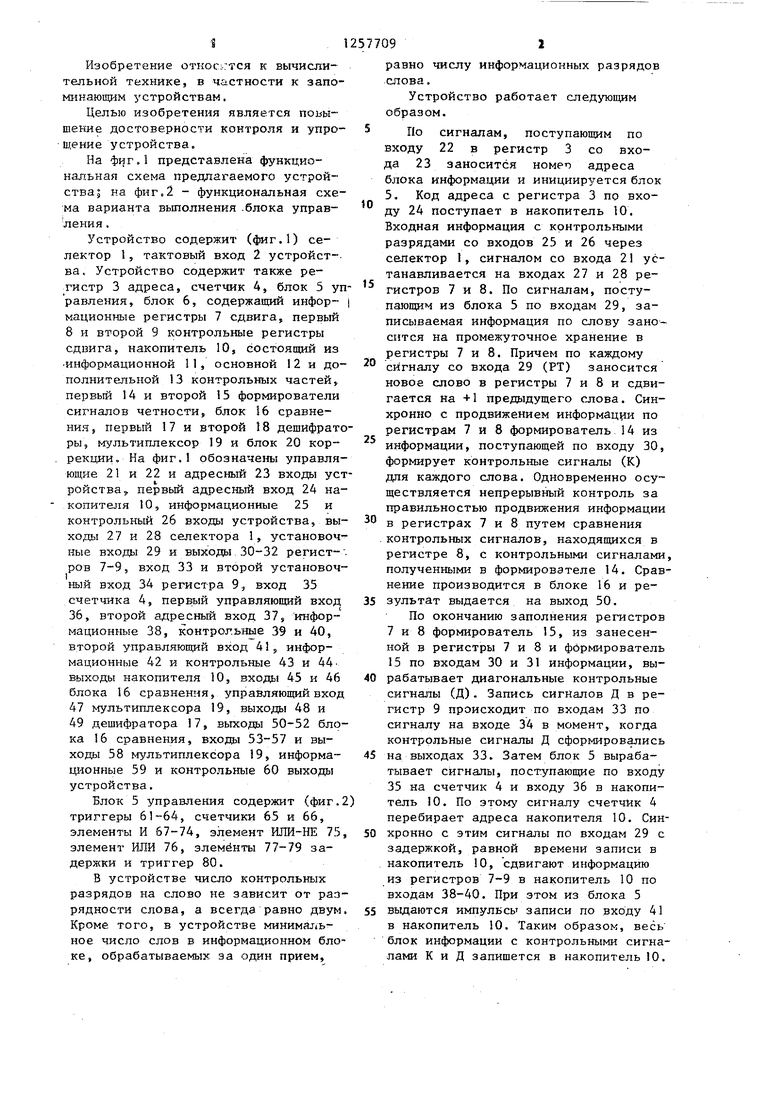

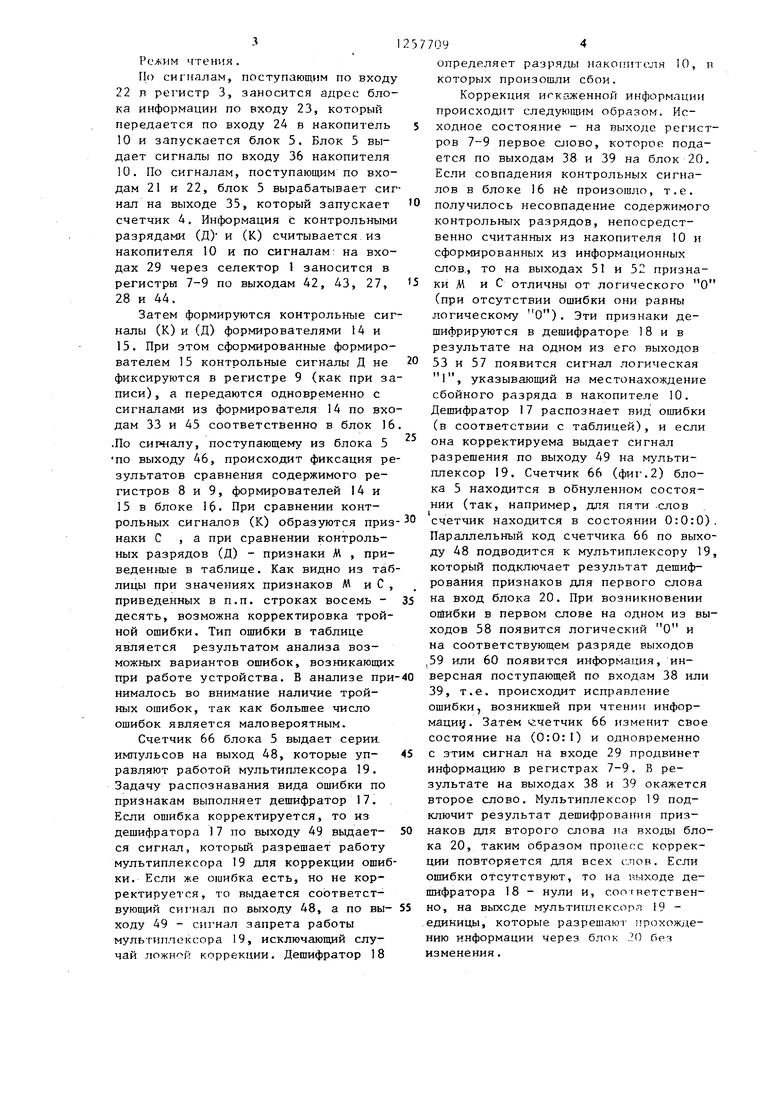

На представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема варианта вьшолнения -блока управления ,

Устройство содержит (фиг.1) селектор 15 тактовый вход 2 устройст-. на. Устройство содержит также регистр 3 адреса, счетчик 4, блок 5 уп- равления, блок 6, содержащий инфор- | мационные регистры 7 сдвига, первый 8 и второй 9 контрольные регистры сдвига, накопитель 10, состоящий из информационной 1, основной 12 и до- 20 полнительной 13 контрольных частей, первый 14 и второй 15 формирователи сигналов четности, блок 16 сравнения, первый 17 и второй 18 дешифраторы, мультиплексор 19 и блок 20 кор- 25 рекции. На фиг. обозначены управляющие 21 и 22 и адресный 23 входы устройства,, первый адресный вход 24 накопителя 10, информационные 25 и контрольный 26 входы устройства, вы- 3D ходы 27 и 28 селектора 1, установоч- ные входы 29 и выходы 30-32 регист- . ров 7-9, вход 33 и второй установочный вход 34 регистра 9., вход 35 счетчика 4, первый управляющий вход 35 36, второй а дресный вход 37, информационные 38, контрольные 39 и 40, второй управляющий вход 41, информационные 42 и контрольные 43 и 44- выходы накопителя 10, входы 45 и 46 40 блока 16 сравнения, управляющий вход 47 мультиплексора 19, выходы 48 и 49 дешифратора 17, выходы 50-52 блока 16 сравнения, входы 53-57 и выходы 58 мультиплексора 19, информа- 45 ционные 59 и контрольные 60 выходы устройства.

Блок 5 управления содержит (фиг.2) триггеры 61-64, счетчики 65 и 66, элементы И 67-74, элемент ИЛИ-НЕ 75, 50 элемент ИЛИ 76, элементы 77-79 задержки и триггер 80.

В устройстве число контрольных разрядов на слово не зависит от разрядности слова, а всегда равно двум. 55 Кроме того, в устройстве минима11Ь- ное число слов в информационном блоке, обрабатываемых за один прием.

12577092

равно числу информационных разрядов слова.

Устройство работает следующим образом.

По сигналам, поступающим по входу 22 в регистр 3 со входа 23 заносится номеп адреса блока информации и инициируется блок 5, Код адреса с регистра 3 по входу 24 поступает в накопитель 10. Входная информация с контрольными разрядами со входов 25 и 26 через

селектор 1, сигналом со входа 21 устанавливается на входах 27 и 28 регистров 7 и 8. По сигналам, поступающим из блока 5 по входам 29, записываемая информация по слову заносится на промежуточное хранение в регистры 7 и 8. Причем по каждому сигналу со входа 29 (РТ) заносится новое слово в регистры 7 и 8 и сдвигается на -I-1 предыдущего слова. Синхронно с продвижением информац 1и по регистрам 7 и 8 формирователь 14 из информации, поступающей по входу 30, формирует контрольные сигналы (К) для каждого слова. Одновременно осуществляется непрерывный контроль за правильностью продвижения информации в регистрах 7 и 8 путем сравнения контрольных сигналов, находящихся в регистре 8, с контрольными сигналами полученными в формирователе 14. Срав нение производится в блоке 16 и результат выдается на выход 50.

По окончанию заполнения регистров 7 и 8 формирователь 15, из занесенной в регистры 7 и 8 и фбрмирователь 15 по входам 30 и 31 информации, вырабатывает диагональные контрольные сигналы (Д). Запись сигналов Д в регистр 9 происходит по входам 33 по сигналу на входе 34 в момент, когда контрольные сигналы Д сформировались на выходах 33. Затем блок 5 вырабатывает сигналы, поступающие по входу 35 на счетчик 4 и входу 36 в накопитель 10. По этому сигналу счетчик 4 перебирает адреса накопителя 10. Син хронно с этим сигналы по входам 29 с задержкой, равной времени записи в накопитель 10, сдвигают информацию из регистров 7-9 в накопитель 10 по входам 38-40. При этом из блока 5 вьщаются импульсы записи по входу 41 в накопитель 10. Таким образом, весь блок информации с контрольными сигна лами К и Д запищется в накопитель 10.

селектор 1, сигналом со входа 21 устанавливается на входах 27 и 28 регистров 7 и 8. По сигналам, поступающим из блока 5 по входам 29, записываемая информация по слову заносится на промежуточное хранение в регистры 7 и 8. Причем по каждому сигналу со входа 29 (РТ) заносится новое слово в регистры 7 и 8 и сдвигается на -I-1 предыдущего слова. Синхронно с продвижением информац 1и по регистрам 7 и 8 формирователь 14 из информации, поступающей по входу 30, формирует контрольные сигналы (К) для каждого слова. Одновременно осуществляется непрерывный контроль за правильностью продвижения информации в регистрах 7 и 8 путем сравнения контрольных сигналов, находящихся в регистре 8, с контрольными сигналами полученными в формирователе 14. Сравнение производится в блоке 16 и результат выдается на выход 50.

По окончанию заполнения регистров 7 и 8 формирователь 15, из занесенной в регистры 7 и 8 и фбрмирователь 15 по входам 30 и 31 информации, вырабатывает диагональные контрольные сигналы (Д). Запись сигналов Д в регистр 9 происходит по входам 33 по сигналу на входе 34 в момент, когда контрольные сигналы Д сформировались на выходах 33. Затем блок 5 вырабатывает сигналы, поступающие по входу 35 на счетчик 4 и входу 36 в накопитель 10. По этому сигналу счетчик 4 перебирает адреса накопителя 10. Синхронно с этим сигналы по входам 29 с задержкой, равной времени записи в накопитель 10, сдвигают информацию из регистров 7-9 в накопитель 10 по входам 38-40. При этом из блока 5 вьщаются импульсы записи по входу 41 в накопитель 10. Таким образом, весь блок информации с контрольными сигналами К и Д запищется в накопитель 10.

Режим чтения.

Flo сигналам, поступающим по входу 22 л регистр 3, заносится адрес блока информации по входу 23, который передается по входу 24 в накопитель 10 и запускается блок 5. Блок 5 выдает сигналы по входу 36 накопителя 10. По сигналам, поступающим по входам 21 и 22, блок 5 вырабатывает сиг нал на выходе 35, который запускает счетчик 4. Информация с контрольными разрядами (Д) и (К) считывается из накопителя 10 и по сигналам: на входах 29 через селектор 1 заносится в регистры 7-9 по выходам 42, 43, 27, 28 и 44.

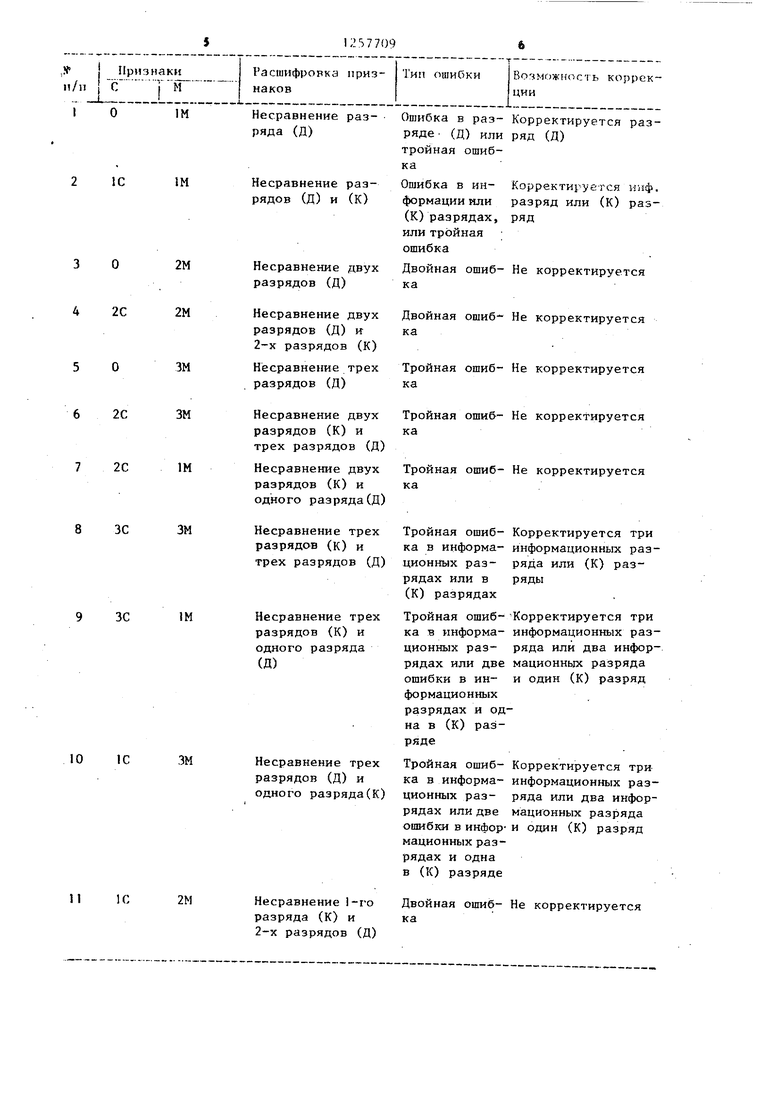

Затем формируются контрольные сигналы (К) и (Д) фopмиpoвaтeля fи 14 и 15. При этом сформированные формирователем 15 контрольные сигналы Д не фиксируются в регистре 9 (как при записи) , а передаются одновременно с сигналами из формирователя 14 по входам 33 и 45 соответственно в блок 16, .По сирналу, поступающему из блока 5 по выходу 46, происходит фиксация результатов сравнения содержимого регистров 8 и 9, формирователей 14 и 15 в блоке 16. При сравнении контрольных сигналов (К) образуются признаки С , а при сравнении контрольных разрядов (Д) - признаки М , приведенные в таблице. Как видно из таблицы при значениях признаков М и С, приведенных в п.п, строках восемь - десять, возможна корректировка тройной ошибки. Тип ошибки в таблице является результатом анализа возможных вариантов ошибок, возникающих при работе устройства. В анализе принималось во внимание наличие тройных ошибок, так как большее число ошибок является маловероятным.

Счетчик 66 блока 5 выдает серии, импульсов на выход 48, которые управляют работой мультиплексора 19. Задачу распознавания вида ошибки по признакам выполняет дешифратор 17. Если ошибка корректируется, то из дешифратора 17 по выходу 49 выдается сигнал, который разрешает работу мультиплексора 19 для коррекции ошибки. Если же ошибка есть, но не корректируется, то выдается соответст- вуюпр1й сигнал по выходу 48, а по выходу 49 - сигнал запрета работы мультиплексора 19, исключаюш 1Й случай ложной коррекции. Дешифратор 18

25

577094

определяет разряды накопителя 10, н которых произошли сбои.

Коррекция искаженной информации происходит следующим образом. Ис- 5 ходное состояние - на выходе регистров 7-9 первое слово, которое подается по выходам 38 и 39 на блок 20. Если совпадения контрольных сигналов в блоке 16 не произошло, т.е. О получилось несовпадение содержимого контрольных разрядов, непосредственно считанных из накопителя 10 и сформированных из информационных слов., то на выходах 51 и 52 призна- 5 ки М и С отличны от логического О (при отсутствии ошибки они равны логическому О) . Эти признаки дешифрируются в дешифраторе 18 и в результате на одном из его выходов 0 53 и 57 появится сигнал логическая 1, указывающими на местонахождение сбойного разряда в накопителе 10. Дешифратор 17 распознает вид ошибки (в соответствии с таблицей), и если она корректируема выдает сигнал разрешения по выходу 49 на м льти- плексор 19. Счетчик 66 (фиг.2) блока 5 находится в обнуленном состоянии (так, например, для пяти -слов 0 счетчик находится в состоянии 0:0:0). Параллельный код счетчика 66 по выходу 48 подводится к мультиплексору 19, который подключает результат дешифрования признаков для первого слова 5 на вход блока 20. При возникновении ойибки в первом слове на одном из выходов 58 появится логический О и на соответствующем разряде выходов 59 или 60 появится информация, ин- 0 версная поступающей по входам 38 или 39, т.е. происходит исправление ошибки, возникшей при чтении инфор- мациц. Затем гчетчик 66 изменит свое состояние на (0:0:1) и одновременно 5 с этим сигнал на входе 29 продвинет информацию в регистрах 7-9. В результате на выходах 38 и 39 окажется второе слово. Мультиплексор 19 подключит результат дешифрования приз- 0 наков для второго слова на входя блока 20, таким образом процесс коррекции повторяется для всех с-.лов. Если ошибки отсутствуют, то на выходе дешифратора 18 - нули и, соо rr eтcтвeн- 5 но, на выходе мультиплексора 19 - .единицы, которые разрешаю - прохождению информации через блок .. О без изменения.

ряда (Д)

1C

IM

Несравнение разрядов (Д) и (к)

C

2M

2M

3M

Несравнение двух разрядов (Д)

Несравнение двух разрядов (Д) и 2-х разрядов (К)

Нёсравнение трех разрядов (Д)

2C

3M

Несравнение двух Тройная оши&- Не корректируется разрядов (К) и ка трех разрядов (Д)

IM

3M

Несравнение двух разрядов (К) и одного разряда(Д)

Несравнение трех разрядов (К) и трех разрядов (Д)

IM

Несравнение трех разрядов (К) и одного разряда (Д)

1C

3M

Несравнение трех разрядов (Д) и одного разряда(К)

1C

2M

Несравнение 1-го разряда (К) и 2-х разрядов (Д)

ряд (Д)

Корректируется ин4 разряд или (К) раз ряд

Не корректируется

Не корректируется

Не корректируется

Тройная ошиб- Не корректируется

ка

Корректируется три информационных разряда или (К) разряды

Корректируется три информационных разряда или два информационных разряда и один (К) разряд

Корректируется три информационных разряда или два информационных разряда и один (К) разряд

Двойная ошиб- Не корректируется ка

Формула изобретени

Запоминающее устройство с обнаружением и коррекцией ошибок, содержащее регистр адреса, счетчик, информационные регистры сдвига, первый контрольный регистр сдвига, первый формирователь сигналов четности, блок сравнения, дешифраторы, блок управления, блок коррекции и накопитель, состоящий из информационной и основной контрольной частей, причем первый вход блока управления является первым управляющим входом устройства, вторым управляющим входом которого являются второй вход блока управления и управляющий вход регистра адреса, вход которого и третий вход блока управления являются соответственно адресным и тактовым входами устройства, выходы регистра адреса и счетчика подключень к адресным входам накопителя, одни из выходов информационных регистров сдвига соединены с информационнь1ми входами на- копителя и входами первой группы блока коррекции, вход которого и контрольный вход основного накопителя подключены к одному из выходов первого контрольного регистра сдвига, первый выход блока управления соединены с установочными входами информацион-

ных и первого контрольного регист- ров сдвига, другие выходы которых подключены соответственно ко входам первого формирователя сигналов четности и ко входам первой группы блока сравнения, входы второй группы которого соединены с выходами первого формирователя сигналов четности, а одни из выходов - со входами первого и второго дешифраторов, вход и выходы счетчика подключены соответственно ко второму выходу и к чет .вертому входу блока управления, тре- тий и четвертый выходы которого соединены с управляющими входами накопителя , информационными и контрольto

5 0

20

5

0

5

ным выходами устройства являются выходы блока коррекции, первый выход первого дешифратора является первым индикаторным выходом устройства, о т- личающееся тем, что, с целью повышения достоверности контроля и упрощения устройства, в него введены второй формирователь сигналов четности, второй контрольный регистр сдвига, дополнительная контрольная часть накопителя, селектор и

. мультиплексор, входы и выходы которого подключены соответственно к вы- второго дешифратора и ко вхо 5 дам второй группы блока коррекции, а управляюпше входы - соответственно ко второму выходу первого дешифратора и к пятому выходу блока управления, первый и шестой выходы которого соединены с установочными входами второго контрольного регистра сдвига, одни из выходов и входов которого подключены соответств енно ко входу и Ki выходу дополнительной контрольной части накопителя, другие выходы и входы второго контрольного регистра сдвига подключены соответственно ко входам третьей группы блока сравнения, к выходам второго фор- ьшрователя сигналов четности и входам четвертой группы блока сравнения, входы второго формирователя сигналов четности подключены к другим выходам информационных и первого контрольного регистров сдвига, входы которых соединены с выходами селектора, одни из входов которого соединены с информационными и контрольным выходами накопителя, другие входы селектора являются информационными и контрольным входами устройства, а управляющий вход подключен к первому входу блока управления, седьмой выход которого соединен с управляющим входом блока сравнения, другой выход которого является вторым индикаторным выходом устрой-, ства.

i

гг

69

Редактор Ю.Середа

Заказ 5031/51Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раущская наб., д.4/5

Производственно-полиграфичсское предприятие,г.Ужгород,ул.Проектная,4

Л. «f

х я

Иез

Т}

фиг г

US

Составитель Т.Зайцева

Техред И.Поповнч Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1236559A1 |

| Запоминающее устройство с коррекцией ошибок | 1978 |

|

SU744740A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является повьшение достоверности контроля и упрощение устройства. Устройство содержит регистр адреса, счетчик, блок управления, информационные регистры сдвига, первый контрольный регистр сдвига, первый формирователь сигналов четности, блок сравнения, два дешифратора, блок коррекции, накопитель, состоящий из информационной и основной контрольной частей, в который введена дополнительная контрольная часть, а также вновь введенные селектор, второй контрольный регистр сдвига, второй формирователь сигналов четности и мультиплексор. Второй формирователь сигналов четности формирует контрольные сигналы,которые записываются в разрядах информационных слов по диагонали, что позволяет обнаруживать тройные ошибки в накопителе и тем самым повысить достоверность контроля. При этом число контрольных разря- flOB в слове не зависит от разрядности слова и всегда равно двум, за счет чего упрощается контрольная часть нако1штеля и уменьшается число контрольЩ)х регистров сдвига, что позволяет упростить устройство. 2 ил. 1 табл. с S (Л о со

| Computer Design, 1981, 20 № 7, P.I43-K8 | |||

| Проблемь передачи информации, Т.XX, ВЫП.1, 1984,.с.19-21. |

Авторы

Даты

1986-09-15—Публикация

1985-03-26—Подача