сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1990 |

|

SU1742991A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1723669A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1723668A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1723670A1 |

| Логический элемент | 1990 |

|

SU1742990A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1716600A1 |

| Логический элемент на переключении тока | 1988 |

|

SU1631714A1 |

| Схема на переключении тока | 1990 |

|

SU1798917A1 |

| Логический элемент "Исключающее ИЛИ" | 2022 |

|

RU2792407C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ИСКЛЮЧАЮЩЕЕ ИЛИ» | 2022 |

|

RU2795286C1 |

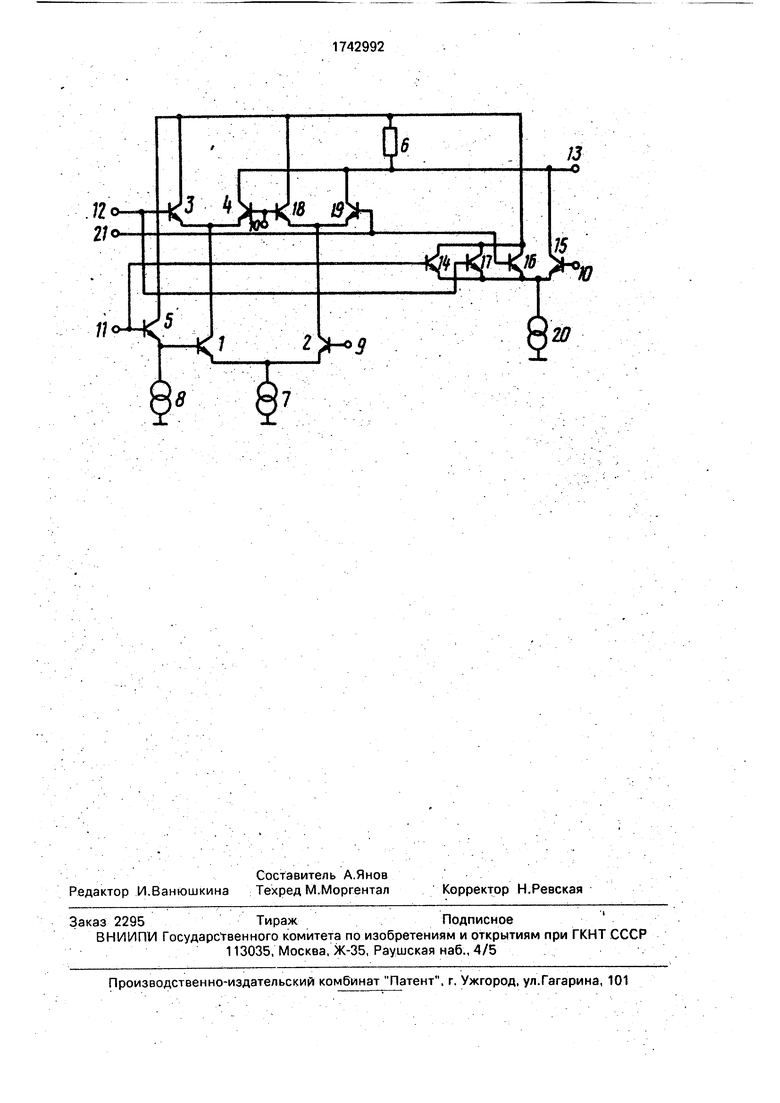

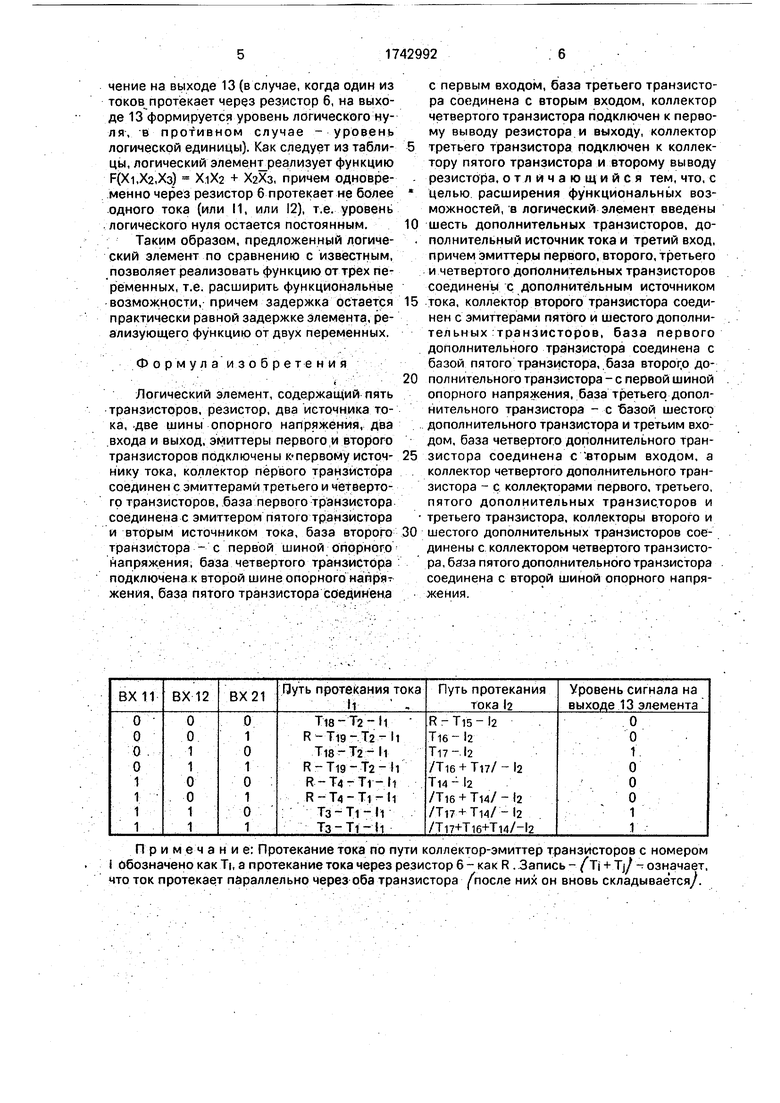

Изобретение относится к импульсной технике и позволяет расширить функциональные возможности логического элемента. Сущность изобретения: логический элемент содержит первый 1, второй 2, третий 3, четвертый 4 и пятый 5 транзисторы, резистор 6, первый 7 и второй 8 источники тока, первую 9 и вторую 10 шины опорного напряжения, первый 11 и второй 12 входы, выход 13 первый 14, второй 15, третий 16, четвертый 17, пятый 18 и шестой 19 допол- нительные транзисторы, дополнительный источник тока 20 и третий вход 21. 1 ил.

Изобретение относится к импульсной технике, в частности к логическим элементам на переключении тока, и может быть использовано в сверхскоростных интегральных схемах для построения комбинационной части логических схем.

Известны элементы, выполненные из двух и более токовых ключах, с двумя уровнями переключения тока, причем максимальная задержка таких схем примерно равна задержке одного токозого ключа.

Однако в элементе, построенном данным образом, через резистор, формирующий логический перепад, может одновременно протекать 0, 1, 2 и более токов токовых ключей. Для стабилизации уровня логического нуля в элемент введен параллельно этому резистору ограничительный диод, что, однако, не позволяет сохранять достаточно стабильный уровень логического нуля в элементе и приводит к увеличению задержки.

Наиболее близким по технической сущности является логический элемент, реализующий функцию F (XiXz) Xi Ха на двух уровнях переключения тока, т.е. формирует функцию, являющуюся частным случаем требуемой при Хз 0. Недостатком этого элемента является невозможность реализации фун кции F (Xi ,X2iX3)XiX2 + ХаХз от трех переменных, каждая из которых отлична от const.

Цель изобретения - расширение,функциональных возможностей логического элемента.

Поставленная цель достигается тем, что в логический элемент, содержащий пять транзисторов, резистор, два источника тоХ|

ю о ю

го

ка, две шины опорного напряжения, два входа и выход, эмиттеры первого и второго транзисторов, подключены к первому источнику тока, коллектор первого транзистора соединен с эмиттерами третьего и четвертого транзисторов, база первого транзистора соединена с эмиттером пятого транзистора и вторым источником тока, база второго транзистора - с первой шиной опорного напряжения, база четвертого транзистора подключена к второй шине опорного напряжения, база пятого транзистора соединена с первым входом, база третьего транзистора соединена с вторым входом, коллектор четвертого транзистора подключен к первому выводу резистора и выходу, коллектор третьего транзистора подключен к коллектору пятого транзистора и второму выводу резистора, введены шесть дополнительных транзисторов, дополнительный источник тока и третий вход, эмиттеры первого, второго,третьего и четвертого дополнительных транзисторов соединены с дополнительным источником тока, коллектор второго транзистора соединен с эмиттерами пятого и шестого дополнительных транзисторов, база первого дополнительного транзистора соединена с базой пятого транзистора, база второго дополнительного транзистора - с первой шиной опорного напряжения, база третьего дополнительного транзистора - с базой шестого дополнительного транзистора и третьим входом, база четвертого дополнительного транзистора соединена с вторым входом, а коллектор четвертого дополнительного транзистора - с коллекторами первого, третьего, пятого дополнительных транзисторов и третьего транзистора, коллекторы второго и шестого дополнительных транзисторов соединены с коллектором четвертого транзистора, база пятого дополнительного транзистора соединена с второй шиной опорного напряжения

Предложенный логический элемент обладает новизной и существенными отличиями, Введение дополнительных элементов, указанных в формуле изобретения, позволяет реализовать функцию Р(Х-|,Х2,Хз) XiXa+ + Х2Хз, причем через резистор протекает одновременно не более одного тока первого источника тока или дополнительного ис- точника тока, поэтому не требуется подключения ограничительного диода, а задержка практически равна задержке элемента, реализующей функцию F(Xi,X2) Xix

ХХ2.

На чертеже представлена электрическая схема логического элемента, реализующего функцию Р(Х1,Х2,Хз) XiX2 + Х2Хз.

Логический элемент, реализующий функцию Р(Х1,Х2,Хз) XiX2 + Х2Хз, содержит пять транзисторов 1-5, резистор б, два источника тока 7,8, две шины опорного напряжения 9, 10, два входа 11, 12 и выход 13, эмиттеры первого и второго транзисторов 1, 2 подключены к первому источнику токз 7, коллектор первого транзистора 1 соединен с эмиттерами третьего и четвертого транзи0 сторов 3, 4, база первого транзистора 1 соединена с эмиттером пятого транзистора 5 и вторым источником тока 8, база второго транзистора 2-е первой шиной опорного напряжения 9, база четвертого транзистора

5 4 подключена к второй шине опорного напряжения 10, база пятого транзистора 5 соединена с первым входом 11, база третьего транзистора 3 соединена с вторым входом 12, коллектор четвертого транзистора 4 под0 ключей к первому выводу резистора 6 и выходу 13, коллектор третьего транзистора 3 подключен к коллектору пятого транзистора 5 и второму выводу резистора 6. Согласно изобретению в логический элемент введены

5 шесть дополнительных транзисторов 14-19, дополнительный источник тока 20, третий вход 21, причем эмиттеры первого, второго, третьего и четвертого дополнительных транзисторов 14-17, соединены с дополни0 тельным источником тока 20, коллектор второго транзистора 2 соединен с эмиттерами пятого и шестого дополнительных транзисторов 18, 19, база первого дополнительного транзистора 14 соединена с базой пятого

5 транзистора 5,база второго дополнительного транзистора 15 - с первой шиной опорного напряжения 9, база третьего дополнительного транзистора 16 - с базой шестого дополнительного транзистора 19 и

0 третьим входом 21, база четвертого дополнительного транзистора 17 соединена с вторым 12 входом, а коллектор четвертого дополнительного транзистора 17-с коллекторами первого 14, третьего 16, пятого до5 полнительных транзисторов 14, 16, 18 и третьего транзистора 3, коллекторы второго и шестого дополнительных транзисторов 15, 19 соединены с коллектором четвертого транзистора 4, база пятого дополнительно0 го транзистора 18 соединена с второй шиной опорного напряжения 10.

Предложенный логический элемент функционирует следующим образом.

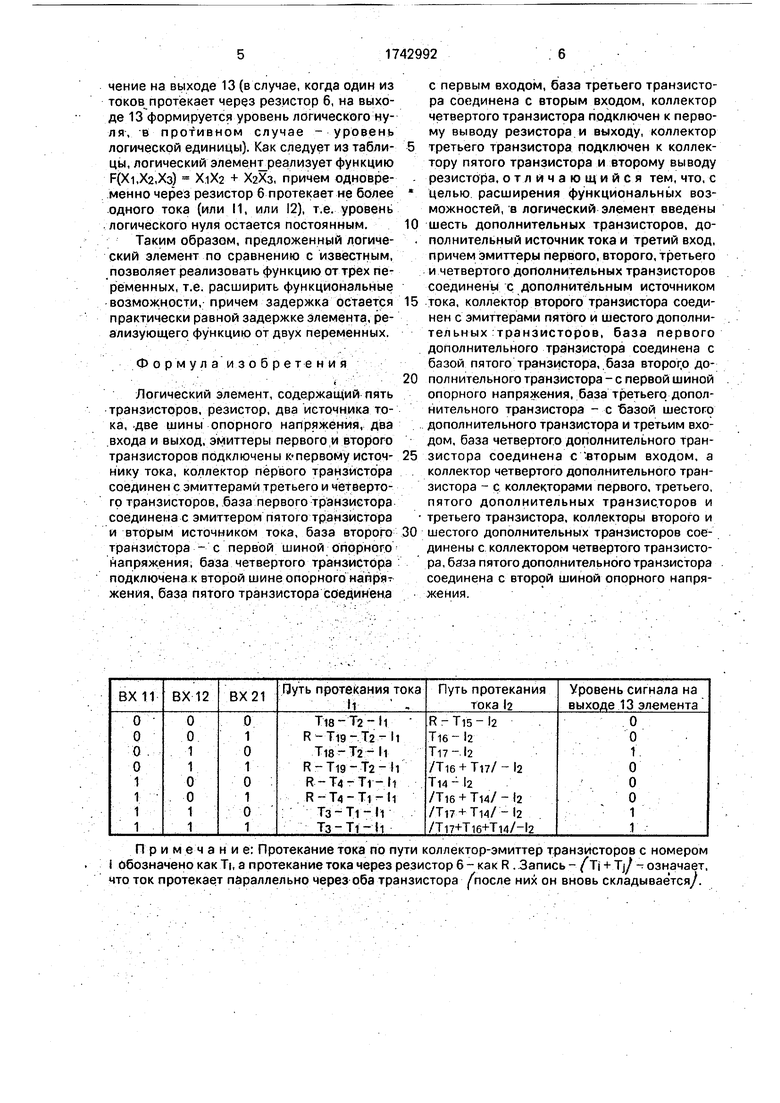

На входы 11, 12, 21 подаются сигналы,

5 соответствующие уровню логического нуля или единицы. В таблице представлены пути протекания токов первого источника тока 7 (Н) и дополнительного источника тока 20 02) при различных комбинациях входных сигналов (всего комбинаций 2 ± 8), а также значение на выходе 13 (в случае, когда один из токов протекает через резистор 6, на выходе 13 формируется уровень логического нуля, в противном случае - уровень логической единицы). Как следует из таблицы, логический элемент реализует функцию F(Xi,X2,Xs) XiX2 + Х2Хз, причем одновременно через резистор 6 протекает не более одного тока (или И, или 12), т.е. уровень логического нуля остается постоянным.

Таким образом, предложенный логический элемент по сравнению с известным, позволяет реализовать функцию от трех переменных, т.е. расширить функциональные возможности, причем задержка остается практически равной задержке элемента, реализующего функцию от двух переменных.

Формула изобретения

t

Логический элемент, содержащий пять транзисторов, резистор, два источника тока, две шины опорного напряжения, два входа и выход, эмиттеры первого и второго транзисторов подключены к-первому источнику тока, коллектор первого транзистора соединен с эмиттерами третьего и четвертого транзисторов, база первого транзистора соединена с эмиттером пятого транзистора и вторым источником тока, база второго транзистора - с первой шиной опорного напряжения, база четвертого транзистора подключена к второй шине опорного напряжения, база пятого транзистора соединена

Примечание: Протекание тока по пути коллектор-эмиттер транзисторов с номером i обозначено как Т|, а протекание тока через резистор 6 - как R . Запись - ( + Tj/ - означает, что ток протекает параллельно через оба транзистора Дюсле них он вновь складывается/.

с первым входом, база третьего транзистора соединена с вторым входом, коллектор четвертого транзистора подключен к первому выводу резистора и выходу, коллектор

третьего транзистора подключен к коллектору пятого транзистора и второму выводу резистора, отличающийся тем, что, с

целью расширения функциональных возможностей, в логический элемент введены

шесть дополнительных транзисторов, дополнительный источник тока и третий вход, причем эмиттеры первого, второго, третьего и четвертого дополнительных транзисторов соединены с дополнительным источником

тока, коллектор второго транзистора соединен с эмиттерами пятого и шестого дополни- тельных транзисторов, база первого дополнительного транзистора соединена с базой пятого транзистора, база второгр дополнительного транзистора - с первой шиной опорного напряжения, база третьего дополнительного транзистора - с Вазой шестого дополнительного транзистора и третьим входом, база четвертого дополнительного транзистора соединена с вторым входом, а коллектор четвертого дополнительного транзистора - с коллекторами первого, третьего, пятого дополнительных транзисторов и третьего транзистора, коллекторы второго и

шестого дополнительных транзисторов соединены с коллектором четвертого транзистора, база пятого дополнительного транзистора соединена с второй шиной опорного напряжения

Я

| Микросхемы интегральные | |||

| Нагревательный прибор для жидкости | 1913 |

|

SU1520A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Алексеенко А.Г., Шагурин И.И | |||

| Микросхемотехника - М.: Радио и связь, 1982, с, 77, рис.2.24. | |||

Авторы

Даты

1992-06-23—Публикация

1990-01-24—Подача