Изобретение относится к импульснрй технике, в частности к логическим элементам на переключении тока, и может быть использовано в сврехскоростных интегральных схемах для построения комбинационной части логических схем.

В ряде случаев при построении ЭСЛ--эле- мента, выполненного на двух уровнях переключения тока, требуется реализовать функцию Y Xi -X2 Хз, причем задержка переключения от любой переменно при этом должна б,ыть минимальна.

Известен метод построения функций трех переменных на одном переключаемом токе при трех ярусах его переключения, од- , задержка сигнала, подаваемого на

нижний ярус, оказывается значительно больше задержки прохождения сигнала, подаваемого на верхний ярус.

Кроме того, значительное число БМК ЭСЛ-типа ориентировано на два уровня переключения тока, что также заставляет ограничиваться двумя уровнями.

Известны элементы, выполненные на двух и более токовых ключах, с двумя уровнями переключения тока, причем максимальная задержка таких элементов примерно равна задержке одного токового ключа.

Однако в элементе, построенном данным образом, через резистор, формирующий логический перепад, может

о о о о

одновременно протекать 0, 1, 2 и более токов токовых ключей. Для стабилизации уровня логического нуля в элемент введен параллельно этому резистору ограничительный диод, что, однако, не позволяет сохранять достаточно стабильный уровень логического нуля в элементе и приводит к увеличению задержки.

Наиболее близким по технической сущности является элемент, реализующий функцию Y Xi Х2 на двух уровнях переключения тока, т.е. он формирует функцию, являющуюся частным случаем требуемой при Хз 1.

Недостатком этого элемента является невозможность реализации функции Y Xi x Х2 Хз от трех переменных, каждая из которых отлична от const.

Целью изобретения является расширение функциональных возможностей логического элемента при переключении тока путем реализации функции трех переменных.

Поставленная цель-достигается тем, что в логический элемент на переключении тока, содержащий пять транзисторов, резистор, два источника тока, две шины опорного напряжения, два входа и выход, причем первый и второй транзисторы выпол-. нены с объединенными эмиттерами, которые подключены к первому источнику тока, коллектор первого транзистора соединен с эмиттерами третьего и четвертого транзисторов, база первого транзистора соедине- на с эмиттером пятого и с вторым источником тока, база второго - с первой шиной опорного напряжения, база четвертого транзистора подключена к второй шине опорного напряжения( база пятого транзистора соединена-с первым входом элемента, база третьего транзистора соединена с вторым входом элемента, коллектор четвертого транзистора подключен к первому выводу резистора и к выходу элемента, коллектор третьего транзистора подключен к коллектору пятого транзистора и второму выводу резистора, согласно изобретению, введены десять дополнительных транзисторов, два дополнительных источника тока, третий вход элемента, причем эмиттеры первого и второго дополнительных тран- зисторов объединены с первым дополнительным источником тока, коллектор первого дополнительного транзистора соединен с объединенными эмиттерами третьего и четвертого дополнительных транзисторов, база первого дополнительного транзистора соединена с эмиттером пятого дополнительного транзистора и вторым дополнительным источником тока, база второго дополнительного транзистора - с первой шиной опорного напряжения, база третьего дополнительного

транзистора - с базами шестого и седьмого дополнительных транзисторов и с третьим входом элемента, а коллектор - с коллекторами шестого, восьмого, пятого, десятого дополнительных и третьего транзисторов,

базы четвертого, девятого и десятого дополнительных транзисторов соединены с второй шиной опорного напряжения, а коллектор четвертого дополнительного транзистора - с коллекторами седьмого и

девятого дополнительных и четвертого

транзисторов, эмиттеры шестого, восьмого

и девятого дополнительных транзисторов

соединены с коллекторами второго допол-нительнрго транзистора, а эмиттеры седьмого и десятого дополнительных транзисторов - с коллектором второго транзистора, база пятого дополнительного транзистора соединена с вторым входом элемента, а база восьмого дополнительного

транзистора - с первым входом элемента.

Введение дополнительных элементов позволяет реализовать функЦию Y Xi -Х2« «Хз, причем через резистор протекает одновременно не более одного тока первого источника тока или первого дополнительного источника тока, и поэтому не требуется подключения ограничительного диода, а задержка практически равна задержке схемы, реализующей функцию

F(Xi, X2) Xi -Х2.

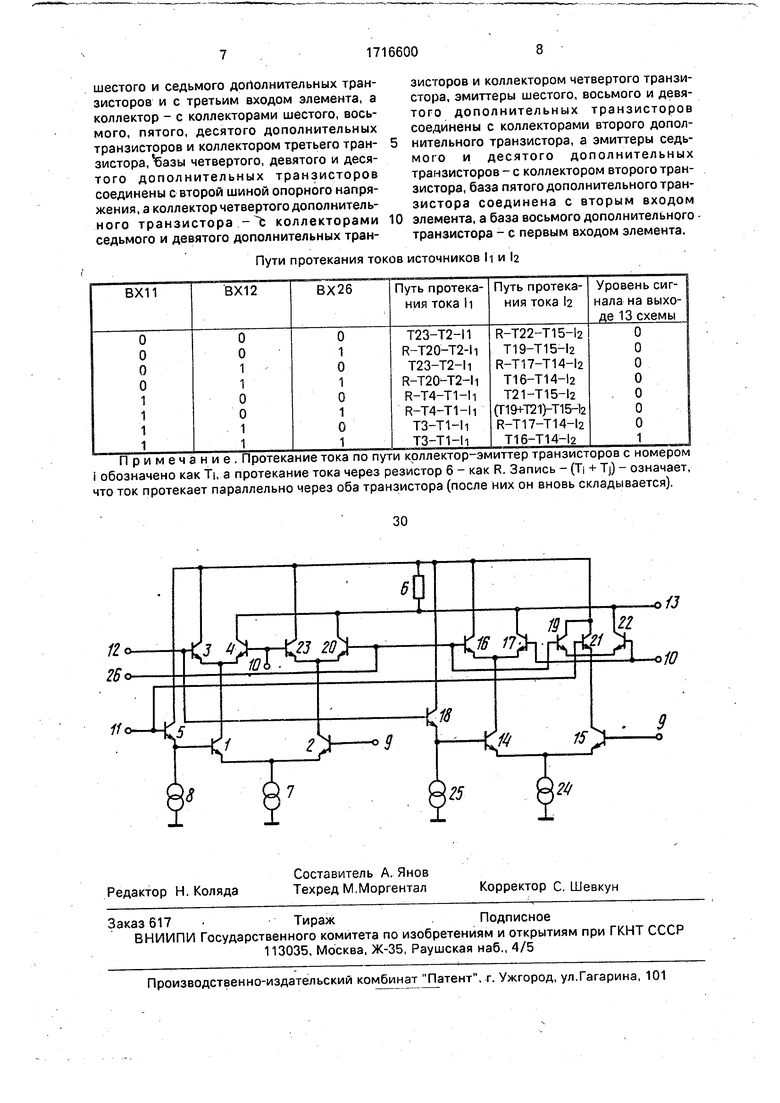

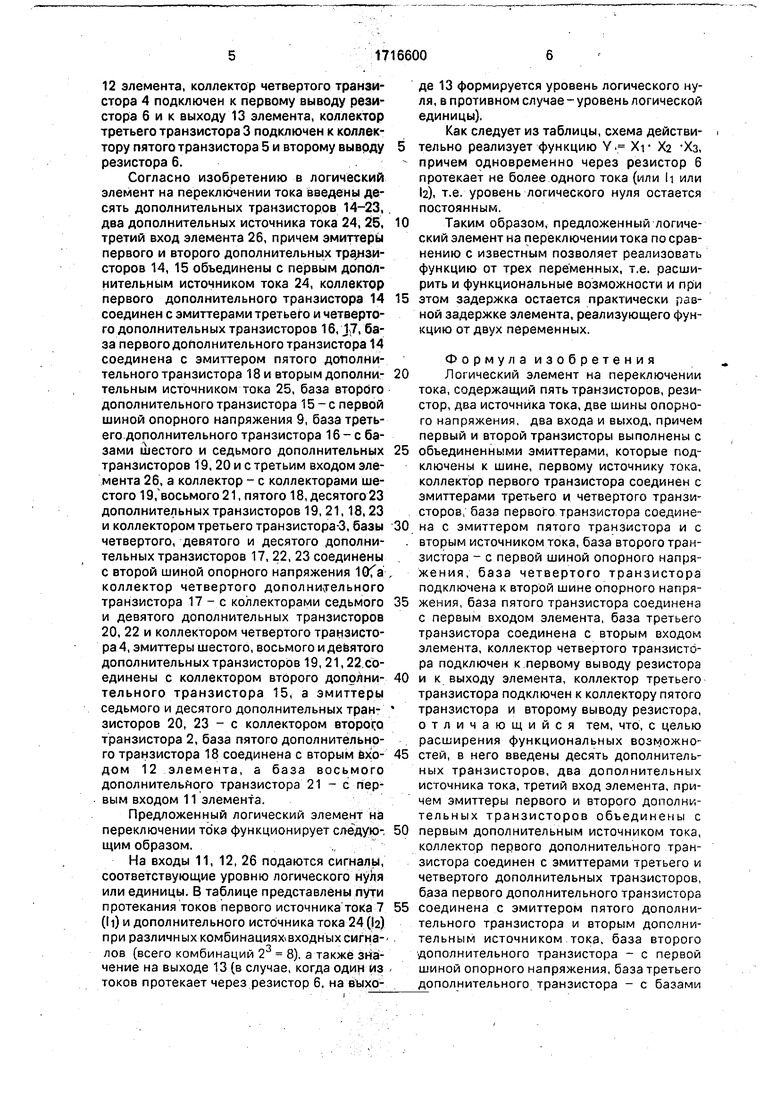

На чертеже представлена электрическая схема предложенного логического элемента на переключении тока, реализующего функцию

Y Хг Х2 -Хз.

Логический элемент на переключении тока содержит пять транзисторов 1-5, резистор 6, два источника тока 7, 8, две шины опорного напряжения 9,10, два входа 11,12

, и выход 13, причем первый и второй транзисторы 1, 2 выполнены с объединенными эмиттерами, которые подключены к первому источнику тока 7, коллектор первого транзистора 1 соединен с эмиттерами третьего и четвертого транзисторов 3, 4, база первого транзистора 1 соединена с эмиттером пятого транзистора 5 и с вторым источником тока 8, база второго транзистора 2 - с первой шиной опорного напряжения 9, база четвертого транзистора 4 подключена к второй шине опорного напряжения 10, база пятого транзистора 5 соединена с первым входом 11 элемента, база третьего транзистора 3 соединена с вторым входом

12 элемента, коллектор четвертого транзистора 4 подключен к первому выводу резистора 6 и к выходу 13 элемента, коллектор третьего транзистора 3 подключен к коллектору пятого транзистора 5 и второму выводу резистора 6..

Согласно изобретению в логический элемент на переключении тока введены десять дополнительных транзисторов 14-23, два дополнительных источника тока 24, 25, третий вход элемента 26, причем эмиттеры первого и второго дополнительных тра,нзи- сторов 14, 15 объединены с первым дополнительным источником тока 24, коллектор первого дополнительного транзистора 14 соединен с эмиттерами третьего и четвертого дополнительных транзисторов 16, . база первого дополнительного транзистора 14 соединена с эмиттером пятого дополнительного транзистора 18 и вторым дополни- тельным источником тока 25, база вторбго дополнительного транзистора 15 - с первой шиной опорного напряжения 9, база третьего дополнительного транзистора 16 - с базами шестого и седьмого дополнительных транзисторов 19, 20 и с третьим входом элемента 26, а коллектор - с коллекторами шестого 19, восьмого 21, пятого 18, десятого 23 дополнительных транзисторов 19, 21,18,23 и коллектором третьего транзистора-3, базы четвертого, девятого и десятого дополнительных транзисторов 17, 22, 23 соединены с второй шиной опорного напряжения 10fa коллектор четвертого дополнительного транзистора 17 - с коллекторами седьмого и девятого дополнительных транзисторов 20, 22 и коллектором четвертого транзистора 4, эмиттеры шестого, восьмого и девятого дополнительных транзисторов 19, 21,22.соединены с коллектором второго дополни- тельного транзистора 15, а эмиттеры седьмого и десятого дополнительных тран- зисторов 20, 23 - с коллектором второг.о транзистора 2, база пятого дополнительного транзистора 18 соединена с вторым вхо- дом 12 элемента, а база восьмого дополнительного транзистора 21 - с riep вым входом 11 элемента.

Предложенный логический элемент на переключении тока функционирует следую- щим образом..,

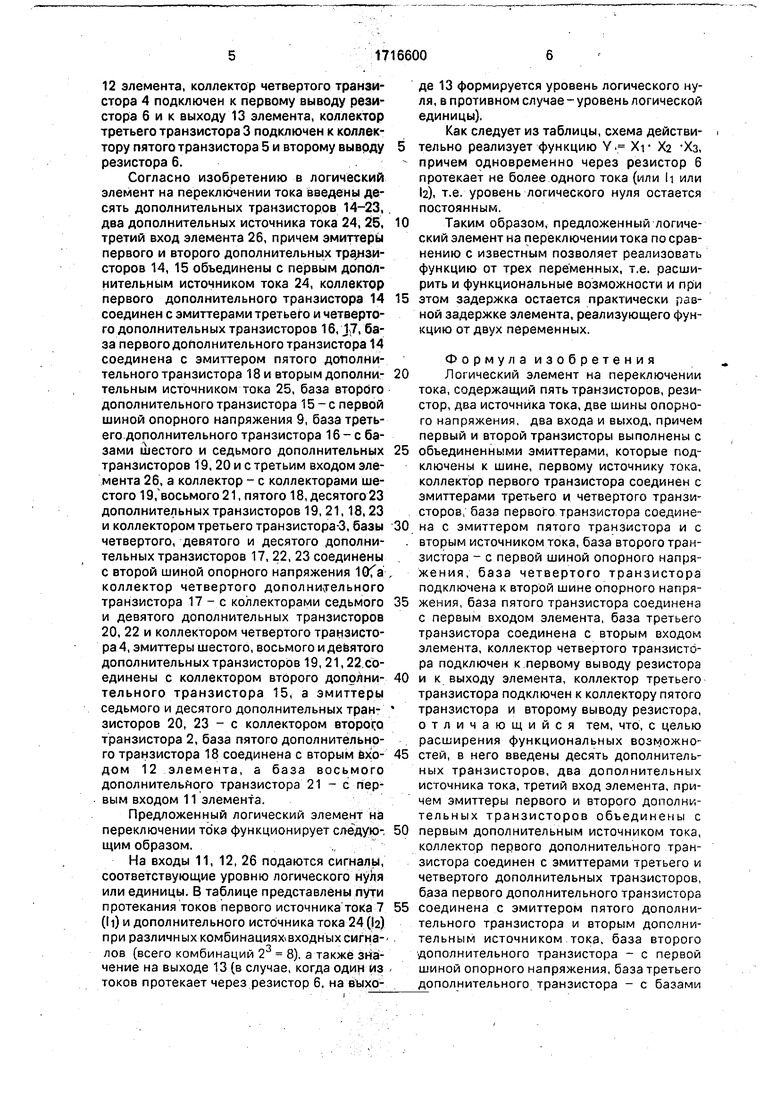

На входы 11, 12, 26 подаются сигналы, соответствующие уровню логического нудя или единицы. В таблице представлены пути протекания токов первого источника тока 7 (И) и дополнительного источника тока 24 ((а) при различных комбинацияжвходныхсигналов (всего комбинаций 23 8), а также значение на выходе 13 (в случае, когда один из токов протекает через резистор 6, на выходе 13 формируется уровень логического нуля, в противном случае - уровень логической единицы),

Как следует из таблицы, схема действительно реализует функцию Y. Xr /2 -Хз, причем одновременно через резистор 6 протекает не более одного тока (или И или 12), т.е. уровень логического нуля остается постоянным.

Таким образом, предложенный логический элемент на переключении тока по сравнению с известным позволяет реализовать функцию от трех переменных, т.е. расширить и функциональные возможности и при этом задержка остается практически разной задержке элемента, реализующего функцию от двух переменных.

Формула изобретения Логический элемент на переключении тока, содержащий пять транзисторов, резистор, два источника тока, две шины опорного напряжения, два входа и выход, причем первый и второй транзисторы выполнены с объединенными эмиттерами, которые подключены к шине, первому источнику тока, коллектор первого транзистора соединен с эмиттерами третьего и четвертого транзисторов; база первого транзистора соединена с эмиттером пятого транзистора и с вторым источником тока, база второго транзистора - с первой шиной опорного напряжения, база четвертого транзистора подключена к второй шине опорного напряжения, база пятого транзистора соединена с первым входом элемента, база третьего транзистора соединена с вторым входом элемента, коллектор четвертого транзистора подключен к первому выводу резистора и к выходу элемента, коллектор третьего транзистора подключен к коллектору пятого транзистора и второму выводу резистора, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены десять дополнительных транзисторов, два дополнительных источника тока, третий вход элемента, причем эмиттеры первого и второго дополнительных транзисторов объединены с первым дополнительным источником тока, коллектор первого дополнительного транзистора соединен с эмиттерами третьего и четвертого дополнительных транзисторов, база первого дополнительного транзистора соединена с эмиттером пятого дополнительного транзистора и вторым дополнительным источником тока, база второго дополнительного транзистора - с первой шиной опорного напряжения, база третьего дополнительного транзистора - с базами

шестого и седьмого дополнительных транзисторов и с третьим входом элемента, а коллектор - с коллекторами шестого, восьмого, пятого, десятого дополнительных транзисторов и коллектором третьего транзистора, базы четвертого, девятого и десятого дополнительных транзисторов соединены с второй шиной опорного напряжения, а коллектор четвертого дополнительного транзистора коллекторами седьмого и девятого дополнительных тран0

зисторов и коллектором четвертого транзистора, эмиттеры шестого, восьмого и девятого дополнительных транзисторов соединены с коллекторами второго дополнительного транзистора, а эмиттеры седьмого и десятого дополнительных транзисторов - с коллектором второго транзистора, база пятого дополнительного транзистора соединена с вторым входом элемента, а база восьмого дополнительного транзистора - с первым входом элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент на переключении тока | 1990 |

|

SU1723669A1 |

| Логический элемент на переключении тока | 1988 |

|

SU1631714A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1723668A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1723670A1 |

| Логический элемент | 1990 |

|

SU1742990A1 |

| Логический элемент | 1990 |

|

SU1742991A1 |

| Триггер | 1983 |

|

SU1132343A1 |

| Логический элемент "Исключающее ИЛИ" | 2022 |

|

RU2792407C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ИСКЛЮЧАЮЩЕЕ ИЛИ» | 2022 |

|

RU2795286C1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

Изобретение относится к импульсной технике, в частности к логическим элементам на переключении тока, и может быть использовано в сверхскоростных интегральных схемах для построения комбинаци- онной части логических схем. Цель изобретения - расширение функциональных возможностей логического элемента на переключении тока, путем реализации функции трех переменных. Логический элемент на переключении тока содержит пять транзисторов, резистор, два источника тока, две шины опорного напряжения, три входа, выход, десять дополнительных транзисторов и два источника тока. Введение десяти дополнительных транзисторов, двух.дополнитель- ных источников тока и третьего входа позволяет расширить функциональные возможности логического элемента за счет реализации функции трех переменных Y Xi «Ха-Хз, при обеспечении максимального быстродействия и сохранении стабильности уровня логического нуля на выходе без использования диодного фиксатора потенциалов. 1 ил. (Л

Пути протекания токов источников И и 2

Примечание. Протекание тока по пути коллектор-эмиттер транзисторов с номером i обозначено как Ть а протекание тока через резистор 6 - как R. Запись - (Ti + Tj) - означает, что ток протекает параллельно через оба транзистора (после них он вновь складывается).

#о

| Алексенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, с | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Микросхемы интегральные | |||

| Нагревательный прибор для жидкости | 1913 |

|

SU1520A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Руководящий документ | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

| Кран машиниста для автоматических тормозов с сжатым воздухом | 1921 |

|

SU194A1 |

Авторы

Даты

1992-02-28—Публикация

1990-01-24—Подача