со

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент на переключении тока | 1990 |

|

SU1723670A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1716600A1 |

| Логический элемент | 1990 |

|

SU1742991A1 |

| Логический элемент на переключении тока | 1988 |

|

SU1631714A1 |

| Логический элемент | 1990 |

|

SU1742992A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1723669A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1723668A1 |

| Схема на переключении тока | 1990 |

|

SU1798917A1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

Изобретение относится к импульсной технике и позволяет расширить функциональные возможности логического элемента. Сущность изобретения: логический элемент содержит первый 1, второй 2, третий 3, четвертый 4 и пятый 5 транзисторы, резистор 6, первый 7 и второй 8 источники тока, первую и вторую 10 шины опорного напряжения, первый 11 и второй 12 входы, выход 13, первый 14, второй 15, третий 16, четвертый 17, пятый 18, шестой 19 и седьмой 20 дополнительные транзисторы, дополнительный источник тока 21 и третий вход 22. 1 ил.

Изобретение относится к импульсной технике, в частности к логическим элементам на переключении тока, и может быть использовано в сверхскоростных интегральных схемах для построения комбинационной части логических схем.

Известные логические элементы, выполненные на двух и более токовых ключах, с двумя уровнями переключения тока, причем максимальная задержка таких схем примерно равна задержке одного токового ключа. Однако в элементе, построенной данным образом, через резистор, формирующий логический перепад, может одновременно протекать 0, 1, 2 и более токов

токовых ключей. Для стабилизации уровня логического нуля в элемент введен параллельно этому резистору ограничительный диод, что, однако, не позволяет сохранять достаточно стабильный уровень логического нуля в элементе и приводит к увеличению задержки.

Наиболее близкой по технической сущности является логический элемент, реализующий функцию F(Xi, Х2) Xi + Х2 на двух уровнях переключения тока, т.е. формирует функцию, являющуюся частным случаем требуемой при Хз 1. Недостатком этого элемента является невозможность реализа- ции функции F(Xi, Х2, Хз) (Xi + Х2) Хз от

vi N ю чэ ю о

трех переменных, каждая из которых отлична от const.

Цель изобретения - расширение функциональных возможностей логического элемента.

Поставленная цель достигается тем, что в логический элемент на переключении тока, содержащий пять транзисторов, резистор, два источника тока, две шины опорного напряжения, два входа и выход, эмиттеры первого и второго транзисторов подключены к первому источнику тока, коллектор первого транзистора соединен с эмиттерами третьего и четвертого транзисторов, база первого транзистора соединена с эмиттером пятого транзистора и вторым источника тока, база второго транзистора - с первой шиной опорного напря- жения, база четвертого транзистора подключена к второй шине опорного напряжения, база пятого транзистора соединена с первым входом, база третьего транзистора соединена с вторым входом, первый вывод резистора подключен к выходу, коллектор пятого транзистора подключен к второму выводу резистора, введены семь дополнительных транзисторов, дополнительный источник тока и третий вход, причем эмиттеры первого и второго дополнительных транзисторов соединены с дополнительным источником тока, база первого дополнительного транзистора соединена с базой первого транзистора ,база второго дополнительного транзистора - с первой шиной опорного напряжения, базы третьего и шестого дополнительных транзисторов соединены с третьим входом, база четвертого допол- нительного транзистора соединена с вторым входом, а коллектор четвертого дополнительного транзистора с коллекторами седьмого дополнительного транзистора и четвертого транзистора и выходом, коллекторы второго, третьего, пятого и шестого дополнительных транзисторов соединены с коллекторами третьего и пятого транзисторов, базы пятого и седьмого дополнительных транзисторов соединены с второй шиной опорного напряжения, эмиттеры четвертого и пятого дополнительных транзисторов соединены с коллектором первого дополнительного транзистора, эмиттер третьего дополнительного транзистора соединен с эмиттером третьего транзистора, коллектор второго транзистора соединен с эмиттерами шестого и седьмого дополнительных транзисторов.

Введение дополнительных элементов позволяет реализовать функцию F(Xi, X2, Хз) ( + Xa)-X3, причем через резистор протекает одновременно не более одного тока первого источника тока или дополнительного источника тока, поэтому не требуется подключения ограничительного диода, а задержка практически равна задержке схемы, реализующей функцию F(Xi,X2) Xi + .

Ни одного известного логического элемента, позволяющего реализовать аналогичную функцию аналогичным образом, нами не обнаружено.

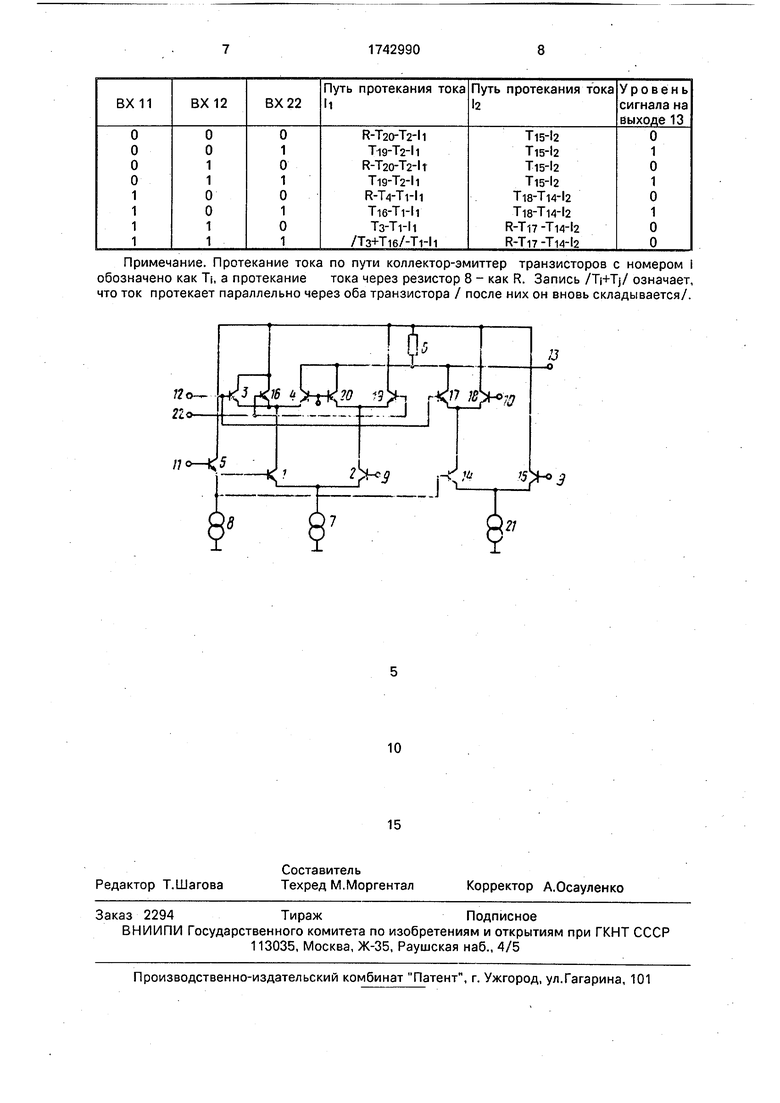

На чертеже представлена электрическая схема логического элемента, реализующего функцию

F(Xi,X2,X3) (Xi+X2) -Хз.

Логический элемент, реализующий функцию F(Xi, X2, Хз) (Xi + Ха) -Хз, содержит пять транзисторов 1-5, резистор 6, два источника 7, 8, две шины опорного напряжения 9, 10, два входа 11, 12 и выход 13. Эмиттеры первого и второго транзисторов 1, 2 подключены к первому источнику тока 7. Коллектор первого транзистора 1 соединен с эмиттерами третьего и четвертого

транзисторов 3, 4. База первого транзистора 1 соединена с эмиттером пятого транзистора 5 и вторым источником тока 8. База второго транзистора 2 соединена с первой шиной опорного напряжения 9. База

четвертого транзистора 4 подключена к второй шине опорного н а - пряжения 10. База пятого транзистора 5 соединена с первым входом 11. База третьего транзистора 3 соединена с вторым входом

третьего и пятого транзисторов 3, 5, база пятого и седьмого дополнительных транзисторов 18, 20 соединены с второй шиной опорного напряжения 10, эмиттеры четвертого и пятого дополнительных транзисторов 17, 18 соединены с коллекторами первого дополнительного транзистора 14, эмиттер третьего дополнительного транзистора 16 соединен с эмиттером третьего транзистора 3, коллектор второго транзистора 2 соединен с эмиттерами шестого и седьмого дополнительных транзисторов 19, 20.

Предложенный логический элемент функционирует следующим образом.

На входы 11, 12, 22 подаются сигналы, соответствующие уровню логического нуля или единицы. В таблице представлены пути протекания токов первого источника тока 7 (И) и дополнительного источника тока 21 (12) при различных комбинациях входных сигналов (всего комбинаций ),, а также значение на выходе 13) в случае, когда один из токов протекает через резистор 6, на выходе 13 формируется уровень логического нуля, в противном случае - уровень логической единицы. Как следует из таблицы, логической элемент реализует функцию F(Xi, Х2, Хз) (Xi + Х2) Хз, причем одновременно через резистор 6 протекает не более одного тока (или И или te), т.е. уровень логического нуля остается постоянным. Таким образом, предложенный логический элемент по сравнению с известным позволяет реализовать функцию от трех переменных, т.е. расширить функциональные возможности, причем задержка остается практически равной задержке логического элемента, реализующего функцию от двух переменных.

Формула изобретения Логический элемент, содержащий пять транзисторов, резистор, два источника тока, две шины опорного напряжения, два входа и выход, эмиттеры первого и второго транзисторов подключены к первому источнику тока, коллектор первого транзистора

соединен с эмиттерами третьего и четвертого транзисторов, база первого транзистора соединена с эмиттером пятого транзистора

и вторым источником тока, база второго транзистора - с первой шиной опорного напряжения, база четвертого транзистора подключена к второй шине опорного напряжения, база пятого транзистора соединена

с первым входом, база третьего транзистора соединена с вторым входом, первый вывод резистора подключен к выходу, коллектор пятого транзистора подключен к второму выводу резистора, отличающийся тем, что,с целью расширения функциональных возможностей, в логический элемент введены семь дополнительных транзисторов, дополнительный источник тока и третий вход, причем эмиттеры первого и второго дополнительных транзисторов соединены с дополнительным источником тока, база первого дополнительного транзистора соединена с базой первого транзистора, база второго дополнительного

транзистора - с первой шиной опорного напряжения, базы третьего и шестого дополнительных транзисторов соединены с третьим входом, база четвертого дополнительного транзистора соединена с вторым

входом, а коллектор четвертого дополнительного транзистора - с коллекторами седьмого дополнительного транзистора и четвертого транзистора и выходом, коллекторы второго, третьего, пятого и шестого

дополнительных транзисторов соединены с коллекторами третьего и пятого транзисторов, базы пятого и седьмого дополнительных транзисторов соединены с второй шиной опорного напряжения, эмиттеры четвертого и пятого дополнительных транзисторов соединены с коллектором первого дополнительного транзистора, эмиттер третьего дополнительного транзистора соединен с эмиттером третьего транзистора,

коллектор второго транзистора соединен с эмиттерами шестого и седьмого дополнительных транзисторов.

Примечание. Протекание тока по пути коллектор-эмиттер транзисторов с номером i обозначено как Tj, а протекание тока через резистор 8 - как R. Запись /Tj+Tj/ означает, что ток протекает параллельно через оба транзистора / после них он вновь складывается/.

7 о-

21о Pjn7f wg, -зЦ -и-Ь-ч---4--- |

п°-%5

Л1

К

.J

и

| Микросхемы интегральные | |||

| Устройство для зарядки аккумуляторов | 1928 |

|

SU11520A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Алексеенко А.Г., Шагурин И.И | |||

| Микросхемотехника - М.: Радио и связь, 1982, с.115-118. | |||

Авторы

Даты

1992-06-23—Публикация

1990-01-24—Подача