Изобретение относится к импульсной технике, в частности к логическим схемам на переключений тока, и может быть использовано в сверхскоростных интегральных схемах для построения комбинационной ча- ,сти логических схем.

Целью изобретения является расширение функциональных возможностей схемы.

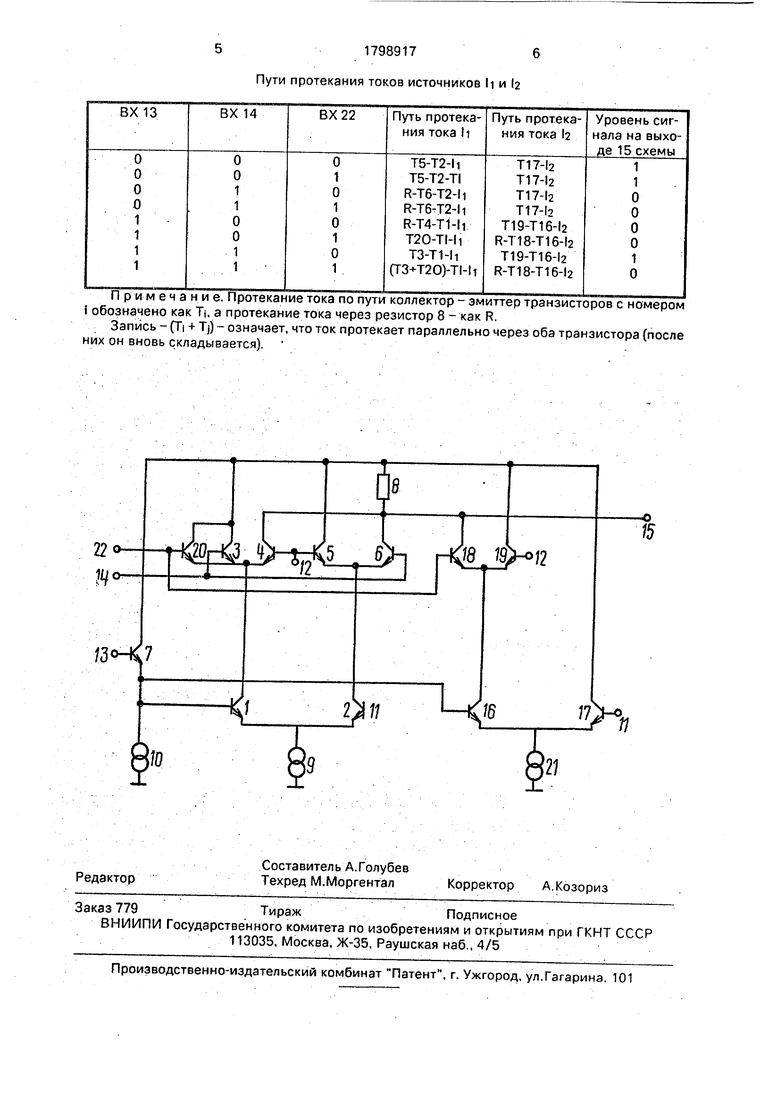

Изобретение поясняется чертежом, где представлена предложенная электрическая схема, реализующая функцию.

Схема на переключении тока, реализующая функцию

F(X1. Х2, ХЗ) Х1Х2ХЗ + Х1Х2

(фиг.1), содержит семь транзисторов 1-7, резистор 8, два источника тока 9, 10, два источника опорного напряжения 11, 12, два входа 13, 14 и выход 15, причем .первый и второй транзисторы 1, 2 выполнены с объединенными эмиттерами, которые подключены к первому источнику тока 9, коллектор

первого транзистора 1 соединен с эмиттерами третьего 3 и четвертого 4 транзисторов, коллектор второго 2-е эмиттерами пятого 5 и шестого 6 транзисторов, а база - первым источником опорного напряжения 11, базы четвертого 4 и пятого 5 транзисторов объединены и подключены ко второму источнику опорного напряжения 12, база первого транзистора 1 соединена с эмиттером седь- . мого 7 и со вторым источником тока 10, база седьмого транзистора 7 соединена с первым входом 13 схемы, базы третьего 3 и шестого.6 транзисторов объединены и соединены со вторым входом 14 схемы, коллекторы четвертого 4 и шестого 6 транзисторов объединены и подключены к первому концу резистора 8 и к выходу 15 схемы, коллекторы третьего 3 и пятого 5 транзисторов объединены и подключены к коллектору седьмого транзистора 7 и второму концу резистора 8.

XI

Ю 00 О

XI

Согласно изобретению в схему дополнительно введены пять транзисторов 16-20, источник тока 21, третий вход схемы 22, причем эмиттеры первого 16 и второго 17 дополнительных транзисторов объединены и соединены с первым дополнительным источником тока 21, коллектор первого дополнительного транзистора 16 соединен с объединенными эмиттерами третьего 18 и четвертрго 19 дополнительных транзисторов, база первого дополнительного транзистора 16 соединена с эмиттером седьмого 7 транзистора, база второго дополнительного транзистора 17 - с первым источником опорного напряжения 11, база третьего дополнительного транзистора 18 - с базой пятого 20 дополнительного транзистора и с третьим входом схемы 22, а коллектор - с коллектором шестого 6 транзистора, база четвертого 19 дополнительного транзистора соединена со вторым источником опорного напряжения 12, а коллектор - с коллекторами второго 17 и пятого 20 дополнительных, и третьего 3 транзисторов, эмиттер пятого дополнительного транзистора 20 соединен с эмиттером третьего 3 транзистора. . .. ..: . ; ; Предложенная схема функционирует следующим образом. ;

На входы схемы 13, 14, 22 подаются сигналы, соответствующие уровню логического нуля или единицы. В таблице представлены пути протекания токов первого источника тока 9 (И) и дополнительного источника тока 21 (12) при различных комбинациях входных сигналов (всего комбинаций 23 8), а также значение на выходе схемы (в случае, когда один из токов протекает через резистор 8, на выходе 15 формируется уровень логического нуля, в противном случае - уровень логической единицы).

Как следует из таблицы, схема действительно реализует функцию, причем одновременно через резистор 8 протекает не более одного тока (или И, или (2), т.е. уровень логического нуля остается постоянным.

Таким образом, предложенная схема по сравнению с известной схемой позволяет реализовать функцию от трех переменных, т.е. расширить и функциональное возможности при этом задержка остается практически разной задержке схемы, реализующей функцию от двух переменных.

Формул а изобретения

1

Схема на переключении тока, содержащая семь транзисторов, резистор, два источника тока, два источника опорного напряжения, два входа и выход, причем первый и второй транзисторы выполнены с объ- единенными эмиттерами, которые подключены к первому источнику тока, коллектор первого транзистора соединен с эмиттерами третьего и четвертого транзисторов, коллектор второго - с эмиттерами пятого и шестого транзисторов, а база - с первым источником опорного напряжения,

базы четвертого и пятого транзисторов подключены к второму источнику опорного напряжения, база первого транзистора соединена с эмиттером седьмого и с вторым источником тока, база седьмого транзистора соединена с первым входом схемы, базы третьего и шестого транзисторов соединены с вторым входом схемы, коллекторы четвертого и шестого транзисторов подключены к первому выводу резистора и

к выходу схемы, коллекторы третьего и пятого транзисторов подключены к коллектору седьмого транзистора и второму выводу резистора, о т л и ч а ю щ а я с я тем, что, с целью расширения функциональных возможностей, в схему дополнительно введены пять транзисторов, источник тока, третий вход схемы, причем эмиттеры первого и второго дополнительных транзисторов соеди- иены с дополнительным источником тока,

коллектор первого дополнительного транзистора соединен эмиттерами третьего и четвертого дополнительных транзисторов, база первого дополнительного транзистора соединена с эмиттером седьмого транзйстора. база второго дополнительного транзистора - с первым Источником опорного напряжения, база третьего дополнительного транзистора - с базой пятого дополнительного транзистора и с третьим входом

схемы, а коллектор -с коллектором шестого транзистора, база четвертрго дополнительного транзистора соединена с вторым источником опорного напряжения, а коллектор- с коллекторами второго и пятого дополнительных и третьего транзисторов, эмиттер пятого дополнительного транзистора соединен с эмиттером третьего транзистора.

Пути протекания токов источников И и (2

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент на переключении тока | 1990 |

|

SU1723669A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1716600A1 |

| Логический элемент на переключении тока | 1990 |

|

SU1723670A1 |

| Логический элемент "Исключающее ИЛИ" | 2022 |

|

RU2792407C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ИСКЛЮЧАЮЩЕЕ ИЛИ» | 2022 |

|

RU2795286C1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

| Логический элемент на переключении тока | 1988 |

|

SU1631714A1 |

| Логический элемент | 1990 |

|

SU1742990A1 |

| Логический элемент | 1990 |

|

SU1742991A1 |

| Полный троичный сумматор | 1979 |

|

SU826342A1 |

Изобретение относится к импульсной технике, в частности к логическим схемам на переключении тока, и может быть использовано в сверхскоростных интегральных схемах для построения комбинационной части логических схем. Схема позволяет реализр- вать функцию F(xi, X2, хз) Х1Х2хз + хш. Сущность изобретения: Устройство содержит семь транзисторов, один резистор, два источника тока, два источника опорного напряжения, три входа, один выход, пять до- полнительных транзисторов, один дополнительный источник тока. 1 ил., 1 табл.

Примечание. Протекание тока по пути коллектор - эмиттер транзисторов с номером i обозначено как Tj, а протекание тока через резистор 8 - как R.

Запись - (Ti + TJ) - означает, что ток протекает параллельно через оба транзистора (после них он вновь складывается).

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Алексенко А.Г., Шагурин И.И | |||

| Микросхемотехника - М.: Радио и связь, 1982, с, 115-118 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микросхемы интегральные | |||

| Нагревательный прибор для жидкости | 1913 |

|

SU1520A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Руководящий документ | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

1993-02-28—Публикация

1990-01-24—Подача