.-. Фиг1

Изобретение относится к вычислительной технике, может быть использовано для контроля хода вычислений в ЭВМ и является усовершенствованием изобретения по авт.св. № 1624462.

Цель изобретения - повышение достоверности контроля путем выявления зацикливания одновременно двух переменных.

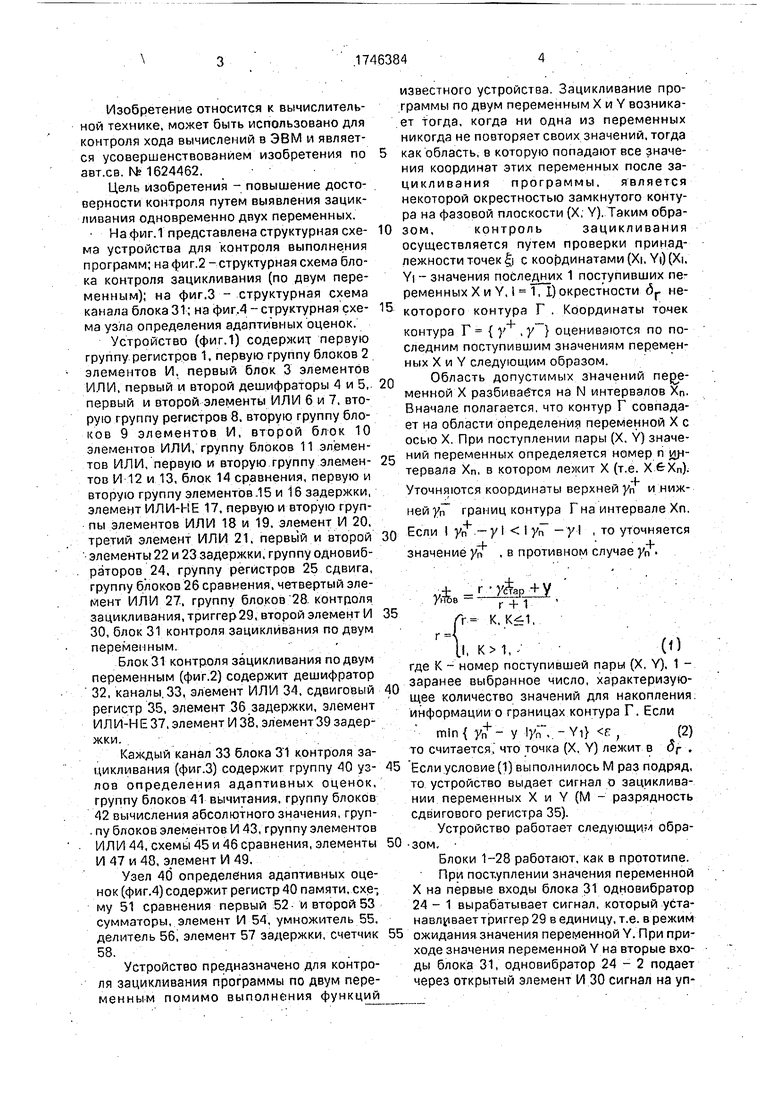

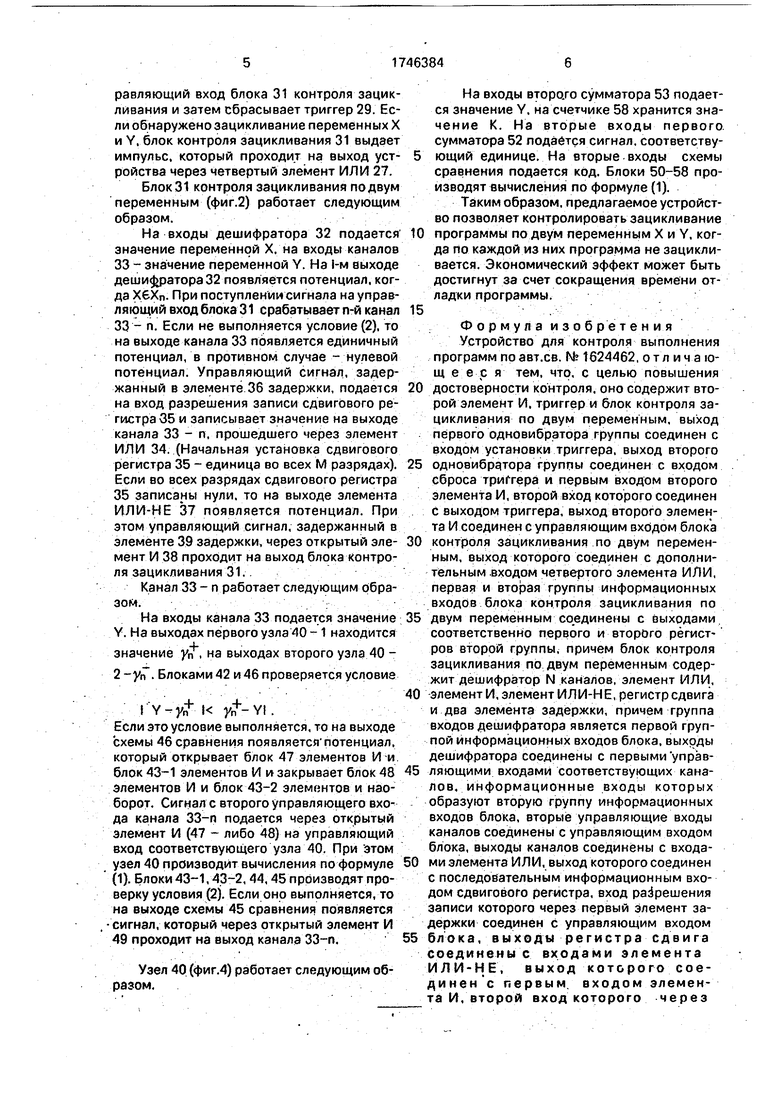

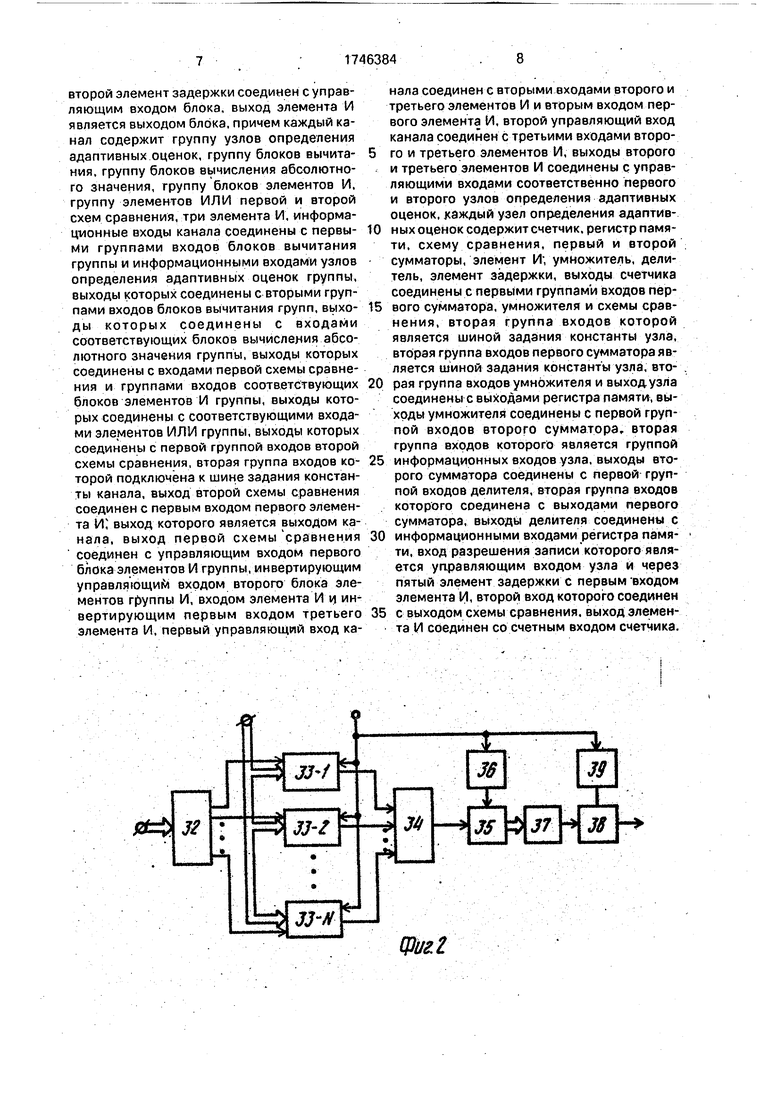

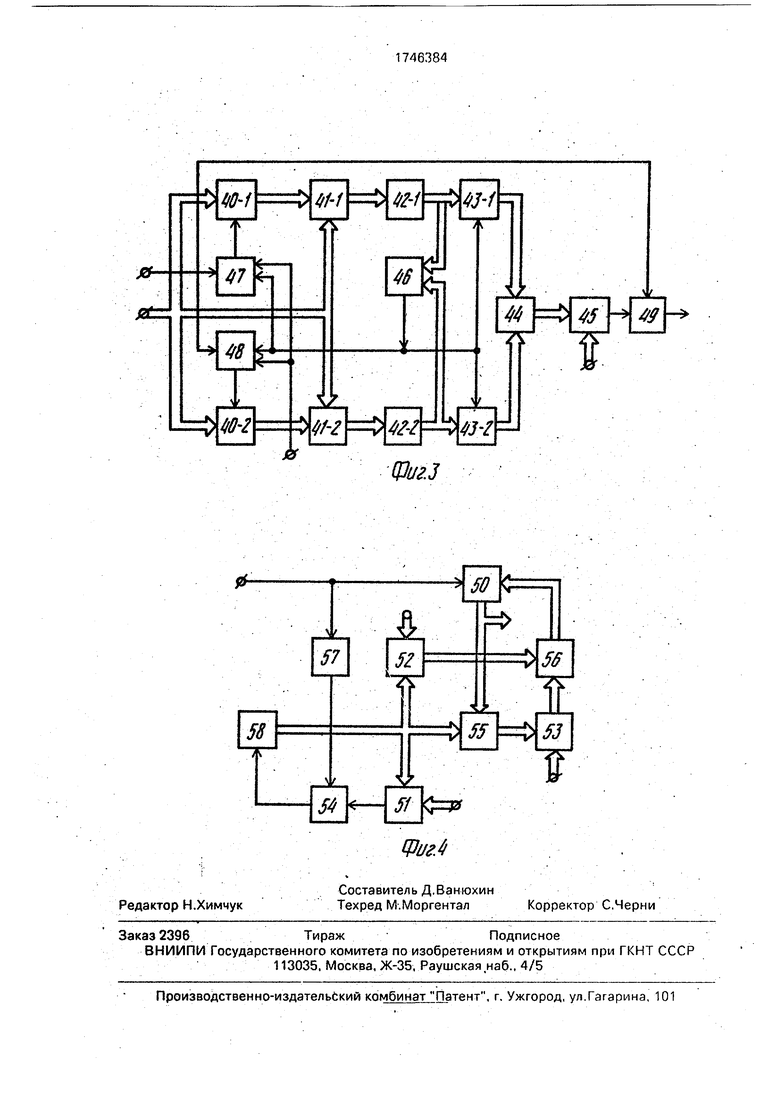

На фиг. 1 представлена структурная схема устройства для контроля выполнения программ; на фиг.2-структурная схема блока контроля зацикливания (по двум переменным); на фиг.З - структурная схема канала блока 31; на фиг.4 - структурная схема узла определения адаптивных оценок.

Устройство (фиг.1) содержит первую группу регистров 1, первую группу блоков 2 элементов И, первый блок 3 элементов ИЛИ, первый и второй дешифраторы 4 и 5, первый и второй элементы ИЛИ 6 и 7, вторую группу регистров 8. вторую группу блоков 9 элементов И, второй блок 10 элементов ИЛИ, группу блоков 11 элементов ИЛИ, первую и вторую группу элементов И 12 и 13, блок 14 сравнения, первую и вторую группу элементов .15 и 16 задержки, элемент ИЛИ-ИЕ 17, первую и вторую группы элементов ИЛИ 18 и 19, элемент И 20, третий элемент ИЛИ 21. первый и второй элементы 22 и 23 задержки, группу одновиб- ра торов 24, группу регистров 25 сдвига, группу блоков 26 сравнения, четвертый элемент ИЛИ 27. группу блоков 28 контроля зацикливания, триггер29, второй элемент И 30, блок 31 контроля зацикливания по двум переменным.

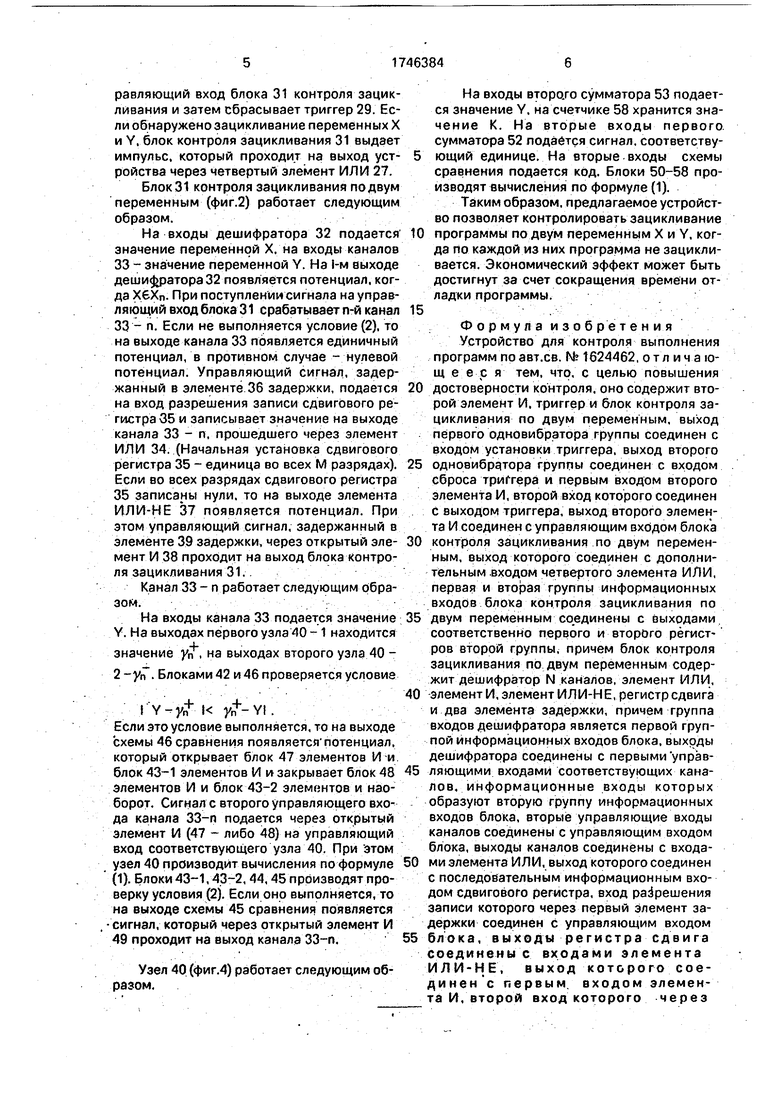

Блок 31 контроля зацикливания по двум переменным (фиг.2) содержит дешифратор 32, каналы 33, элемент ИЛИ 34, сдвиговый регистр 35, элемент 36.задержки, элемент ИЛИ-НЕ 37, элемент И 38, элемент 39 задержки.

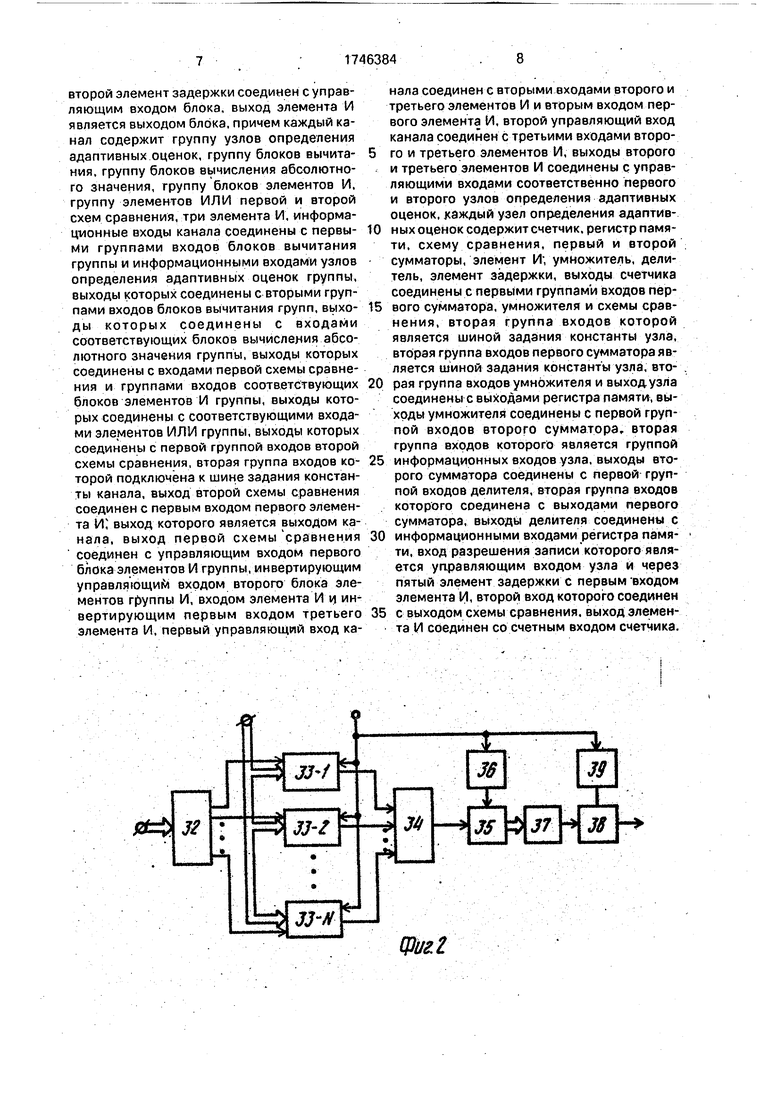

Каждый канал 33 блока 31 контроля зацикливания (фиг.З) содержит группу 40 узлов определения адаптивных оценок, группу блоков 41 вычитания, группу блоков 42 вычисления абсолютного значения, группу блоков элементов И 43, группу элементов ИЛИ 44, схемы 45 и 46 сравнения, элементы И 47 и 48, элемент И 49.

Узел 40 определения адаптивных оценок (фиг.4) содержит регистр 40 памяти, схе-, му 51 сравнения первый 52 и второй 53 сумматоры, элемент И 54, умножитель 55, делитель 56, элемент 57 задержки, счетчик 58.

Устройство предназначено для контроля зацикливания программы по двум переменным помимо выполнения функций

известного устройства. Зацикливание программы по двум переменным X и Y возникает тогда, когда ни одна из переменных никогда не повторяет своих значений, тогда

как область, в которую попадают все значения координат этих переменных после зацикливания программы, является некоторой окрестностью замкнутого контура на фазовой плоскости (X, Y). Таким образом,контрользацикливания

осуществляется путем проверки принадлежности точек § с координатами (Xi, Yi) (Xi, YI - значения последних 1 поступивших переменных X и Y, i 1, 1) окрестности 5Г некоторого контура Г . Координаты точек

контура Г { у , у } оцениваются по последним поступившим значениям переменных X и Y следующим образом.

Область допустимых значений переменной X разбивается на N интервалов Хп. Вначале полагается, что контур Г совпадает на области определения переменной X с осью X. При поступлении пары (X. Y) значений переменных определяется номер п интервала Хп, в котором лежит X (т.е. Х&ХП).

Уточняются координаты верхней уп и нижней угГ границ контура Г на интервале Хп. i

Если I уп - - у , то уточняется значение уп , в противном случае УП

35

,

гг К. КЈ1,

0

г

ll, ,-(1)

где К - номер поступившей пары (X, Y), 1 - заранее выбранное число, характеризующее количество значений для накопления информации о границах контура Г. Если

,+

min{ Уп - У } п , - Yi} F ;

(2)

г- .

то считается, что точка (X, Y) лежит в Of , 5 Если условие (1) выполнилось М раз подряд, то устройство выдает сигнал о зацикливании переменных X и Y (М - разрядность сдвигового регистра 35).

Устройство работает следующим обра- 0-зом.

Блоки 1-28 работают, как в прототипе. При поступлении значения переменной X на первые входы блока 31 одновибратор 24-1 вырабатывает сигнал, который устанавливает триггер 29 в единицу, т.е. в режим 5 ожидания значения переменной Y. При приходе значения переменной Y на вторые входы блока 31, одновибратор 24-2 подает через открытый элемент И 30 сигнал на управляющий вход блока 31 контроля зацикливания и затем сбрасывает триггер 29. Если обнаружено зацикливание переменных X и Y. блок контроля зацикливания 31 выдает импульс, который проходит на выход устройства через четвертый элемент ИЛИ 27.

Блок 31 контроля зацикливания по двум переменным (фиг.2) работает следующим образом.

На входы дешифратора 32 подается значение переменной X. на входы каналов 33 - значение переменной Y. На i-м выходе дешифратора 32 появляется потенциал, когда Х6ХП. При поступлении сигнала на управляющий вход блока 31 срабатывает n-й канал 33 - п. Если не выполняется условие (2), то на выходе канала 33 появляется единичный потенциал, в противном случае - нулевой потенциал. Управляющий сигнал, задержанный в элементе 36 задержки, подается на вход разрешения записи сдвигового регистра 35 и записывает значение на выходе канала 33 - п, прошедшего через элемент ИЛИ 34. (Начальная установка сдвигового регистра 35 - единица во всех М разрядах). Если во всех разрядах сдвигового регистра 35 записаны нули, то на выходе элемента ИЛИ-НЁ 37 появляется потенциал. При этом управляющий сигнал, задержанный в элементе 39 задержки, через открытый элемент И 38 проходит на выход блока контроля зацикливания 31.

Канал 33 - п работает следующим образом.

На входы канала 33 подается значение Y. На выходах первого узла 40-1 находится

значение уп , на выходах второго узла 40 - 2 -угГ. Блоками 42 и 46 проверяется условие

I Y-yrf К yrt-YI.

Если это условие выполняется, то на выходе хемы 46 сравнения появляется потенциал, который открывает блок 47 элементов И и блок 43-1 элементов И и закрывает блок 48 лементов И и блок 43-2 элементов и наоборот. Сигнал с второго управляющего вхоа канала 33-п подается через открытый лемент И (47 - либо 48) на управляющий вход соответствующего узла 40. При этом зел 40 производит вычисления по формуле 1). Блоки 43-1,43-2, 44,45 производят проверку условия (2). Если оно выполняется, то а выходе схемы 45 сравнения появляется игнал, который через открытый элемент И 9 проходит на выход канала 33-п.

Узел 40 (фиг.4) работает следующим обазом.

На входы второ/о сумматора 53 подается значение Y. на счетчике 58 хранится значение К. На вторые входы первого сумматора 52 подается сигнал, соответству- 5 ющий единице. На вторые входы схемы сравнения подается код. Блоки 50-58 производят вычисления по формуле (1).

Таким образом, предлагаемое устройство позволяет контролировать зацикливание 10 программы по двум переменным X и Y, когда по каждой из них программа не зацикливается. Экономический эффект может быть достигнут за счет сокращения времени отладки программы. 15

Формула изобретения Устройство для контроля выполнения программ по авт.св. № 1624462, отличающееся тем, что, с целью повышения 0 достоверности контроля, оно содержит второй элемент И, триггер и блок контроля зацикливания по двум переменным, выход первого одновибратора группы соединен с входом установки триггера, выход второго 5 одновибрдтора группы соединен с входом сброса триггера и первым входом второго элемента И, второй вход которого соединен с выходом триггера, выход второго элемента И соединен с управляющим входом блока 0 контроля зацикливания по двум переменным, выход которого соединен с дополнительным входом четвертого элемента ИЛИ, первая и вторая группы информационных входов блока контроля зацикливания по 5 двум переменным соединены с выходами соответственно первого и второго регистров второй группы, причем блок контроля зацикливания по двум переменным содержит дешифратор N каналов, элемент ИЛИ, 0 элемент И, элемент ИЛИ-НЕ, регистр сдвига и два элемента задержки, причем группа входов дешифратора является первой группой информационных входов блока, выходы дешифратора соединены с первыми управ- 5 ляющими входами соответствующих каналов, информационные входы которых образуют вторую группу информационных входов блока, вторые управляющие входы каналов соединены с управляющим входом блока, выходы каналов соединены с входа- 0 ми элемента ИЛИ, выход которого соединен с последовательным информационным входом сдвигового регистра, вход разрешения записи которого через первый элемент задержки соединен с управляющим входом 5 блока, выходы регистра сдвига соединены с входами элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И, второй вход которого через

второй элемент задержки соединен с управляющим входом блока, выход элемента И является выходом блока, причем каждый канал содержит группу узлов определения адаптивных оценок, группу блоков вычита- ния, группу блоков вычисления абсолютного значения, группу блоков элементов И, группу элементов ИЛИ первой и второй схем сравнения, три элемента И, информационные входы канала соединены с первы- ми группами входов блоков вычитания группы и информационными входами узлов определения адаптивных оценок группы, выходы которых соединены с вторыми группами входов блоков вычитания групп, выхо- ды которых соединены с входами соответствующих блоков вычисления абсолютного значения группы, выходы которых соединены с входами первой схемы сравнения и группами входов соответствующих блоков элементов И группы, выходы которых соединены с соответствующими входами элементов ИЛИ группы, выходы которых соединены с первой группой входов второй схемы сравнения, вторая группа входов ко- торой подключена к шине задания константы канала, выход второй схемы сравнения соединен с первым входом первого элемента 1/К выход которого является выходом канала, выход первой схемы сравнения соединен с управляющим входом первого блока элементов И группы, инвертирующим управляющим входом второго блока элементов группы И, входом элемента И ц инвертирующим первым входом третьего элемента И. первый управляющий вход канала соединен с вторыми входами второго и третьего элементов И и вторым входом первого элемента И, второй управляющий вход канала соединен с третьими входами второго и третьего элементов И, выходы второго и третьего элементов И соединены с управляющими входами соответственно первого и второго узлов определения адаптивных оценок, каждый узел определения адаптивных оценок содержит счетчик, регистр памяти, схему сравнения, первый и второй сумматоры, элемент И; умножитель, делитель, элемент задержки, выходы счетчика соединены с первыми группами входов первого сумматора, умножителя и схемы сравнения, вторая группа входов которой является шиной задания константы узла, вторая группа входов первого сумматора является шиной задания константы узла, вторая группа входов умножителя и выход узла соединены с выходами регистра памяти, выходы умножителя соединены с первой группой входов второго сумматора, вторая группа входов которого является группой информационных входов узла, выходы второго сумматора соединены с первой группой входов делителя, вторая группа входов которого соединена с выходами первого сумматора, выходы делителя соединены с информационными входами регистра памяти, вход разрешения записи которого является управляющим входом узла и через пятый элемент задержки с первым входом элемента И, второй вход которого соединен с выходом схемы сравнения, выход элемента И соединен со счетным входом счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля выполнения программ | 1988 |

|

SU1624462A2 |

| Устройство для контроля программ | 1987 |

|

SU1418719A1 |

| Устройство для контроля программ | 1988 |

|

SU1509906A2 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 2001 |

|

RU2216760C2 |

| Коррелятор | 1981 |

|

SU1024933A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА ПИЛОТИРОВАНИЯ САМОЛЕТА ЛЕТЧИКОМ | 1998 |

|

RU2136046C1 |

| Многоканальное устройство для идентификации моделей | 1984 |

|

SU1238100A1 |

| Адаптивная система регулирования многомерного объекта | 1981 |

|

SU1174901A1 |

| Адаптивный цифровой фильтр | 1987 |

|

SU1543542A1 |

| Аналого-цифровое вычислительное устройство | 1988 |

|

SU1501103A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля хода вычислений ЭВМ. Целью изобретения является повышение достоверности контроля за счет выявления зацикливания программы по двум переменным X и Y Для этого в устройство дополни- тельно-введен блок 31 контроля зацикливания по двум переменным Появление сигнала на выходе блока свидетельствует о зацикливании программы по двум переменным. Функционирование блока контроля зацикливания основано на определении при каждом изменении контролируемых переменных попадания значений переменных в окрестность некоторого контура на фазовой плоскости (X, Y). При многократном попадании значений переменных в окрестность контура на выходе блока контроля зацикливания появляется сигнал. Кроме того в устройство введены триггер 29 и второй элемент И 30. 4 ил.

qtoeZ

4Н

4H

047

48

Ш

3#v

0

Ш

4J-f

46

Ъ

л

44

$

4S

W

7

Ј # -/43-t

$M.J

| Устройство для контроля выполнения программ | 1988 |

|

SU1624462A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-07-07—Публикация

1990-02-22—Подача