(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1987 |

|

SU1418719A1 |

| Устройство для контроля хода программ | 1990 |

|

SU1737455A2 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

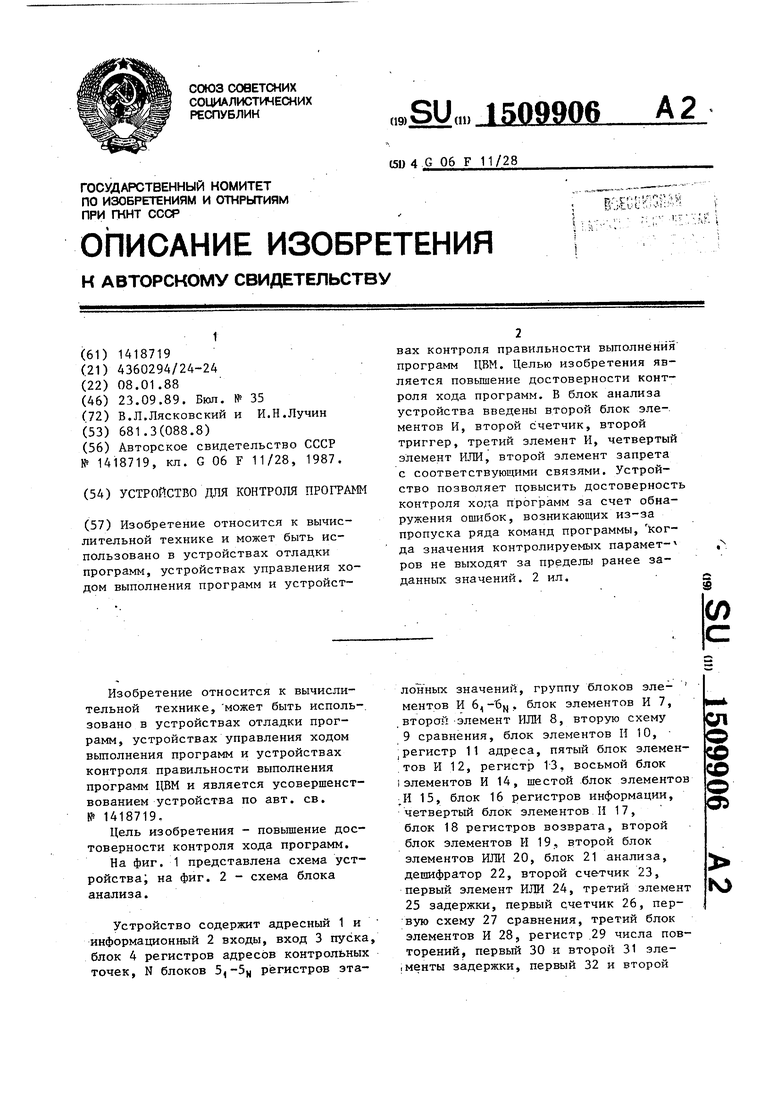

Изобретение относится к вычислительной технике и может быть использовано в устройствах отладки программ, устройствах управления ходом выполнения программ и устройствах контроля правильности выполнения программ ЦВМ. Целью изобретения является повышение достоверности контроля хода программ. В блок анализа устройства введены второй блок элементов И, второй счетчик, второй триггер, третий элемент И, четвертый элемент ИЛИ, второй элемент запрета с соответствующими связями. Устройство позволяет повысить достоверность контроля хода программ за счет обнаружения ошибок, возникающих из-за пропуска ряда команд программы, когда значения контролируемых параметров не выходят за пределы ранее заданных значений. 2 ил.

Изобретение относится к вычислительной технике, может быть исполь-. зовано в устройствах отладки программ, устройствах управления ходом вьшолнения программ и устройствах контроля правильности выполнения программ ЦВМ и является усовершенствованием устройства по авт. св. № 1418719,

Цель изобретения - повьшение достоверности контроля хода программ.

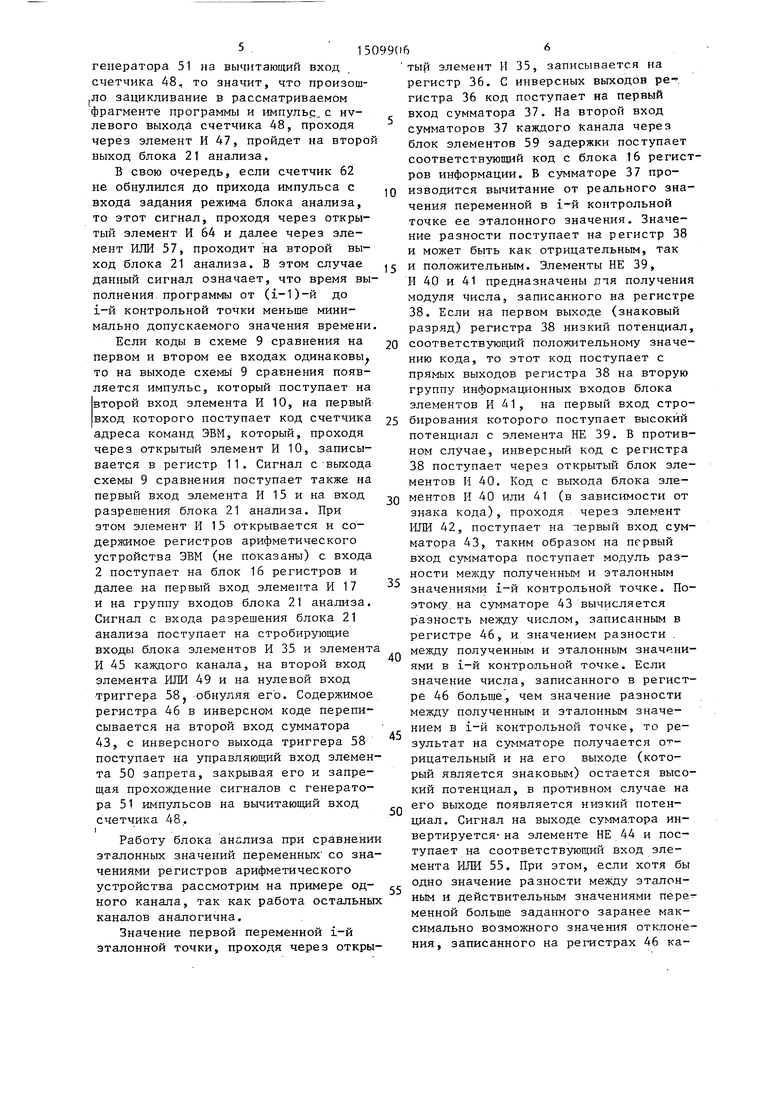

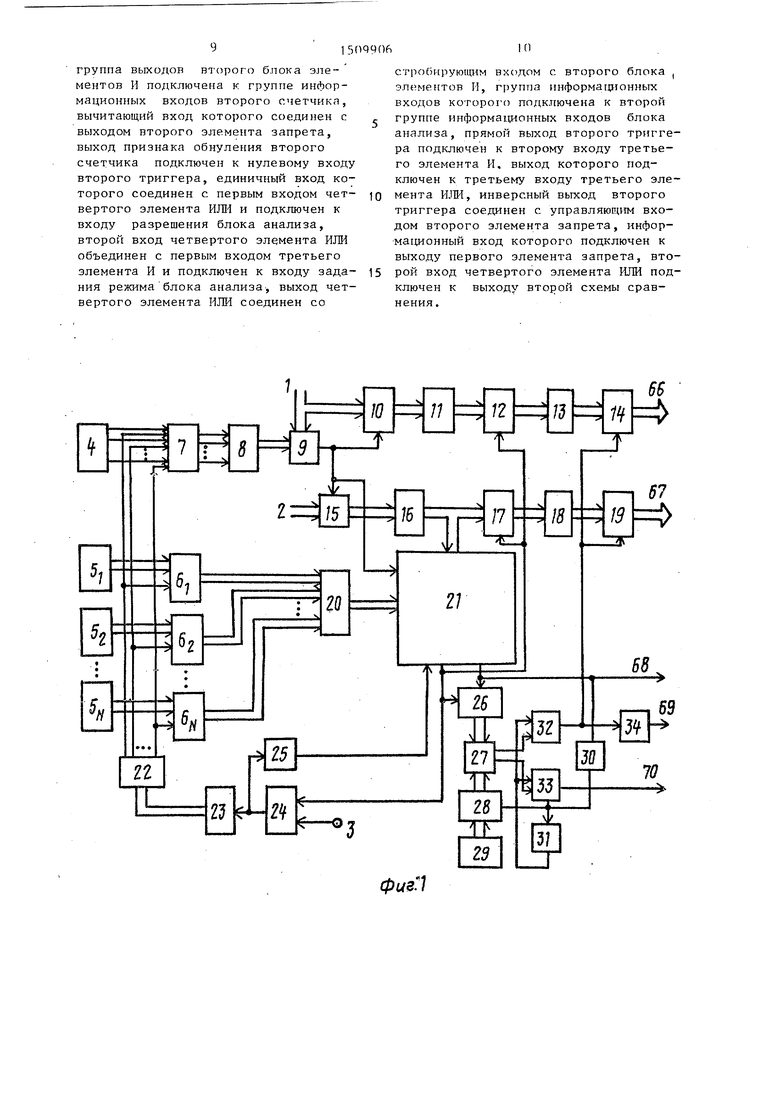

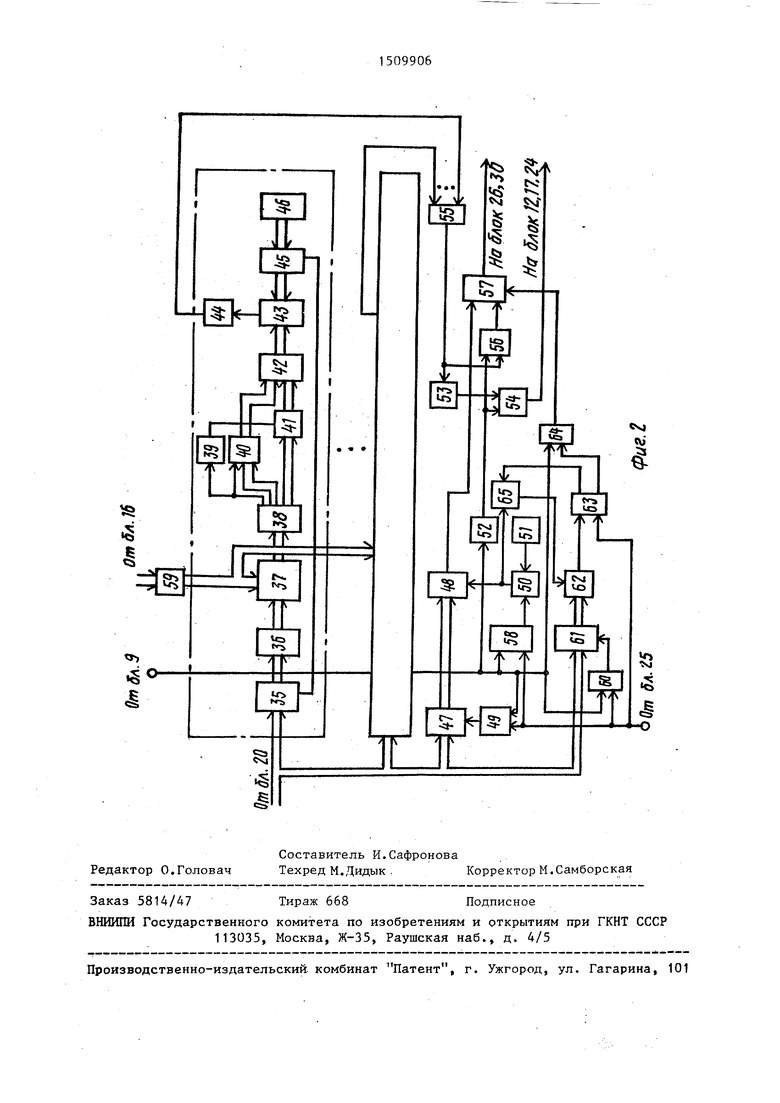

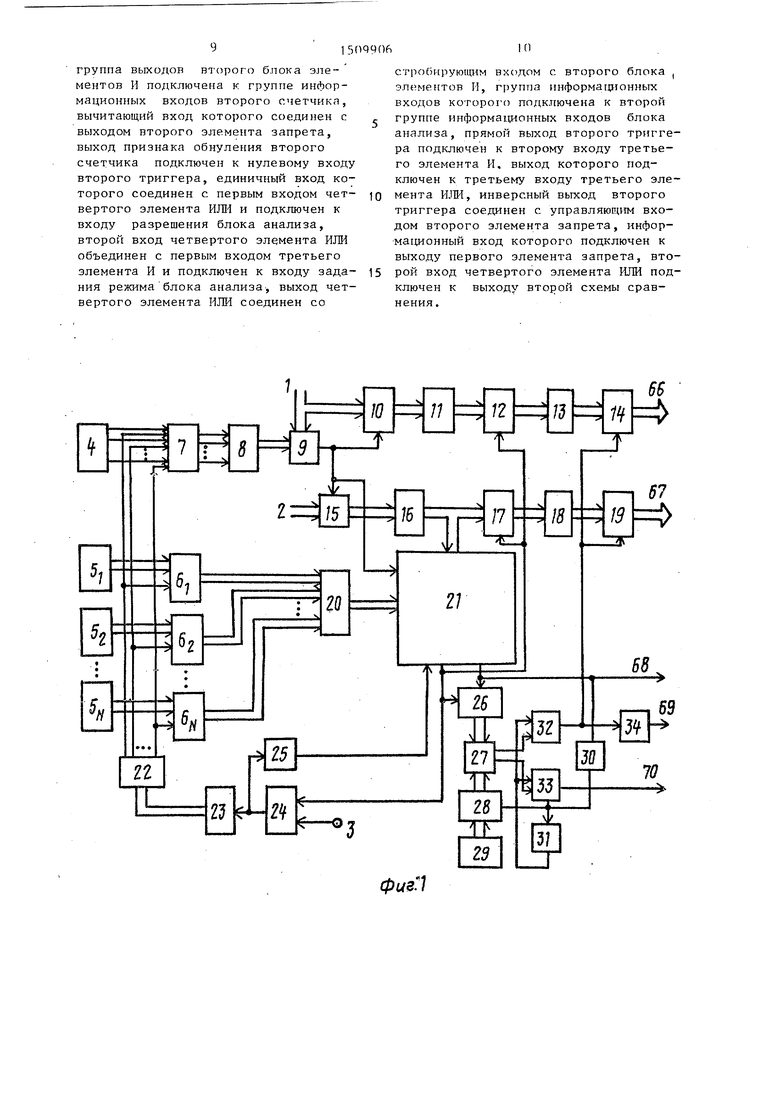

На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока анализа.

Устройство содержит адресный 1 и информационный 2 входы, вход 3 пуска, блок 4 регистров адресов контрольных точек, N блоков 5,-5ц регистров эталонных значений, группу блоков эле- ментов И ,. блок элементов И 7, второй элемент ИЛИ 8, вторую схему 9 сравнения, блок элементов И 10, регистр 11 адреса, пятый блок элемен- тов И 12, регистр 13, восьмой блок iэлементов И 14, шестой блок элементов 11 15, блок 16 регистров информации, четвертый блок элементов И 17, блок 18 регистров возврата, второй блок элементов И 19, второй блок элементов ИЛИ 20, блок 21 анализа, дешифратор 22, второй счетчик 23, первый элемент ИЩ 24, третий элемент 25 задержки, первый счетчик 26, первую схему 27 сравнения, третий блок элементов И 28, регистр .29 числа повторений, первый 30 и второй 31 эле- 1 менты задержки, первый 32 и второй

сл

со QD О

к

33 элементы И, четвертый элемент 34 задержки.

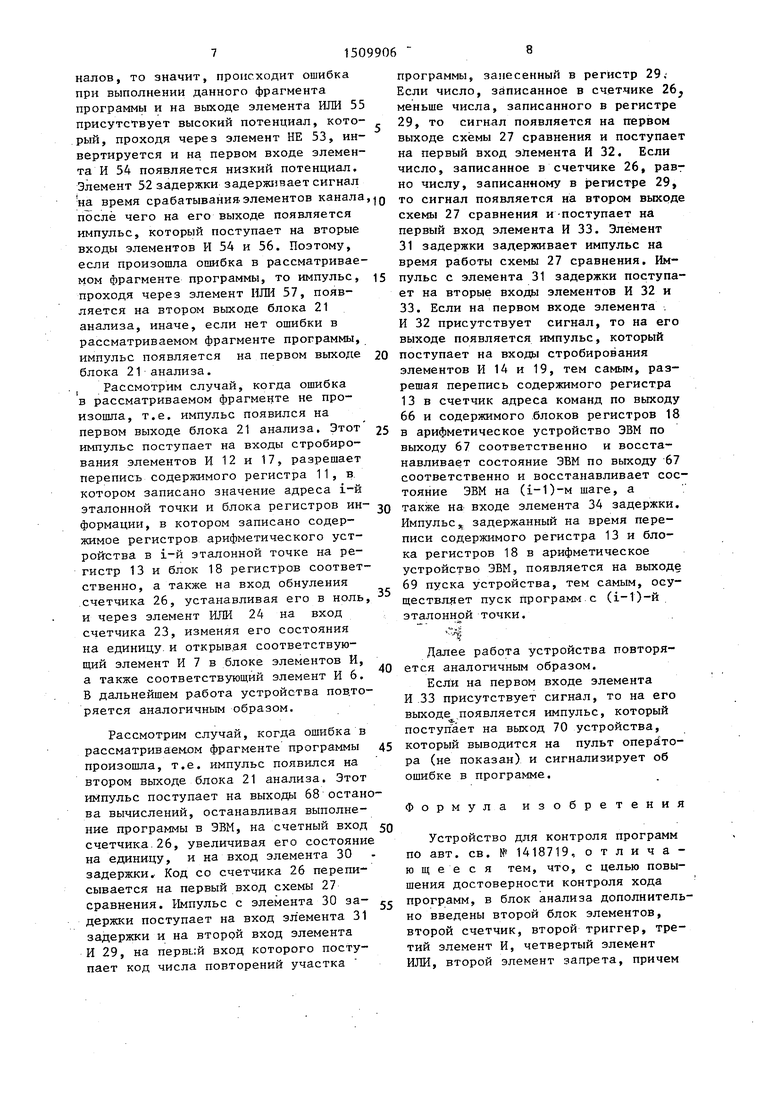

В блоке анализа каждый канал содержит первый блок элементов И 35, первый регистр 36, первый сумматор 37, второй регистр 38, первый элеме НЕ 39, третий блок элементов И 40, второй блок элементов И 41, блок элементов ИЛИ 42, второй сумматор .43, второй элемент НЕ 44, четвертый элемент И 45 и третий регистр 46. В блок анализа также входят блок элементов И 47,счетчик 48,первый элемент ИЛИ 49, элемент 50 запрета, генера- тор 51 импульсов, элемент 52 задержки, элемент НЕ 53, второй элемент И 54, второй элемент ИЛИ 55, первый элемент И 56, третий элемент ИЛИ 57 триггер 58. блок 59 элементов за- держки, четвертый элемент ИЛИ 60, второй блок элементов И 61, второй счетчик 62, второй триггер 63, третий элемент И 64 и второй элемент . 65 запрета.

Кроме того, устройство имеет две группы информационных выходов 66 и 67, выход 68 останова, выход 69 пуска и выход 70 ошибки.

Устройство работает следующим об- разом.

В исходном состоянии на блоке 4 регистров адресов контрольных точек записаны адреса контрольных точек (блок 4 содержит N регистров по чис- лу контрольных точек в программе). На i-M блоке 5 регистров (i 1,N) записаны эталонные значения переменных программ для i-й контрольной точки. На регистре 29 записано число повторения фрагмента программы. На J-M регистре 46 (j 1,М) записано значение максимально возможного отклонения j-й переменной от ее эталонного значения. Остальные регистры, блоки регистров и счетчики устройств обнулены.

После появления сигнала Пуск на входе 3 устройства, который озна- чает начало счета контролируемой программы, через элемент ИЛИ, 24 импульс поступает -на вход счетчика 23, увеличивая его состояние на единицу и через элемент -25 задержки на вход задания режима блока анализа.

Дешифратор 22 расшифровывает код на выходе счетчика 23 и на его соответствующем входе появляется сигнал.

10 15 20 25

30

35 40 5

5

который поступает на второй вход соответствующего, элемента И блока элементов И 7, а также на второй вход соответствующего блока элементов И 6, открывая эти элементы. Адрес i-контрольной точки программы, проходя через открытый элемент И блока элементов И 7 и через элемент ИЛИ 8, поступает на первый вход схемы 9 сравнения, на второй вход которой поступает код со счетчика адреса команд ЭВМ (не показана). Содержимое блока регистров 5 i-й контрольной точки поступает через открытый блок элементов И 6 и блок элементов ИЛИ 20 на группу информационных входов блока анализа.

На предпоследнем регистре блока 5 регистров записано максимально возможное значение времени выполнения фрагмента программы от (1-1)-и до. i-й контрольной точки программы с учетом времени задержки элемента 25 (i 1j N - 1), где под нулевой контрольной точкой подразумевается состояние начала программы. На последнем регистре блока регистров 5 записано минимально возможное значение времени выполнения фрагмента программы от (i-1)-й до i-й контрольной точки программы с учетом времени задержки элемента 25. Элемент 25 задержки задерживает сигнал на время срабатывания счетчика 23, дешифратора 22, элемента И 6 и элемента ИЛИ 20. Сигнал с выхода элемента 25 задержки устанавливает триггеры 58 и 63. в единичное состояние и, проходя через элементы ИЛИ 49 и 60, пос- тупает на вторые входы элементов И 47 и 61. Содержимое М-го и (М+1)-го регистров блока регистров 5 переписывается соответственно на счетчики 48 и 62. Низкий потенциал с инверсного выхода триггера 58 поступает на управляющий вход элемента 50 запрета, открывая его и, тем самым, разрешая поступление сигналов генератора 51 импульсов на вычитающий вход счетчика 48 и через открытый элемент 65 запрета на вычитающий вход счетчика 62.

Если счетчик 48 обнулился до прихода импульса с входа задания режима блока анализа, который переводит триггер 58 в нулевое состо яние и закрывает элемент запрета, тем самым, не разрешая прохождение импульсов с

генератора 51 на вычитающий вход счетчика 48. то значит, что произошло зацикливание в рассматриваемом фрагменте программы и импульс, с нулевого выхода счетчика 48, проходя через элемент И 47, пройдет на второ выход блока 21 анализа.

Б свою очередь, если счетчик 62 не обнулился до прихода импульса с входа задания режима блока анализа, то этот сигнал, проходя через открытый элемент И 64 и далее через элемент ИЛИ 57, проходит на второй выход блока 21 анализа. В этом случае данный сигнал означает, что время выполнения, программы от (1-1)-й до i-й контрольной точки меньше минимально допускаемого значения времени

Если коды в схеме 9 сравнения на первом и втором ее входах одинаковы, то на выходе схемы 9 сравнения появляется импульс, который поступает на второй вход элемента И 10, на первый вход которого поступает код счетчика адреса команд ЭВМ, который, проходя через открытый элемент И 10, записывается в регистр 11. Сигнал с выхода схемы 9 сравнения поступает также на первый вход элемента И 15 и на вход разрешения блока 21 анализа. При этом элемент И 15 открывается и содержимое регистров арифметического устройства ЭВМ (не показаны) с входа 2 поступает на блок 16 регистров и далее на первый вход элемента И 17 и на группу входов блока 21 анализа. Сигнал с входа разрешения блока 21 анализа поступает на стробирующие входы блока элементов И 35 и элемент И 45 каждого канала, на второй вход элемента ИЛИ 49 и на нулевой вход триггера 58, обнуляя его. Содержимое регистра 46 в инверсном коде переписывается на второй вход сумматора 43, с инверсного выхода триггера 58 поступает на управляющий вход элемента 50 запрета, закрывая его и запрещая прохождение сигналов с генератора 51 импульсов на вычитающий вход счетчика 48.

Работу блока анализа при сравнени эталонных значений переменных со значениями регистров арифметического устройства рассмотрим на примере одного канала, так как работа остальны каналов аналогична.

Значение первой переменной i-й эталонной точки, проходя через открытый элемент И регистр 36. С

0

5

35, записывается на инверсных выходов ре-. гистра 36 код поступает на первый вход сумматора 37. На второй вход сумматоров 37 каждого канала через блок элементов 59 задержки поступает соответствующий код с блока 16 регистров информации. В cy мaтope 37 производится вычитание от реального значения переменной в i-й контрольной точке ее эталонного значения. Значение разности поступает на регистр 38 и может быть как отрицательным, так и положительным. Элементы НЕ 39,

И 40 и 41 предназначены дчя получения модуля числа, записанного на регистре 38. Если на первом выходе (знаковый разряд) регистра 38 низкий потенциал, соответствующий положительному значению кода, то этот код поступает с прямь:х выходов регистра 38 на вторую группу информационных входов блока элементов И 41, на первый вход стро- бирования которого поступает высокий потенциал с элемента НЕ 39. В противном случае, инверсньш код с регистра 38 поступает через открытый блок элементов И 40. Код с выхода блока элементов И 40 или 41 (в зависимости от знака кода), проходя через элемент 1ШИ 42, поступает на первый вход сумматора 43, таким образом на первый вход сумматора поступает модуль разности между полученным и эталонным значениями i-й контрольной точке. Поэтому, на сумматоре 43 вычисляется разность между числом, записанным в регистре 46, и значением разности . между полученным и эталонным значениями в i-й контрольной точке. Если значение числа, записанного в регистре 46 больше, чем значение разности между полученным и эталонным значением в i-й контрольной точке, то результат на сумматоре получается отрицательный и на его выходе (который является знаковым) остается высокий потенциал, в противном случае на его выходе появляется низкий потенциал. Сигнал на выходе сумматора инвертируется- на элементе НЕ 44 и поступает на соответствующий вход элемента ИЛИ 55. При этом, если хотя бы одно значение разности между эталонным и действительным значениями переменной больше заданного заранее максимально возможного значения отклонения, записанного на регистрах 46 ка0

5

0

5

0

5

налов, то значит, происходит ошибка при выполнении данного фрагмента программы и на выходе элемента ИЛИ 55 присутствует высокий потенциал, который, проходя через элемент НЕ 53, инвертируется и на первом входе элемента И 54 появляется низкий потенциал. Элемент 52 задержки задерживает сигнал на время срабатывания, элементов канал а после чего на его выходе появляется импульс, который поступает на вторые входы элементов И 54 и 56. Поэтому, если произошла ошибка в рассматриваемом фрагменте программы, то импульс, проходя через элемент ИЛИ 57, появляется на втором выходе блока 21 анализа, иначе, если нет ошибки в рассматриваемом фрагменте программы, импульс появляется на первом выходе блока 21 анализа.

I Рассмотрим случай, когда ошибка в рассматриваемом фрагменте не произошла, т.е. импульс появился на первом выходе блока 21 анализа. Этот импульс поступает на входы стробиро- вания элементов И 12 и 17, разрешает перепись содержимого регистра 11, в котором записано значение адреса i-й эталонной точки и блока регистров ин- формации, в котором записано содержимое регистров арифметического устройства в i-й эталонной точке на регистр 13 и блок 18 регистров соответственно, а также на вход обнуления счетчика 26, устанавливая его в ноль, и через элемент ИЛИ 24 на вход счетчика 23, изменяя его состояния на единицу, и открыв.ая соответствующий элемент И 7 в блоке элементов И, а также соответствующий элемент И 6. В дальнейшем работа устройства повторяется аналогичным образом.

Рассмотрим случай, когда ошибка в рассматриваем.ом фрагменте программы произошла, т,е. импульс появился на втором выходе блока 21 анализа. Этот импульс поступает на выходы 68 останова вычислений, останавливая выполнение программы в ЭВМ, на счетный вход счетчика.26, увеличивая его состояние на единицу, и на вход элемента 30 задержки.. Код со счетчика 26 переписывается на первый вход схемы 27 сравнения. Импульс с элемента 30 за- держки поступает на вход эл емента 31 задержки и на второй вход элемента И 29, на первый вход которого поступает код числа повторений участка

Q s 0

5 Q

5 0

0

программы, занесенный в регистр 29,- Если число, записанное в счетчике 26j меньше числа, записанного в регистре 29, то сигнал появляется на первом выходе схемы 27 сравнения и поступает на первый вход элемента И 32, Если число, записанное в счетчике 26, равно числу, записанному в регистре 29, то сигнал появляется на втором выходе схемы 27 сравнения и-поступает на первый вход элемента И 33. Элемент 31 задержки задерживает импульс на время работы схемы 27 сравнения. Импульс с элемента 31 задержки поступает на вторые входы элементов И 32 и 33. Если на первом входе элемента . И 32 присутствует сигнал, то на его выходе появляется импульс, который поступает на входы стробирования элементов И 14 и 19, тем самым, разрешая перепись содержимого регистра 13 в счетчик адреса команд по выходу 66 и содержимого .блоков регистров 18 в арифметическое устройство ЭВМ по выходу 67 соответственно и восстанавливает состояние ЭВМ по выходу 67 соответственно и восстанавливает состояние ЭВМ на (i-l)-M шаге, а также на входе элемента 34 задержки. Импульс задержанный на время переписи содержимого регистра 13 и блока регистров 18 в арифметическое устройство ЭВМ, появляется на выходе 69 пуска устройства, тем самым, осуществляет пуск программ с (1-1)-й эталонной точки,

V.

Далее работа устройства повторяется аналогичным образом.

Если на первом входе элемента И 33 присутствует сигнал, то на его выходе,появляется импульс, который поступает на выход 70 устройства, который выводится на пульт оператора (не показан) и сигнализирует об ошибке в программе.

Формула изобретения

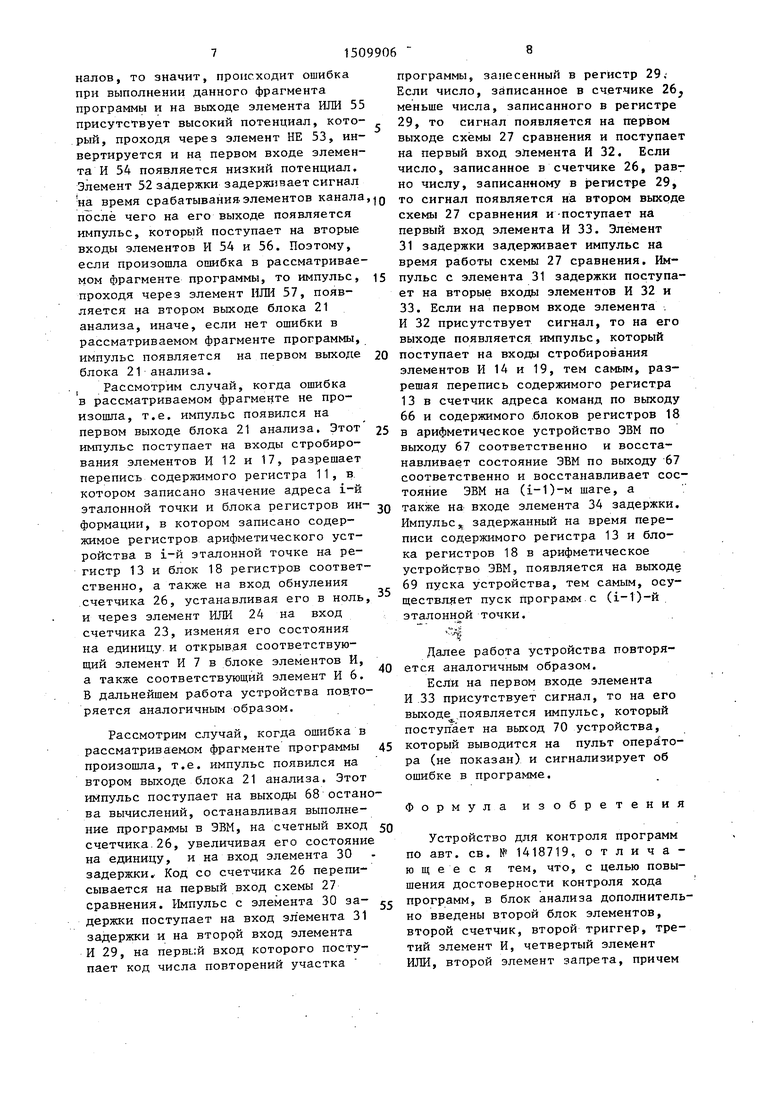

Устройство для контроля программ по авт. св. № 1418719, о т л и ч а - ю щ е е с я тем, что, с целью повышения достоверности контроля хода программ, в блок анализа дополнительно введены второй блок элементов, второй счетчик, второй триггер, третий элемент И, четвертый элемент ИЛИ, второй элемент запрета, причем

J15(

группа выходов второго блока эле- ментов И подключена к группе информационных входов второго счетчика, вычитающий вход которого соединен с выходом второго элемента запрета, выход признака обнуления второго счетчика подключен к нулевому входу второго триггера, единичный вход которого соединен с первым входом чет- вертого элемента ИЛИ и подключен к входу разрешения блока анализа, второй вход четвертого элемента ИЛИ объединен с первым входом третьего элемента И и подключен к входу зада- ния режима блока анализа, выход четвертого элемента ИЛИ соединен со

1П

стро)ирующим входом с второго блока элементов И, группа информагщонных входов которого подключена к второй группе иртформанионных входов блока анализа, прямой выход второго триггера подключен к второму входу третьего элемента И, выход которого подключен к третьему входу третьего элемента ИЛИ, инверсный выход второго триггера соединен с управляющим входом второго элемента запрета, инфор- ма1щонный вход которого подключен к выходу первого элемента запрета, второй вход четвертого элемента ИЛИ подключен к выходу второй схемы сравнения.

| Устройство для контроля программ | 1987 |

|

SU1418719A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1988-01-08—Подача