в

ел

Изобретение относится к вычислительной технике и может быть использовано в системах контроля оперативных запоминающих устройств.

Целью изобретения является повышение достоверности контроля памяти и расширение функциональных возможностей устройства - формирования тестов памяти за счет непрерывности прохождения тестов и возможности тестирования как всей, так и отдельных фрагментов проверяемой памяти.

На фиг. 1 изображена схема устройства для формирования тестов памяти; на фиг.2 - блок управления; на фиг.З - блок деления частоты.

Устройство содержит генератор 1 импульсов, блок 2 деления частоты, демуль- типлексор 3, счетчик 4 адреса, первый мультиплексор 5, блок 6 управления, блок 7 мультиплексоров, буферную память 8, блок

9элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй

10и третий 11 мультиплексоры, регистр 12 управляющего слова, четвертый мультиплексор 13. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и элемент И 15.

Устройство работает следующим образом.

После включения питания перед началом работы на вход 16 устройства подается сигнал начальной установки, который устанавливает блок управления в начальное состояние. .

Устройство работает в двух режимах, определяемых состоянием регистра 12 управляющего слова. В первом режиме в буферную память 8 осуществляют запись тестовой последовательности. Во втором режиме тестирования выполняют выдачу тестовых воздействий в обьект тестирования. В режиме записи фрагмент тестовой последовательности (адрес, слово данных, сигнал записи или чтения) записывается в буферную память 8, Тестирование может осуществляться как для полного объема памяти, так и для фрагмента памяти. При тестировании полного объема памяти адрес на адресный выход 17 устройства поступает через первый информационный вход 18 блока 7 мультиплексоров с информационного выхода 19 счетчика 4 адреса, а данные - на информационный выход 20 устройства через блок 9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с выхода 21 данных буферной памяти 8. При этом происходит многократное повторение фрагмента тестовой последовательности данных, записанного в буферной памяти, по всему объему памяти, информационная емкость которой больше, чем у буферной памяти, под управлением счетчика

адреса. При фрагментальном тестировании адрес на-адресный выход 17 устройства поступает через второй информационный вход 22 блока 7 мультиплексоров с адресно5 го выхода 23 буферной памяти 8, данные на информационный выход 20 устройства; поступают с выхода 21 данных буферной памяти. Сигнал управления записью-чтением в обоих режимах поступает с управляющего

0 выхода 24 буферной памяти на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, и после модификации сигналом с выхода четвертого мультиплексора подается на управляющий

выход 25 устройства.

5 В режиме записи в буферную память первоначально производится запись информации в регистр 12 управляющего слова. Эта информация формируется на информационном выходе 26 блока буправ0 ления. Занесение информации в регистр управляющего слова происходит по сигналу. записи на первом выходе 27 управления записью блока управления.

Выходы регистра 12 управляющего сло5 ва имеют следующее назначение: первый выход 28 блокирует уровнем Лог.О с выхода элемента И 15 работу генератора 1 импульсов, второй 29 и третий 30 выходы управляют блоком 2 деления частоты, чет0 вертый 31 выход подключен к входу управления направлением пересчета демультиплексора 3 и управляет работой счетчика 4 адреса на сложение или вычитание, пятый 32 и шестой 33 выходы подклю5 чены к первому и второму управляющим входам первого мультиплексора 5 и управляют длительностью теста, седьмой выход 34 подключен к входу управления адресами блока 7 мультиплексоров и управляет выбо0 ром источника адреса, восьмой выход 35 подключен к входу управления второго мультиплексора 10 и управляет сигналом выборки для буферной памяти 8, девятый 36 и десятый 37 выходы подключены к первому

5 и второму управляющим входам третьего мультиплексора 11 и управляют модификацией данных в блоке 9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, одиннадцатый 38 и . двенадцатый 39 выходы подключены к пер0 вому и второму управляющим входам четвертого мультиплексора 13 и управляют модификацией сигнала записи-чтение в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 14, тринадцатый 40 выход осуществляет сброс в нулевое

5 состояние счетчика 4 адреса сигналом низкого уровня.

Первое записанное в регистр 12 управляющее слово устанавливает на выходе 28

уровень Лог.О, блокируя работу генератора 1 импульсов, на выходе 40 - Лог.1,

запрещая сброс счетчика 4 адреса, на выходе 35 - Лог.О, соответствующий передаче мультиплексором 10 через второй информационный вход сигнала управления выборкой с выхода 41 управления выборкой блока 6 управления. Последнее означает, что управление выборкой буферной памяти осуществляется .через блок 6 управления сигналами на системном входе 16 устройства. Состояние остальных выходов регистра 12 управляющего слова в режиме записи является несущественным.

После указанной установки регистра 12 управляющего слова следует собственно, запись информации в буферную память 8. На системный вход 16 устройства подается адрес ячейки буферной памяти, который с информационного выхода 26 блока 6 управления поступает на адресный вход:42 счетчика 4 адреса и запоминается в счетчике по сигналу записи на первом выходе 43 управления записью блока 6 управления. Записанный адрес с информационного выхода 19 счетчика 4 адреса поступает на адресный вход 44 буферной памяти 8. Затем на системный вход 16 устройства подается код данных и разряд управления записью- чтением, который с выхода 26 блока 6 управления поступает на информационный вход 45 буферной памяти 8, и по сигналу записи с второго выхода 46 управления записью записывается в адресуемую ячейку буферной памяти 8. Таким образом производится заполнение всей буферной памяти тестовой информацией.

Для перевода устройства в режим выдачи тестовой последовательности производится сброс в нулевое состояние счетчика 4 адреса путем записи в регистр 12 управляющего слова с логическими нулями в первом и последнем разрядах. Затем в регистр 12 записывают управляющее слово, соответствующее требуемому тесту. При этом на вых оде 35 регистра 12 должно быть значение Лог.1, что соответствует подаче сигнала Лог.О с первого информационного входа 47 мультиплексора 10 на его выход, т.е. постоянной выборке буферной памяти 8. На выходе 40 регистра 12 устанавливается уровень Лог.1. Уровень Лог.1 на выходе 28 запускает генератор 1 импульсов. Значения сигналов на выходах 29 и 30 управляют выбором частоты синхроимпульсов тестирования в блоке 2 деления частотьгв соответствии с табл.1. Сигнал с выхода 31 регистра 12 управляет направлением перебора адресов. При уровне Лог.О происходит нарастание кода адреса, а при уровне Лог.1 - убывание кода адреса. Сигналы с выходов 32 и 33 управляют длительностью

теста в соответствии с табл.2. Первый - чет вертый информационные входы первой мультиплексора 5 подключены соответст венно к первому48 четвертому 51 выходаг.

старших разрядов, счетчика 4 адреса. Сиг нал Лог. выхода 34 подключает адрес ный выход. 17 устройства t информационному выходу Ш и второму выходу 52 счетчика 4 адреса для теетировани

0 по полному перебору адресов, Уровень Лог.1 на выходе 34 подключает адресный выход 17 к адресному выходу 23 буферной памяти 8 для тестирования фрагмента памяти по адресам, Записанным в буферной па5 мяти. Сигналы с выходов 36 vi 37 управляют выбором источника модификации кода данных на информационном выходе 20 устройства в соответствии с табл.3. К первому - четвертому входам-мультиплексора 11 под0 ключены cooTBeTcfBeHHO- выходы первого 53, второго 52, первого ста ршего 48 и второго старшего 49 разрядЬв;счётчи ка 4-дцреса. Сигнал из выбранного йстбчникаМодификации с выхода мултипле ксора 11 поступает

5 на управляющий вход 54 блокад элементов ИСКЛЮЧАЮЩЕЕ:ИЛИ: Информационный вход 55 этого блока подключен выходу 21

данных буферной памяти 8. Сигнал нггвходе 54 модифицирует код данных, фо рмируя на

0 выходе 20 прямой или инверсный-код (табл.3). Сигналы с выходов 38 и 39 выбирают источник модифицирующего сигнала записи-чтения на выходе 56 четвёртого мультиплексора 13. Источник модификации

5 подключается к второму входу 57 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 согласно б табл.4. Первый и второй входы -четвертого мультиплексора 13 подключены соответственно к первому 53 и второму 52f выходам счётчика

0 4 адреса, третий вход - к выходу 48 первого старшего разряда счётч ика 4 адреса, а на вход 58 подан уровень . J -L .

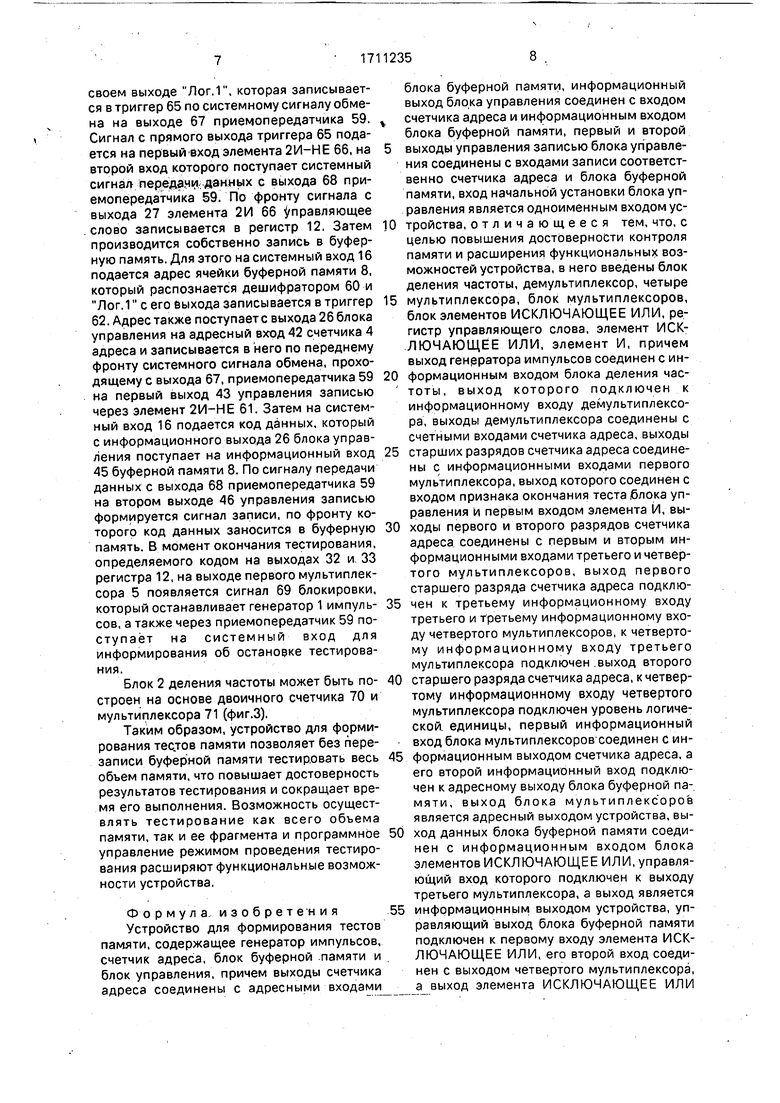

Блок 6 управления может бУтьреализован по схеме, представленной на фйг.2, и

5 содержит шинный приёмоперёдаҐч йк 59, дешифратор 60 адреса буферной ламяти, элемент 2И--НЕ 61, триггер 62, элёмент-2И- НЕ 63,-дешифратор 64 адреса регистра управляющего сло ва, триггер 65 и элемент 2И

0 66. - т:-: -

Блок управления работает следующим образом. По сигналу начальной установки с системного входа 16 триггеры 62 и 65-устанавливаются в состояние лог. О. В режиме

5 записи в буферную память код адреса принимается приемопередатчиками 59 и подается на информационный выход 26 блока управления. Одновременно дешифратор 64 адреса распознает обращение устройству через системный вход и устанавливает на

своем выходе Лог.1, которая записывается в триггер 65 по системному сигналу обмена на выходе 67 приемопередатчика 59. Сигнал с прямого выхода триггера 65 подается на первый вход элемента 2Й-НЕ 66, на второй вход которого поступает системный сигнал передачи;: данных с выхода 68 приемопередатчика 59. По фронту сигнала с выхода 27 элемента 2И 66 управляющее слово записывается в регистр 12. Затем производится собственно запись в буферную память. Для этого на системный вход 16 подается адрес ячейки буферной памяти 8, который распознается дешифратором 60 и Лог.1 сего выхода записывается в триггер 62. Адрес также поступает с выхода 26 блока управления на адресный вход 42 счетчика 4 адреса и записывается в него по переднему фронту системного сигнала обмена, проходящему с выхода 67. приемопередатчика 59 на первый выход 43 управления записью через элемент 2И-НЕ 61. Затем на системный вход 16 подается код данных, который с информационного выхода 26 блока управления поступает на информационный вход 45 буферной памяти 8. По сигналу передачи данных с выхода 68 приемопередатчика 59 на втором выходе 46 управления записью формируется сигнал записи, по фронту которого код данных заносится в буферную память. В момент окончания тестирования, определяемого кодом на выходах 32 и 33 регистра 12, на выходе первого мультиплексора 5 появляется сигнал 69 блокировки, который останавливает генератор 1 импульсов, а также через приемопередатчик 59 поступает на системный вход для информирования об остановке тестирования.

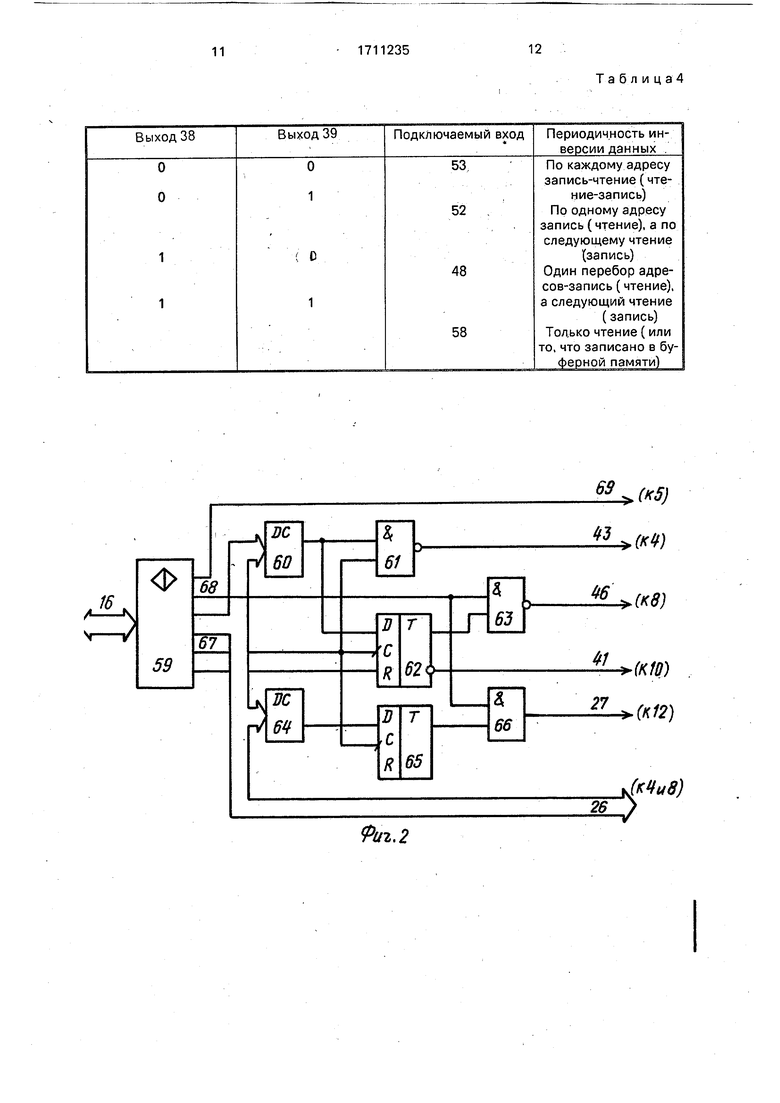

Блок 2 деления частоты может быть построен на основе двоичного счетчика 70 и мультиплексора 71 (фиг.З).

Таким образом, устройство для формирования тестов памяти позволяет без перезаписи буферной памяти тестировать весь объем памяти, что повышает достоверность результатов тестирования и сокращает время его выполнения. Возможность осуществлять тестирование как всего объема памяти, так и ее фрагмента и программное управление режимом проведения тестирования расширяют функциональные возможности устройства.

Формула, изобретения Устройство для формирования тестов памяти, содержащее генератор импульсов, счетчик адреса, блок буферной .памяти и блок управления, причем выходы счетчика адреса соединены с адресными входами

блока буферной памяти, информационный выход блока управления соединен с входом

счетчика адреса и информационным входом блока буферной памяти, первый и второй 5 выходы управления записью блока управления соединены с входами записи соответственно счетчика адреса и блока буферной памяти, вход начальной установки блока управления является одноименным входом ус10 тройства, отличающееся тем, что, с целью повышения достоверности контроля памяти и расширения функциональных возможностей устройства, в него введены блок деления частоты, демультиплексор, четыре

15 мультиплексора, блок мультиплексоров, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр управляющего слова, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, причем выход генератора импульсов соединен с ин0 формационным входом блока деления час тоты, выход которого подключен к

информационному входу демультиплексора, выходы демультиплексора соединены с

счетными входами счетчика адреса, выходы

25 старших разрядов счетчика адреса соединены с информационными входами первого мультиплексора, выход которого соединен с входом признака окончания теста .блока управления и первым входом элемента И, вы30 ходы первого и второго разрядов счетчика адреса соединены с первым и вторым информационными входами третьего и четвертого мультиплексоров, выход первого старшего разряда счетчика адреса подклю35 чен к третьему информационному входу третьего и третьему информационному входу четвертого мультиплексоров, к четвертому информационному входу третьего мультиплексора подключен .выход второго

40 старшего разряда счетчика адреса, к четвертому информационному входу четвертого мультиплексора подключен уровень логической, единицы, первый информационный вход блока мультиплексоров соединен с ин45 формационным выходом счетчика адреса, а его второй информационный вход подключен к адресному выходу блока буферной памяти, выход блока мультиплексоров является адресный выходом устройства, вы0 ход данных блока буферной памяти соединен с информационным входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющий вход которого подключен к выходу третьего мультиплексора, а выход является

5 информационным выходом устройства, управляющий выход блока буферной памяти подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, его второй вход соединен с выходом четвертого мультиплексора, а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

является управляющим выходом устройства, первый информационный вход второго мультиплексора подключен к уровню логического нуля, его второй информационный вход соединен с выходом управления вы- боркой блока управления, а его выход соединен с входом управления выборкой блока буферной памяти, информационный вход регистра управляющего слова соединен с информационным выходом блока управле- ния, а его вход записи соединен с третьим выходом управления записью блока управ-4 ления, выходы регистра управляющего сло

ва подключены соответственно к второму входу элемента И, первому и второму управляющим входам блока деления частоты, входу управления направления пересчета демультиплексора, первому и второму управляющим входам первого мультиплексора, входу управления адресами блока мультиплексоров, входу управления второго мультиплексора, первому и второму управляющим входам третьего мультиплексора, первому и второму управляющим входам четвертого мультиплексора, входом сброса в О счетчика адреса.

Т а б л и ц а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распаковки команд | 1984 |

|

SU1196865A1 |

| Устройство для отображения символьной информации на экране видеоконтрольного блока | 1991 |

|

SU1836678A3 |

| Многоканальный временной коммутатор | 1988 |

|

SU1647922A1 |

| Цифровой компенсатор выпадений телевизионного сигнала яркости | 1985 |

|

SU1269274A1 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1988 |

|

SU1499389A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Логический процессор | 1986 |

|

SU1315995A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах контроля оперативных запоминающих устройств. Целью изобретения является повышение достоверности контроля памяти и расширение функциональных воз-, можностей устройства. Устройство содегр- жит генератор 1 импульсов, блок 2 деления частоты, демультиплексор 3 счетчик4 адреса, первый мультиплексор 5,блок 6 управления, блок 7 мультиплексоров, буферную память 8, блок 9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй ТО и третий 11- мульти плексоры, регистр 12 управляющего слова, четвертый мультиплексор 13, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, элемент И 15. Уст- рой ство позволяет без перезаписи буферной памяти тестировать весь обье м памяти, что повышает достоверность результатов тестирования и сокращает время его выполнения. Возможность осуществ-- лять тестирование как всего объема памяти, дак и ее фрагмента и программное управление режимами проведения тестирования расширяют функциональные возможности устройства. 3 ил.,4 табл. ;; сл с

Таблица2

20

ТаблицаЗ

Таблица4

(ami)

Фиг.З

| Огнев И.В | |||

| и др | |||

| Методы и средства, контроля и диагностирования памяти ЭВМ | |||

| - М.: Моск.энерг., 1988, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

Авторы

Даты

1992-02-07—Публикация

1989-07-24—Подача