Изобретение относится к информационно-измерительной технике, может использоваться в адаптивных телеметрических системах.

Известно устройство для сокращения избыточности информации, содержащее блок сравнения, состоящий из элемента сравнения и порогового элемента, формирователь модели сигнала, состоящий из элемента памяти, двух ключей и элемент задержки, блок управления, состоящий из двух триггеров, двух элементов И, двух элементов задержки, формирователя импульсов, и ключ, которые соответствующим образом соединены между

собой,

Устройство имеет узкие функциональные возможности, так как обеспечивает выдачу только полного значения существенных отсчетов измеряемого параметра.

Известно устройство для сокращения избыточности информации, содержащее блок сравнения, состоящий из элемента сравнения и порогового элемента, формирователь модели (полного) сигнала, выполненный на элементе памяти, первом и втором ключах и элементе задержки, блок управления, выполненный на первом и втором триггерах, первом, втором и третьем элементах И, первом и втором элементах задержки, формирователе импульсов, элементе ИЛИ, и ключ, которые соответствующим образом соединены между собой.

Устройство имеет узкие функциональные возможности, так как обеспечивают выдачу только полного значения существенных отсчетов измеряемого параметра.

Цель изобретения - повышение информативности устройства путем обеспечения выдачи разностного сигнала между значеел

00 О

1751801

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сокращения избыточности информации | 1983 |

|

SU1100634A1 |

| Цифровое устройство для сличения частот | 1977 |

|

SU741178A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для сокращения избыточности информации | 1988 |

|

SU1541650A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровое устройство для сличения частот | 1978 |

|

SU1029092A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1984 |

|

SU1197085A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

Устройство для сокращения избыточности информации относится к информационно-измерительной технике, может использоваться в адаптивных телеметрических системах. Цель изобретения - повышение информативности устройства (путем обеспечения выдачи разностного сигнала между значениями текущего и предшествующего существенных отсчетов измеряемого параметра) Сущность изобретения состоит в том, что дополнительно введены: формирователь знака разностного сигнала, элемент задержки, формирователь модели разностного сигнала между значениями текущего и предшествующего существенных отсчетов измеряемого параметра, ключ и элемент И. В результате появляется возможность передачи не вСей величины измеряемого параметра, а только абсолютной величины ее приращения и знака приращения. Это, в свою очередь, обеспечит возможность либо увеличить скорость передачи информации за счет сокращения объема передаваемых сигналов, либо увеличить точность измерения величины параметра за счет увеличения разрядности информационной посылки, 4 з.п.ф-лы, 6 фиг.

ниями текущего существенного отсчета и предшествующего существенного отсчета измеряемого параметра.

Поставленная цель достигается тем, что в устройстве дополнительно введены формирователь знака разностного сигнала, первый и второй входы которого подключены соответственно к первому входу устройства и первому выходу формирователя модели полного сигнала, третий вход формирователя знака разностного сигнала объединен с входом элемента задержки и подключен к первому выходу формирователя модели разностного сигнала, первый и второй входы которого подключены соответственно к второму выходу блока сравнения и второму выходу блока управления, второй выход формирователя модели разностного сигнала соединен с сигнальным входом второго ключа, управляющий вход которого объединен с первым входом элемента И и подключен к первому выходу блока управления, второй вход элемента И подключен к выходу формирователя знака разностного сигнала, а выходы элемента задержки, второго ключа и элемента И соединены соответственно с вторым входом формирователя модели полного сигнала, четвертым и пятым выходами устройства,

Формирователь знака разностного сигнала содержит элемент сравнения, первый и второй входы которого подключены соответственно к первому и второму входам формирователя знака разностного сигнала, выход элемента сравнения соединен с объединенными вторыми входами первого и второго элементов И, первые входы которых объединены и подключены к третьему входу формирователя знака разностного сигнала, выходы первого и второго элементов И соединены соответственно с первым и вторым входами триггера, выход которого соединен с выходом формирователя знака разностного сигнала.

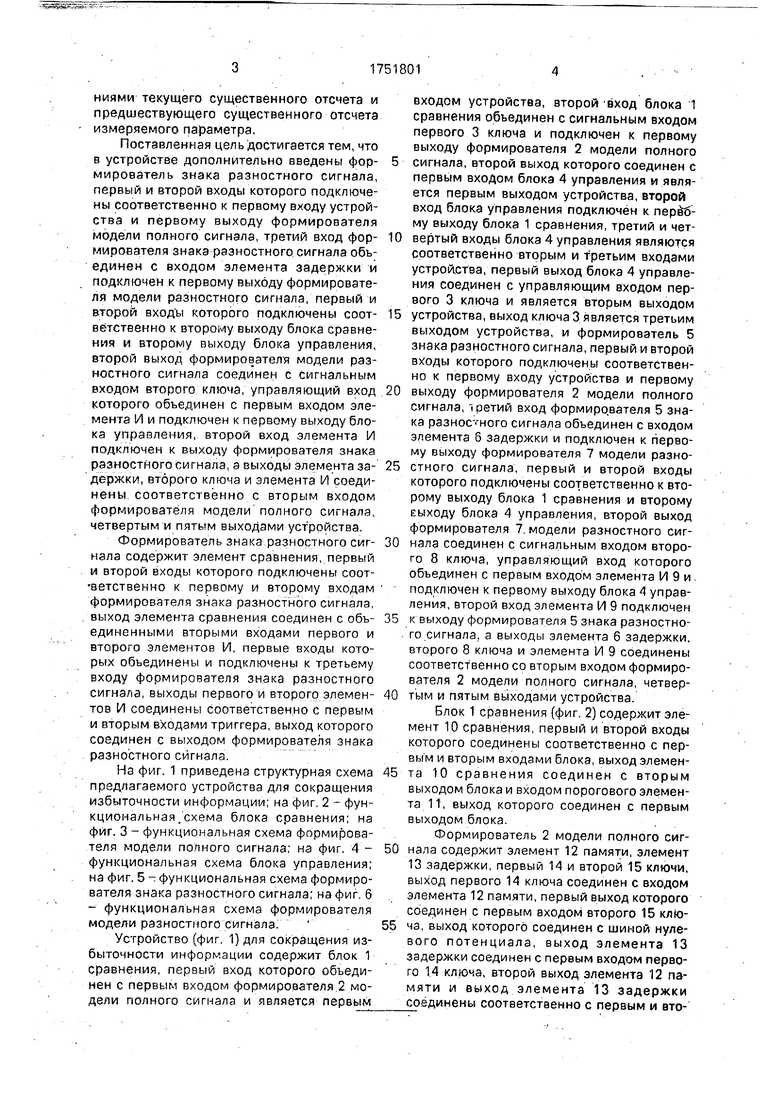

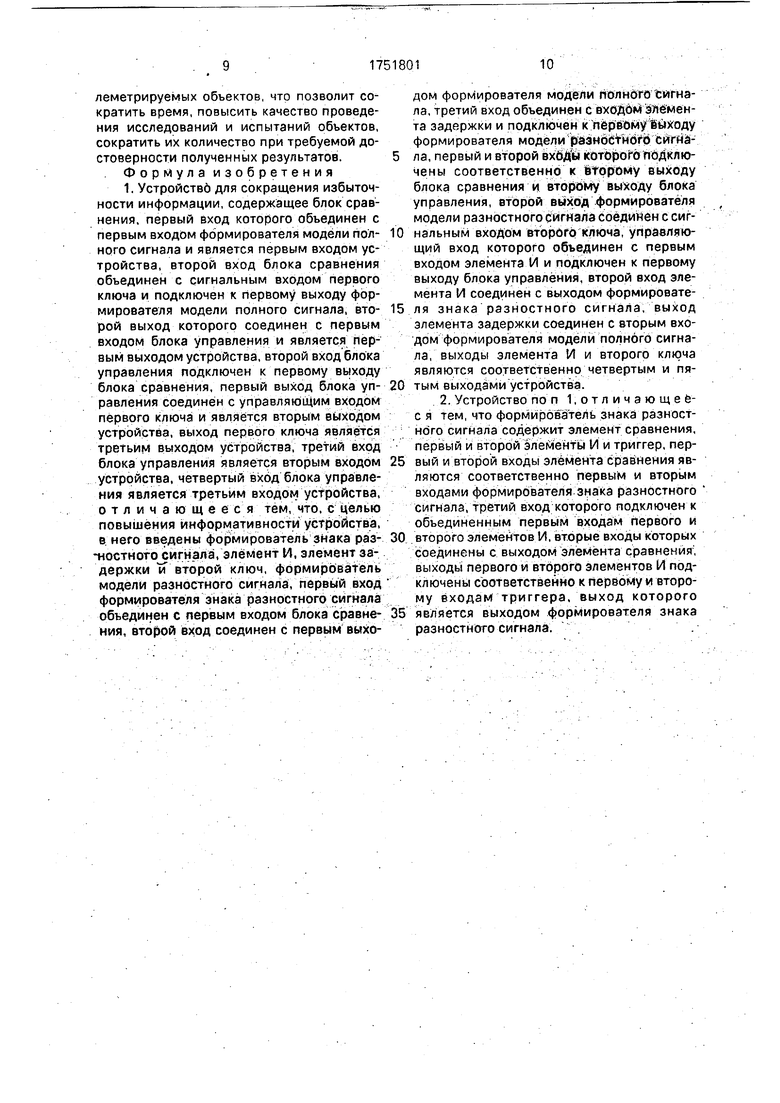

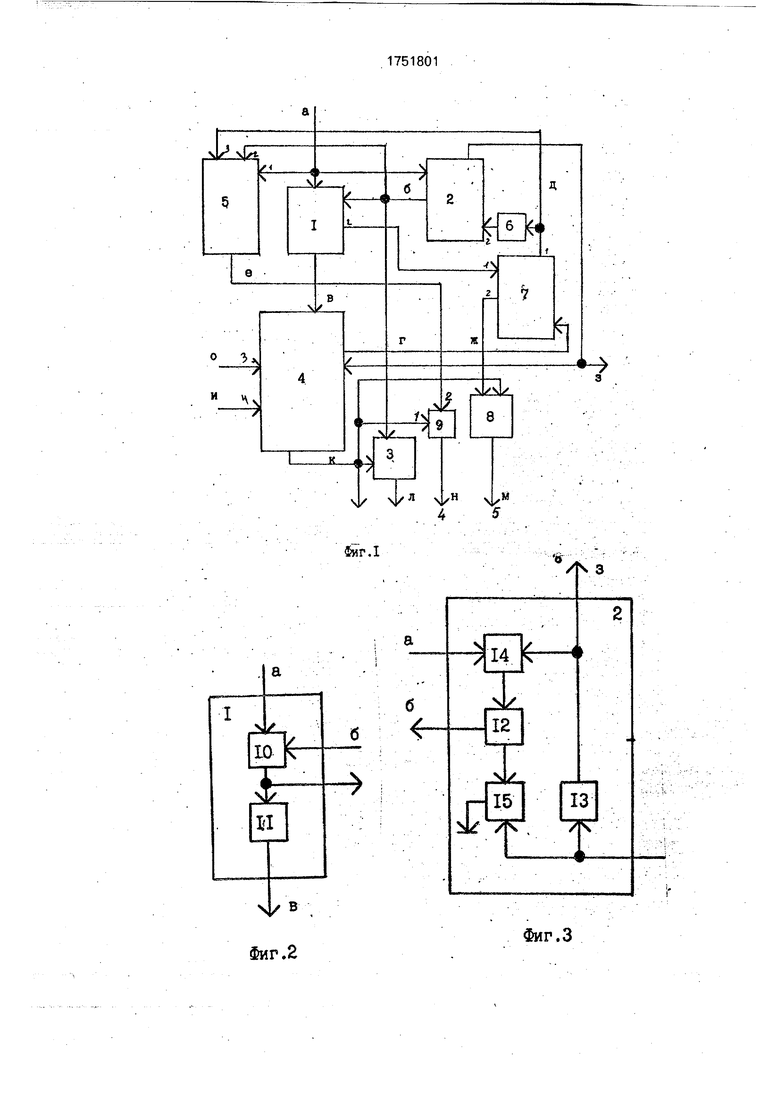

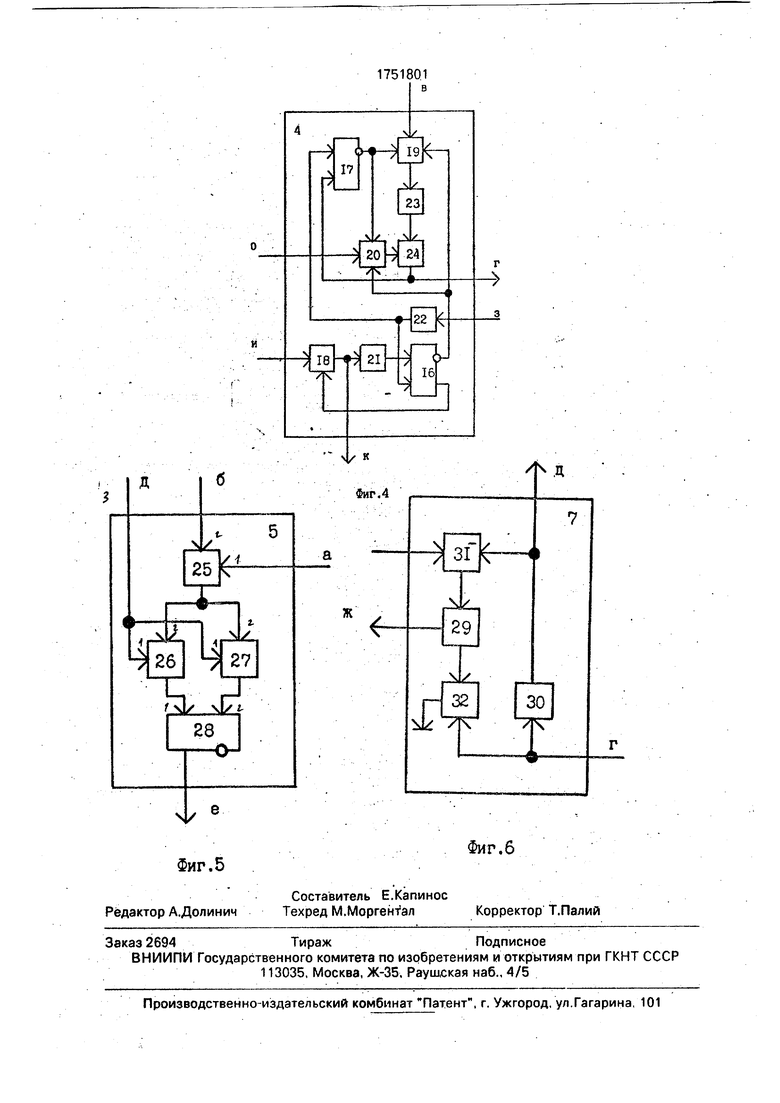

На фиг. 1 приведена структурная схема предлагаемого устройства для сокращения избыточности информации; на фиг. 2 - функциональная, схема блока сравнения; на фиг. 3 - функциональная схема формирователя модели попного сигнала; на фиг. 4 - функциональная схема блока управления; на фиг, 5 - функциональная схема формирователя знака разностного сигнала; на фиг 6 - функциональная схема формирователя модели разностного сигнала.

Устройство (фиг. 1) для сокращения избыточности информации содержит блок 1 сравнения, первый вход которого объединен с первым входом формирователя 2 модели полного сигнала и является первым

входом устройства, второй вход блока 1 сравнения объединен с сигнальным входом первого 3 ключа и подключен к первому выходу формирователя 2 модели полного

сигнала, второй выход которого соединен с первым входом блока 4 управления и является первым выходом устройства, второй вход блока управления подключен к перйб- му выходу блока 1 сравнения, третий и чет0 вертый входы блока 4 управления являются соответственно вторым и третьим входами устройства, первый выход блока 4 управления соединен с управляющим входом первого 3 ключа и является вторым выходом

5 устройства, выход ключа 3 является третьим выходом устройства, и формирователь 5 знака разностного сигнала, первый и второй входы которого подключены соответственно к первому входу устройства и первому

0 выходу формирователя 2 модели полного сигнала, третий вход формирователя 5 знака разностного сигнала объединен с входом элемента б задержки и подключен к первому выходу формирователя 7 модели разно5 стного сигнала, первый и второй входы которого подключены соответственно к второму выходу блока 1 сравнения и второму еыходу блока 4 управления, второй выход формирователя 7 модели разностного сиг0 нала соединен с сигнальным входом второго 8 ключа, управляющий вход которого объединен с первым входом элемента И 9 и подключен к первому выходу блока 4 управления, второй вход элемента И 9 подключен

5 к выходу формирователя 5 знака разностного сигнала, а выходы элемента 6 задержки, второго 8 ключа и элемента И 9 соединены соответственно со вторым входом формирователя 2 модели полного сигнала, четвер0 тым и пятым выходами устройства.

Блок 1 сравнения {фиг. 2) содержит элемент 10 сравнения, первый и второй входы которого соединены соответственно с первым и вторым входами блока, выход элемен5 та 10 сравнения соединен с вторым выходом блока и входом порогового элемента 11, выход которого соединен с первым выходом блока

Формирователь 2 модели полного сиг0 нала содержит элемент 12 памяти, элемент 13 задержки, первый 14 и второй 15 ключи, выход первого 14 ключа соединен с входом элемента 12 памяти, первый выход которого соединен с первым входом второго 15 клю5 ча, выход которого соединен с шиной нулевого потенциала, выход элемента 13 задержки соединен с первым входом первого 14 ключа, второй выход элемента 12 памяти и выход элемента 13 задержки соединены соответственно с первым и вторым выходами формирователя модели полного сигнала, объединенные вход элемента 13 задержки и второй вход второго 15 ключа соединены с вторым входом формирователя модели полного сигнала, второй вход первого 14 ключа соединен с первым входом формирователя модели полного сигнала.

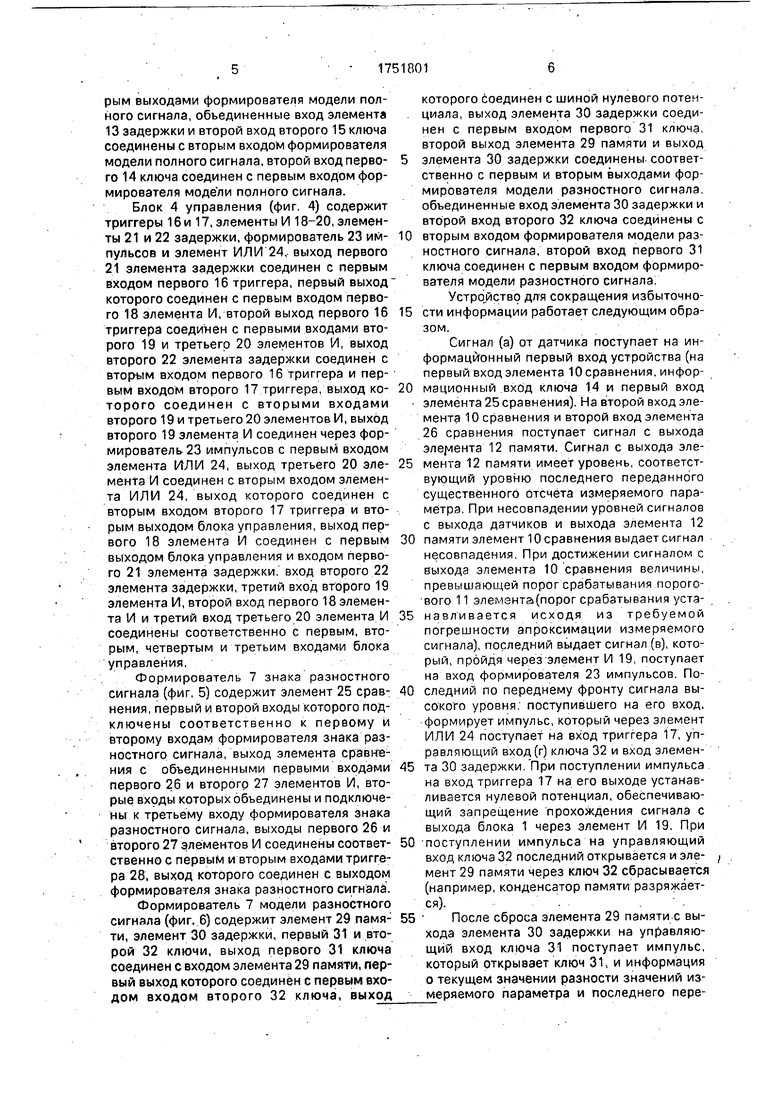

Блок 4 управления (фиг. 4) содержит триггеры 16 и 17, элементы И 18-20, элементы 21 и 22 задержки, формирователь 23 импульсов и элемент ИЛИ 24, выход первого 21 элемента задержки соединен с первым входом первого 16 триггера, первый выход которого соединен с первым входом первого 18 элемента И, второй выход первого 16 триггера соединен с первыми входами второго 19 и третьего 20 элементов И, выход второго 22 элемента задержки соединен с вторым входом первого 16 триггера и первым входом второго 17 триггера, выход которого соединен с вторыми входами второго 19 и третьего 20 элементов И, выход второго 19 элемента И соединен через формирователь 23 импульсов с первым входом элемента ИЛИ 24, выход третьего 20 элемента И соединен с вторым входом элемента ИЛИ 24, выход которого соединен с вторым входом второго 17 триггера и вторым выходом блока управления, выход первого 18 элемента И соединен с первым выходом блока управления и входом первого 21 элемента задержки, вход второго 22 элемента задержки, третий вход второго 19 элемента И, второй вход первого 18 элемента И и третий вход третьего 20 элемента И соединены соответственно с первым, вторым, четвертым и третьим входами блока управления,

Формирователь 7 знака разностного сигнала (фиг, 5) содержит элемент 25 сравнения, первый и второй входы которого подключены соответственно к первому и второму входам формирователя знака разностного сигнала, выход элемента сравнения с объединенными первыми входами первого 26 и второго 27 элементов И, вторые входы которых объединены и подключены к третьему входу формирователя знака разностного сигнала, выходы первого 26 и второго 27 элементов И соединены соответственно с первым и вторым входами триггера 28, выход которого соединен с выходом формирователя знака разностного сигнала.

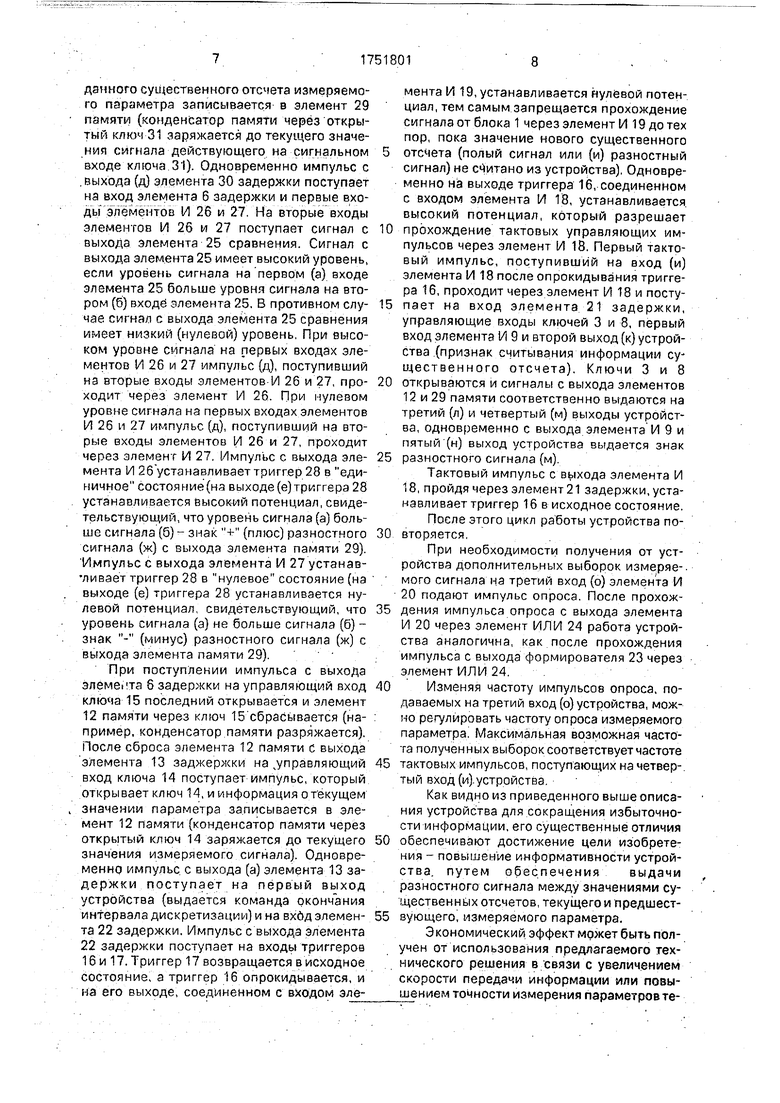

Формирователь 7 модели разностного сигнала (фиг. 6) содержит элемент 29 памяти, элемент 30 задержки, первый 31 и второй 32 ключи, выход первого 31 ключа соединен с входом элемента 29 памяти, первый выход которого соединен с первым входом входом второго 32 ключа, выход

которого соединен с шиной нулевого потенциала, выход элемента 30 задержки соединен с первым входом первого 31 ключа второй выход элемента 29 памяти и выход элемента 30 задержки соединены соответственно с первым и вторым выходами формирователя модели разностного сигнала объединенные вход элемента 30 задержки и второй вход второго 32 ключа соединены с

0 вторым входом формирователя модели разностного сигнала, второй вход первого 31 ключа соединен с первым входом формирователя модели разностного сигнала

Устройство для сокращения избыточно5 сти информации работает следующим образом.

Сигнал (а) от датчика поступает на информационный первый вход устройства (на первый вход элемента 10 сравнения, инфор0 мационный вход ключа 14 и первый вход элемента 25 сравнения). На второй вход элемента 10 сравнения и второй вход элемента 26 сравнения поступает сигнал с выхода элемента 12 памяти. Сигнал с выхода эле5 мента 12 памяти имеет уровень, соответствующий уровню последнего переданного существенного отсчета измеряемого параметра При несовпадении уровней сигналов с выхода датчиков и выхода элемента 12

0 памяти элемент 10 сравнения выдает сигнал несовпадения При достижении сигналом с выхода элемента 10 сравнения величины, превышающей порог срабатывания порогового 11 элемента(порог срабатывания уста5 навливается исходя из требуемой погрешности апроксимации измеряемого сигнала), последний выдает сигнал (в), который, пройдя через элемент И 19, поступает на вход формирователя 23 импульсов По0 следний по переднему фронту сигнала высокого уровня поступившего на его вход, формирует импульс, который через элемент ИЛИ 24 поступает на вход триггера 17, управляющий вход (г) ключа 32 и вход элемен5 та 30 задержки При поступлении импульса на вход триггера 17 на его выходе устанавливается нулевой потенциал, обеспечивающий запрещение прохождения сигнала с выхода блока 1 через элемент И 19. При

0 поступлении импульса на управляющий вход ключа 32 последний открывается и эле- / мент 29 памяти через ключ 32 сбрасывается (например, конденсатор памяти разряжается).

5 После сброса элемента 29 памяти с выхода элемента 30 задержки на управляющий вход ключа 31 поступает импульс, который открывает ключ 31, и информация о текущем значении разности значений измеряемого параметра и последнего переданного существенного отсчета измеряемого параметра записывается в элемент 29 памяти (конденсатор памяти через открытый ключ 31 заряжается до текущего значения сигнала действующего на сигнальном входе ключа 31). Одновременно импульс с выхода (д) элемента 30 задержки поступает на вход элемента 6 задержки и первые входы элементов И 26 и 27. На вторые входы элементов И 26 и 27 поступает сигнал с выхода элемента 25 сравнения. Сигнал с выхода элемента 25 имеет высокий уровень, если уровень сигнала на первом (а) входе элемента 25 больше уровня сигнала на втором (б) входе элемента 25, В противном случае сигнал с выхода элемента 25 сравнения имеет низкий (нулевой) уровень, При высоком уровне сигнала на первых входах элементов И 26 и 27 импульс (д), поступивший на вторые входы элементов И 26 и 27, проходит через элемент И 26. При нулевом уровне сигнала на первых входах элементов И 26 и 27 импульс (д), поступивший на вторые входы элементов И 26 и 27, проходит через злеменг И 27. Импульс с выхода элемента И 26 устанавливает триггер 28 в единичное состояние (на выходе (е) триггера 28 устанавливается высошй потенциал, свидетельствующий, что уровень сигнала (а) больше сигнала (б) - знак + (плюс) разностного сигнала (ж) с выхода элемента памяти 29). Импульс с выхода элемента И 27 устанавливает триггер 28 в нулевое состояние (на выходе (е) триггера 28 устанавливается нулевой потенциал свидетельствующий, что уровень сигнала (а) не больше сигнала (б) - знак - (минус) разностного сигнала (ж) с выхода элемента памяти 29).

При поступлении импульса с выхода элемента 6 задержки на управляющий вход ключа 15 последний открывается и элемент 12 памяти через ключ 15 сбрасывается (например, конденсатор памяти разряжается). После сброса элемента 12 памяти с выхода элемента 13 заджержки на управляющий вход ключа 14 поступает импульс, который открывает ключ 14, и информация отекущем значении параметра записывается в элемент 12 памяти (конденсатор памяти через открытый ключ 14 заряжается до текущего значения измеряемого сигнала). Одновременно импульс с выхода (а) элемента 13 задержки поступает на первый выход устройства (выдается команда окончания интервала дискретизации) и на вхбд элемента 22 задержки. Импульс с выхода элемента 22 задержки поступает на входы триггеров 16 и 17. Триггер 17 возвращается в исходное состояние, а триггер 16 опрокидывается, и на его выходе, соединенном с входом элемента И 19, устанавливается нулевой потенциал, тем самым запрещается прохождение сигнала от блока 1 через элемент И 19 до тех пор, пока значение нового существенного

отсчета (полый сигнал или (и) разностный сигнал) не считано из устройства), Одновременно на выходе триггера 16, соединенном с входом элемента И 18, устанавливается высокий потенциал, который разрешает

0 прохождение тактовых управляющих импульсов через элемент И 18. Первый тактовый импульс, поступивший на вход (и) элемента И 18 после опрокидывания триггера 16, проходит через элемент И 18 и посту5 пает на вход элемента 21 задержки, управляющие входы ключей 3 и 8, первый вход элемента И 9 и второй выход (к) устройства (признак считывания информации существенного отсчета). Ключи 3 и 8

0 открываются и сигналы с выхода элементов 12 и 29 памяти соответственно выдаются на третий (л) и четвертый (м) выходы устройства, одновременно с выхода элемента И 9 и пятый (н) выход устройства выдается знак

5 разностного сигнала(м)

Тактовый импульс с выхода элемента И 18, пройдя через элемент 21 задержки, устанавливает триггер 16 в исходное состояние. После этого цикл работы устройства по0 вторяется.

При необходимости получения от устройства дополнительных выборок измеряемого сигнала на третий вход (о) элемента И 20 подают импульс опроса. После прохож5 дения импульса опроса с выхода элемента И 20 через элемент ИЛИ 24 работа устройства аналогична, как после прохождения импульса с выхода формирователя 23 через элемент ИЛИ 24.

0 Изменяя частоту импульсов опроса, подаваемых на третий вход (о) устройства, можно регулировать частоту опроса измеряемого параметра. Максимальная возможная частота полученных выборок соответствует частоте

5 тактовых импульсов, поступающих на четвертый вход (и)устройства

Как видно из приведенного выше описания устройства для сокращения избыточности информации, его существенные отличия

0 обеспечивают достижение цели изобретения - повышение информативности устройства, путем обеспечения выдачи разностного сигнала между значениями существенных отсчетов, текущего и предшест5 вующего, измеряемого параметра.

Экономический эффект может быть получен от использования предлагаемого технического решения в связи с увеличением скорости передачи информации или повышением точности измерения параметров телеметрируемых объектов, что позволит сократить время, повысить качество проведения исследований и испытаний объектов, сократить их количество при требуемой достоверности полученных результатов. Формула изобретения 1. Устройство для сокращения избыточности информации, содержащее блок сравнения, первый вход которого объединен с первым входом формирователя модели полного сигнала и является первым входом устройства, второй вход блока сравнения объединен с сигнальным входом первого ключа и подключен к первому выходу формирователя модели полного сигнала, второй выход которого соединен с первым входом блока управления и является первым выходом устройства, второй вход блока управления подключен к первому выходу блока сравнения, первый выход блока управления соединен с управляющим входом первого ключа и является вторым выходом устройства, выход первого ключа является третьим выходом устройства, третий вход блока управления является вторым входом устройства, четвертый вход блока управления является третьим входом устройства, отличающееся тем, что, с целью повышения информативности устройства, в него введены формирователь знака раз- -ностното сигнала, элемент И, элемент задержки л второй ключ, формирователь модели разностного сигнала, первый вход формирователя знака разностного сигнала объединен с первым входом блока сравнения, второй вход соединен с первым выходом формирователя модели полного сигнала, третий вход объединен с входом элемента задержки и подключен к первому выходу формирователя модели разностного сйгнала, первый и второй входы которого подклю- чены соответственно к второму выходу блока сравнения и второму выходу блока управления, второй выход формирователя модели разностного сигнала соединен с сигнальным входом второго ключа, управляющий вход которого объединен с первым входом элемента И и подключен к первому выходу блока управления, второй вход элемента И соединен с выходом формирователя знака разностного сигнала, выход элемента задержки соединен с вторым входом формирователя модели полного сигнала, выходы элемента И и второго ключа являются соответственно четвертым и пятым выходами устройства.

2 Устройство поп 1,отличающее- с я тем, что формирователь знака разностного сигнала содержит элемент сравнения, первый и второй элементы И и триггер, первый и второй входы элемента сравнения являются соответственно первым и вторым входами формирователя знака разностного сигнала, третий вход которого подключен к объединенным первым входам первого и

второго элементов И, вторые входы которых соединены с выходом элемента сравнения, выходы первого и второго элементов И подключены соответственно к первому и второму входам триггера, выход которого

является выходом формирователя знака разностного сигнала.

V/

е

Фиг. 5

Редактор А.Долинич

Составитель Е.Капинос Техред М.МоргенУал

Фиг.б

Корректор Т.Палий

| Устройство для сокращения избыточности информации | 1987 |

|

SU1425755A2 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1992-07-30—Публикация

1990-11-21—Подача