Изобретение относится к вычисли- тельной технике и может быть использовано в управляющих ЦВМ объектов, к которым предъявляются повышенные требования к достоверности переработки информации.

Цель изобретения - упрощение сум- aтopa,

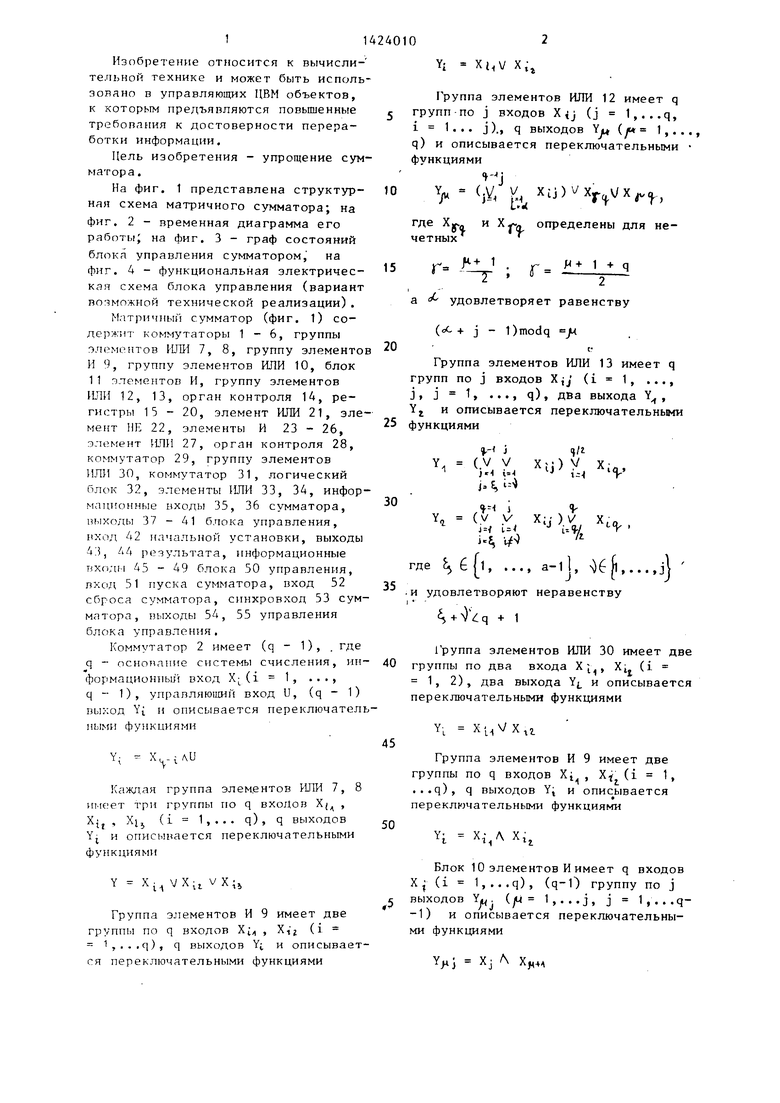

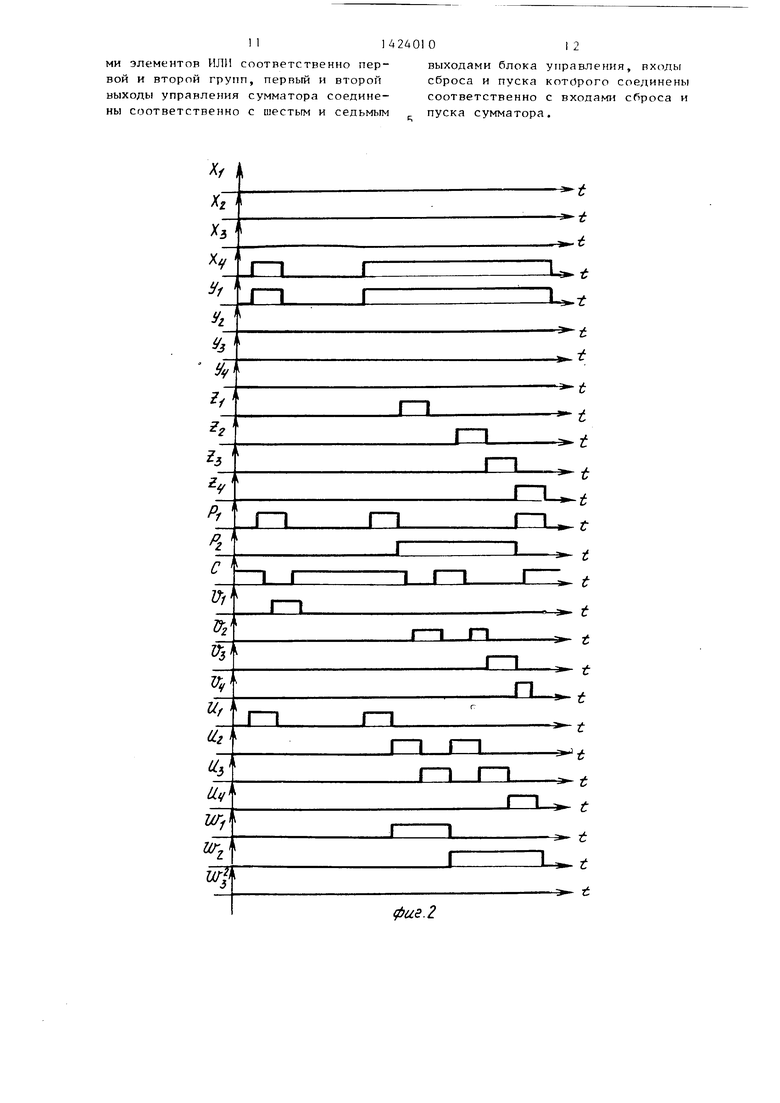

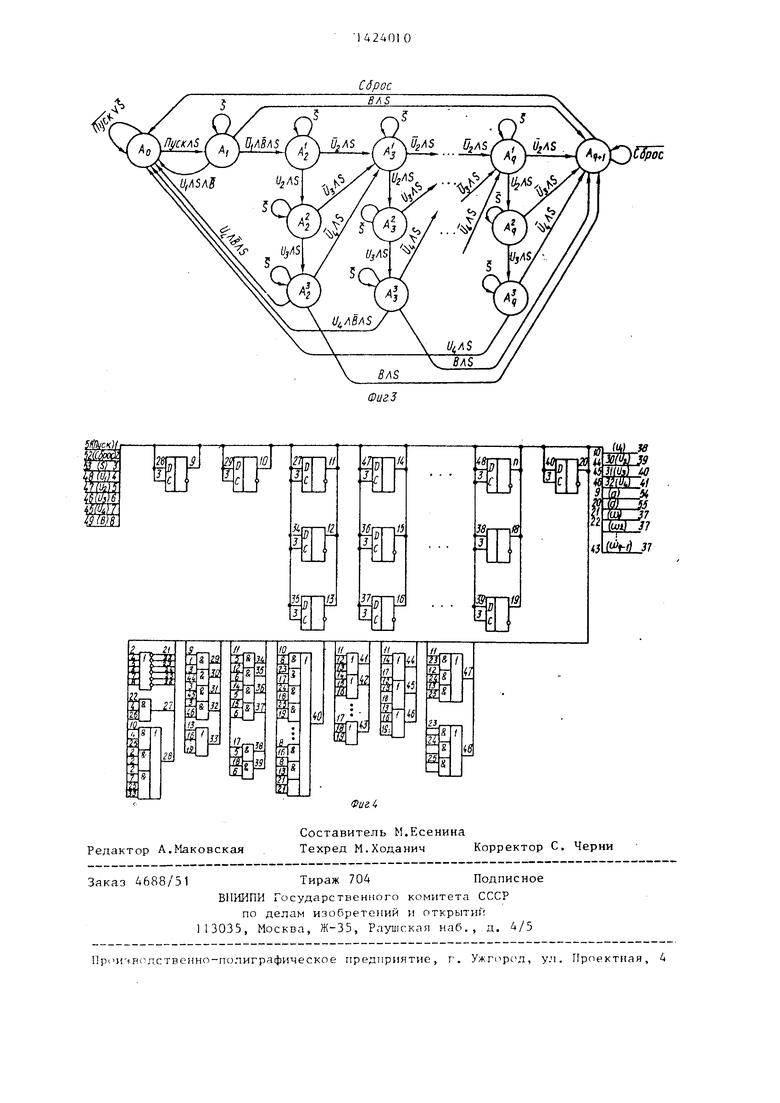

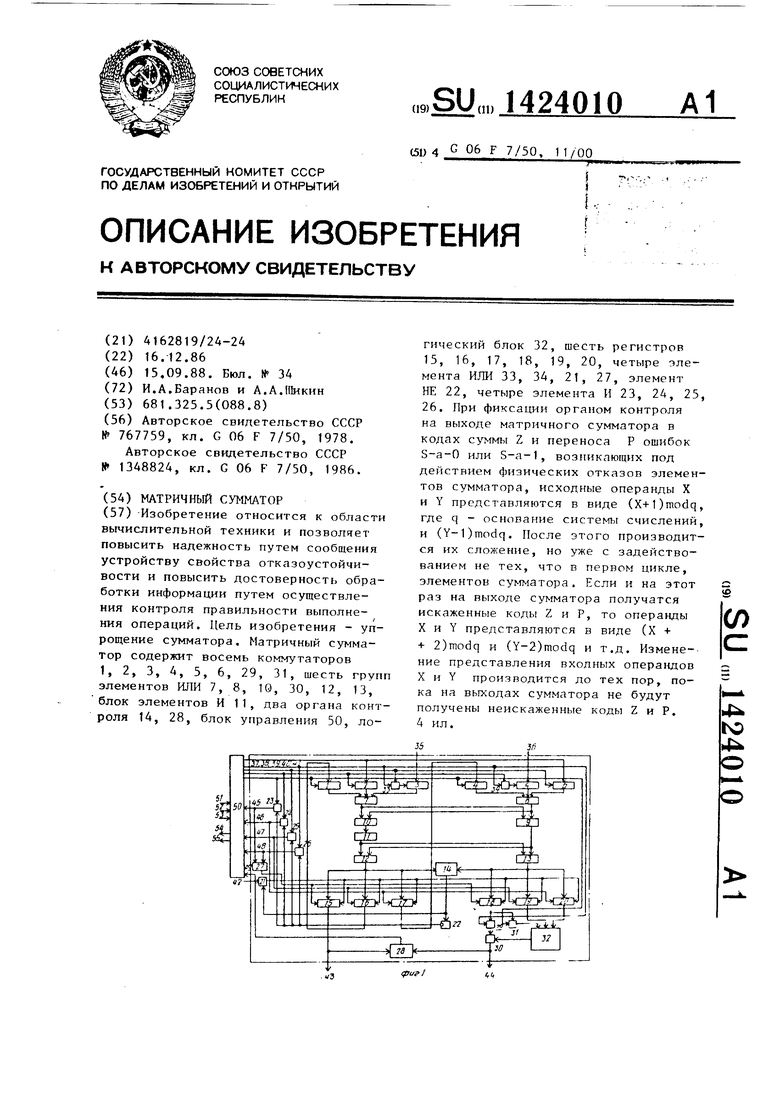

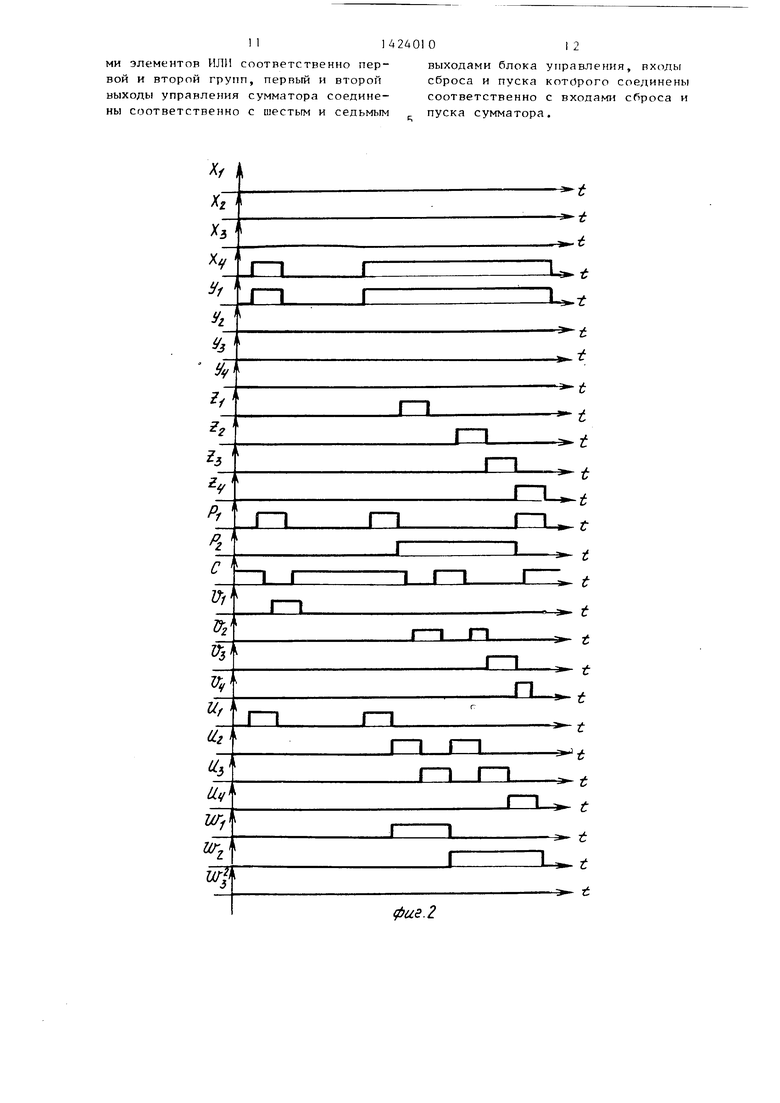

На фиг. 1 представлена структур- нал схема матричного сумматора; на фиг. 2 - временная диаграмма его работы на фиг. 3 - граф состояний блока управления сумматором, на фиг. 4 - функциональная электрическая схема блока управления (вариант возможной технической реализации).

Матричный сумматор (фиг. 1) со- коммутаторы 1-6, группы элементов ИЛИ 7, 8, группу элементов И 9, группу элементов ИЛИ 10, блок 1 1 гэлементов И, группу элементов 1ШИ 12, 13, орган контроля 14, регистры 15 - 20, элемент ИЛИ 21, элемент НЕ 22, элементы И 23 - 26, элемент ЯПИ 27, орган контроля 28, коммутатор 29, группу элементов ИЛИ 30, коммутатор 31, логический блок 32, элементы ИЛИ 33, 34, информационные входы 35, 36 сумматора, выходы 37 - 41 блока управления, иход 42 начальной установки, выходы 43, 44 результата, информационные пходы 45 - 49 блока 50 управления, пход 51 пуска сумматора, вход 52 сброса сумматора, синхровход 53 сумматора, выходы 54, 55 управления блока управления.

Коммутатор 2 имеет (q - 1), , где q - оснопацие системы счисления, ив- формационньш вход Х(i 1, , q - 1), управляющий вход U, (q - 1) выход Yi и описывается переключательными функциями

YI Xi,

Группа элементов ИЛИ 12 имеет q групп по j входов Xij (j 1,...q, i 1... j)., q выходов Y (yc« 1,.. q) и описывается переключательными функциями

.j

(jV, f{ Xij)v/x,.,.

и X

IV

rf

определены для не

г

ft+ 1

г 1 +

о

а оо удовлетворяет равенству (сС + j - Dmodq /(

с:

Группа элементов ИЛИ 13 имеет q групп по j входов Xjj (i 1, ..., j J 1 ., q), два выхода Y, Yj и описывается переключательными функциями

Y.

YO

где , .... a-lj, -06f,...,j

.и удовлетворяют неравенству

I

+ V q + 1

1 руппа элементов ИЛИ 30 имеет две группы по два входа Х, Х (i 1, 2), два выхода Yj и описывается переключательными функциями

Y,

И

VX

гг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный сумматор | 1986 |

|

SU1348824A1 |

| Матричный сумматор | 1987 |

|

SU1582187A1 |

| Матричный сумматор | 1987 |

|

SU1545217A1 |

| Устройство для вычитания | 1987 |

|

SU1418703A1 |

| Устройство для последовательного деления | 1986 |

|

SU1304017A1 |

| Вычислительное устройство | 1983 |

|

SU1080135A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Вычислительное устройство | 1984 |

|

SU1203513A1 |

| Параллельный синтаксический анализатор | 1987 |

|

SU1465894A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

Изобретение относится к области вычислительной техники и позволяет повысить надежность путем сообщения устройству свойства отказоустойчивости и повысить достоверность обработки информации путем осуществления контроля правильности выполнения операций. Цель изобретения - упрощение сумматора. Матричный сумматор содержит восемь коммутаторов 1, 2, 3, 4, 5, 6, 29, 31, шесть групп элементов ИЛИ 7, 8, 10, 30, 12, 13, блок элементов И 11, два органа контроля 14, 28, блок управления 50, ло.«3 гический блок 32, шесть регистров 15, 16, 17, 18, 19, 20, четыре элемента ИЛИ 33, 34, 21, 27, элемент НЕ 22, четыре элемента И 23, 24, 25, 26. При фиксации органом контроля на выходе матричного сумматора в кодах Z и переноса Р ошибок S-a-0 или S-a-1, возникающих под действием физических отказов элементов сумматора, исходные операнды X и Y представляются в виде (X+1)modq, где q - основание системы счислений, и (Y-1)modq. После этого производится их сложение, но уже с задействованием не тех, что в первом цикле, элементов сумматора. Если и на этот раз на выходе сумматора получатся искаженные коды Z и Р, то операнды X и Y представляются в виде (X + + 2)rnodq и (Y-2)modq и т.д. Измене-. ние представления входных операндов X и Y производится до тех пор, пока на выходах сумматора не будут получены неискаженные коды Z и Р, 4 ил. 35 (Р (Л и ю Ui о (риг

Каждая группа элементов ИЛИ 7, имеет три группы по q входов Х; ,

X Y,

tz

Xij (i 1,... q), q выходов описывается переключательными

функциями

У

Х;,

Группа элементов И 9 имеет две группы по q входов Xi , Xt (i 1,..,q), q выходов Yi и описывается переключательными функциями

Группа элементов И 9 имеет две группы по q входов Xi , Х (i 1, ...q), q выходов Y; и опис ывается переключательными функциями

50

YI

l Хг,

Блок 10 элементов И имеет q входов Х| (i 1,...q), (q-0 группу по j выходов Y (д( 1,...j, j 1,. ..q- -1) и описывается переключательными функциями

j

31/I2/-.01

Органы контроля 14, 28 имеют по лве группы входов Х{ , Х; (, . Ч J 2), выход Y и описываются переключательными функциями

«V-i ( .

Y V, 5 . (.OV CA X;,)l ,

X,,)V(X,,,A Х,г-)

Комбинационная схема 32 имеет три группы по два входа X , , Х. X,j (i 1, 2), два выхода Y , Y и описывается переключательными функциями

Y, ( Хгг АХ,1 )V(XHA .Л А X,.,)V(X,, А X,,, )V

v/(x, Л л Х,А);

Y2 (,j, Л Xjj )V(,,))/

У(Х,ЛХ,гАХ,,, )V(X . Л Xi.,)

Матричный сумматор функционирует в двух режимах: первый режим имеет место при отсутствии в матричном сумматоре отказов элементов или отсутствии их влияния на искажение выходной информации сумматора при данных входных наборах, а второй режим - при фиксации на выходе сумматора логической ошибки S-a-0 или S-a-1 при данных входных наборах. Работа матричного сумматора в каждом из этих режимов поясняется с помощью времен- ной диаграммы, представленной на фиг. 2.

Управление матричным сумматором осуществляет блок 50 управления, построенный на основе регистров с перемещаемыми единицами. Граф переходов состояний блока приведен на фиг. 3, где Ар, А, А,, А (i 1, 2 3, j 2, ..., q +1) - состояния блока, а на дугах указаны условия переходов, гфичем обозначения, принятые на графе, соответствуют обозначениям на фиг. 4, на которой приведен один из возможных вариантов конкретной реализации блока 50.

Данный блок 50 содержит 3(q -- 1) DC-триггера. Функции возбуждения блока 50, как это Г7оказано на фиг . 4, построены на логических элементах

0

5

0

5

0 5 0

5 g е

О

6НЕ, ЗИ, 3-ЗИ-ИЛИ, 4-2И, (q - 1)1ШИ, 2(q - 1)-2И, (q + 2)-2П-ЯЛИ, (q - - 1)-ЗИЛИ, 3-(q - 1) ИЛИ и (q - 2) элементах 3-2И-ИЛИ.

Рассмотрим работу матричного сумматора, например, для q 4, X 3 и Y О в первом режиме, а именно при отсутствии в нем физических отказов элементов или отсутствии их влияния на искажение выходной информации сумматора.

Одновременно с поступлением на информационные входы 35 и 36 сумматора операндов X и Y, представленных п кодах с позиционным представлением цифр системы счисленш (на временной диаграмме фиг. 2 данным кодам соответствуют сигналы Х и Y , на входе 51 блока 50 управления формируется сигнал Пуск, под воздействием которого блок 50 формирует сигнал U на вход 38 сумматора. Данный сигнал с входа 38 открывает через элементы ШТИ 33, 34 входные коммутаторы 3, 5. В результате этого коды операндов X 5 и Y О поступают через узлы

элементов {ПИ 7 и 8 на узлы элементоц ИЛИ 10 и элементов И 9.

Коммутация кодов операндов X и Y на узлы 10 и 9 приводит к тому, что на входах узла элементов ИЛИ 12 формируется сигнал 7.А , который соответствует сумме

Z (X + Y),

а на выходах узла элементов ИЛИ 13 - сигнал Р переноса Р 0.

Данные сигналы (коды) анализируются органом контроля 14. Так как в соответствии с нашим допущением о выборе режима функционирования матричного сумматора коды Z и Р не имеют логических ошибок, то орган контроля

14снимает со своего выхода сигнал

С ошибки (фиг. 2). Отсутствие данного сигнала С ошибки приводит к появле- нию сигнала V на выходе 48 матричного сумматора и к записи в регистры

15и 18 кодов Z 3 и переноса Р 0. После данной записи коды Z и

Р вновь контролируются, код Р посту- пает на орган контр ьтя 28 через открытый коммутатор 29 и группу элементов ИЛИ 30. При отсутствии в кодах Z и Р, поступивших на пыхо;н 43 и 44

51А

мат ричного сумматора, логических ошибок S-a-0 или S-a-1 сигнал ошибки на выход А9 не поступает и блок 50 управления форми11ует на выходе Ъ сиг нал успешного окончания операции, В этом случае, если в результате записи п выходные регистры 15 и 18 в кодах Z и Р возникает ошибка одной из категорий S-a-0 или S-a-1, то сигнал ошибки b с выхода 4Э сумматора приводит к гтоявлению сигнала на выходе 55 блока 50 управления. Наличие сиг- 1П, га на данном выходе свидетельствует об отказе матричного сумматора и невозможности получения на его выходах неискаженного результата при данных входных наборах (кодах X 3 и Y - 0).

Рассмотрим работу матричного сум- MnTojia вс-. втором режиме, а именно при фи1,с:лиии органом контроля 14 ошибки о/июй из категорий S-a-0 или S-a-1 Г ь,:оде Z или Р при поступлении на ин- (t)oiiMnn, входы 35 и 36 кодов X - 3 и Y 0.

Сл1гр1ал С с выхода органа контроля 1Л через элемент НЕ 22 закрывает .ni i.seuT 23, В этом случае сигнал V г ы;-соде 48 Tie формируется, на что О. :пк 50 управления отвечает вы- ррСоткой Uj на нход 39 и сигнала Wj па первый вход группы управдяющих входоп 37.

Упрат ллктаий сигнал 1 г открывает пммутат(ры 3 и 6, что приводит к формированию на выходах узлов элемен- Toj ИЛИ 12, 13 кодов

Z (X + Dmodq О,

v 1-

На временной диаграмме (фиг. 2) дап11Ь м кгхдам соответствуют сигналы

Z, и Р, .

Иоско.чьку в этом случае при формировании кодов Z и Р передача сиг- наноп осуществляется не по тем цепям, что в первом цикле формирования код(зв Z и Р, а по другим, то при этом происходит исключение вл 1яния на искажение выходной информации сумматора физических отказов, проявив- 1лихся в первом цикле.

Пусть в данных кодах Z и Р ошибки S-a-0 и S-a-1 отсутствуют. Тогда орг ан контроля 14 формирует на выходе 47 сигнал V,, а блок 50 управлеь:ия - сигнал U

на вход 40 и

10

сигнал W на первый вход управляющих входов 37. Под действием сигнала V код Z записывается в регистр 16, а код Р - в регистр 19.

Управляюп1ИЙ сигнал Uj открывает коммутаторы 2 и 5. При зтом коммутатор 2 коммутирует сигнал W со своего первого входа на третий выход, что равносильно преобразованию кода 1 в код 3.

R результате данной коммутации на выходах узлов элементов ИЛИ 12 и 13 формируются коды соответственно:

z (Y + 3)raod4 (Y - 1)

и Р

На временной диаграмме (фиг. 2) данным кодам соответств1уют сигналы и Р .

Пусть в связи с наличием в матричном сумматоре физических отказов сигнал Z, не формируется. Тогда на выходе органа контроля 1А будет получен сигнал С ошибки, а на выходе 46 сигнал будет отсутствовать. При этом сигнал С ошибки сбрасывает все триггеры 15-20, блок 50 управления вьфабатывает сигнал Wj на второй вход группы входов 37 и сигнал U на вход 39. Таким образом, в следующем цикле работы сумматора на выходах групп элементов ИЛИ 12, 13 формируются коды соответственно;

z (X ч- 2),

т

и Р

-

На временной диаграмме фиг. 2 дан; ным кодам соответствуют сигналы и Р., .

Пусть в данных кодах Z и ошибки S-a-0 и S-a-1 отсутствуют. Тогда орган контроля 14 формирует на выходе 47 сигнал V , блок 50 управления - сигнал Uj на вход -40 и сигнал W на второй вход группы управля- Ш(их входов 37. При этом сигнал Vj записывает код Z в регистр 16, код Р - в регистр 19, а на выходах элементов ИЛИ 12 и 13 формируются коды соответственно

(У + 2)mod4 (Y - 2)

n v

7U

На временной диаграмме (фиг. 2) данным кодам соответствуют сигналы Zj и Рг .

Пусть в кодах и р ошибки S -а-0 и S -а-1 отсутствуют. Тогда орган контроля 14 формирует сигнал Vj на выходе 46, который записывает коды Z и Р в регистры 17 и 20, а блок 50 управления формирует сигна- лы Ux на вход 41,

Управляющий сигнал И открывает кокп утаторы 1 и 4. При этом на выходы узлов элементов ИЛИ 12 и 13 поступают коды,

Z - Z - 2)mod4

о

(X + 2)raod4 + (X + Y)inod4 З;

На временной диаграмме (фиг. 2) данным кодам соответствуют сигналы Z и Р, .

Если в этих кодах и ошибки S-a-0 и S-a-1 отсутствуют, то сигнал

V V

V записывает коды Z и Р в регистры 15 и 18 и сообщает автомату управления (50) о завершении формирования в матричном сумматоре суммы Z,

Формирование кода переноса Р производится логическим блоком 32, который на основе анализа кодов Р , Р , Р , хранимых в регистрах 19, 20, 18, присваивает ему значение в соответствии со следуклцим выражением

Р (р . + P)mod2

Коды Z и Р, поступающие на выхо- ды 43 и 44 матричного сумматора, анализируются органом контроля 28. При этом блок 50 управления формирует сигнал успешного окончания операции на выходе 54 в том случае, ее- ли в блок 50 управления поступает сигнал с выхода 45 и сигнал ошибки b на выходе 49 отсутствует. В противном случае (если на выходе 49 есть сигнал ошибки) блок 50 управления формирует сигнал на выходе 55, что свидетельствует об отказе матричного сумматора и невозможности получения на его выходах неискаженного результата при данном входном наборе. Сиг- нал на Bbixotfie 55 блока 50 управления формируется также в том случае, если орган контроля 14 фиксирует ошибк S-a-0 или S-a-1 q раз, т.е. при на

5

0

5

5

о

Q g g 5

0

личии сигнала W на любом входе группы ВХГ1ДОВ 37.

Таким образом, введенные функциональные элементы и их связи позволяют получить неискаженный код суммы на выходах матричного сумматора при наличии в нем не менее одного отказа. Это обеспечивается за счет изменения на входах 37 управляющего операнда, что равносильно изменению представления операндов X и Y.

Данное изменение представления операндов X и У приводит к задействованию после калсдого подобного изменения других элементов и шин сумматора, а следовательно, к парированию их отказов.

Как показывают результаты анализа данного технического решения, среднее число отказов в данном сумматоре, после которого последний считается неработоспособным, для q 2 равно 5 при потенциально возможном числе отказов в самом сумматоре 33, для q 4 равно 12 при потенциально возможном числе отказов в самом сумматоре 66, для q 6 равно 19 при потенциально возможном числе отказов в самом сумматоре 103, для q 8 равно 26 при потенциально возможном числе отказов в самом сумматоре 144.

Формула изобретения

Матричный сумматор, содержащий восемь коммутаторов, шесть групп элементов ИЛИ, первый орган контроля, блок элементов И, элемент НЕ, четыре элемента И, блок управления, два элемента ИЛИ, группу элементов И, причем тактовый вход блока управления соединен с тактовым входом сумматора, а первый его вьтход соединен с первым входом первого элемента И и входом управлеш1Я первого коммутатора, первый информационный вход сумматора соединен с информационным входом второго коммутатора, вход управления которого соединен с выходом первого элемента ИЛИ, второй информационный вход сумматора соединен с информационным входом третьего коммутатора, вход управления которого соединен с выходом второго элемента ИЛИ, первый и второй входы элементов ИЛИ первой груггпы соединены соответственно с выхода) первого и второго коммутаторо з, первый и второй

914

-inpMOHTon или второй групгты соединены соответственно с выходами третьего и четвертого коммутаторов, выходы элементов ИЛИ первой группы соединены соответственно с первыми входами элементов ИЛИ третьей группы и элементов И группы, выходы элементов IL llI второй группы соединены соответственно с вторыми входами элемен- топ ИЛИ третьей группы и элементов И группы, выходы элементов И группы соединены с первыми входами элементов ИЛИ четвертой группы и первыми пходамт элементов ИЛИ пятой группы, вторые Плоды которых соединены соответственно с вторыми входами элементов ЯЧИ четвертпГ группы и выходом бтгокг; элементов И, вход которого соединен с Bbixo/iahoi элементов ИЛИ третьей группы, выход элемента НЕ соединен с первым входом второго элемента И, выход пятого коммутатора сосд.пнен с первыми входами элементов ИЛ1-1 и естой rpynnf-.i, выходы которой соедипе 111)1 с входами первой группы первого органа контроля и первым выходом результата сумматора, второй результата сумматора соединен с входаш второй группы первого ор- гана контроля, о т л и ч а ю щ и й- с я тем, что, с целью упрощения, сумматор дополнительно содержит два элемента Ш1И, второй о)1ган контроля, inecTi) регистров, логический блок, приче вход управления шестого коммутатора соединен с входами управления первого и седьмого коммутаторов, информадио1П1Ы1 1 вход которого соединен с информационным входом пятого коммутатора и выходом первого регистра, вход начальной установки которого соединен с входами начальной установки второго, третьего, четвертого, пятого, шестого регистров и выходом третьего элемента ИЛИ, первый вход которого соединен с входом начальной установки сумматора, входы разрешения записи первого, втор ого

регистров соединены с выходом четвертого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И и первым информационным входом блока управления, второй информационный вход которого соединен с вторым входом четвертого элемента ИЛИ и выходом второго элемента И, второй вход которого соединен с вторым выходом блока управления, первы

О

5 0 5 0 с 0

0

5

ми входами первог о и второго элементов ИЛИ и входом управления пятого коммутатора, выход элемента НЕ соединен с вторым входом первого элемента И и с первыми входами третьего и четвертого элементов И, второй вход третьего элемента И соединен с третьим выходом блока управления, входом управления восьмого коммутатора и вторым входом второго элемента ИЛИ, четвертый выход блока управления соединен с вторым входом чет-; вертого элемента И, вторым входом первого элемента ИЛИ и входом угфав- ления четвертого коммутатора, третий и четвертый информационные входы блока управления соединены соответственно с выходами третьего и четвертого элементов И, второй вход третьего элемента ИЛИ соединен с входом элемента НЕ и выходом второго органа контроля, входы первой группы которого соединены соответственно с информационными входами первого, третьего, четвертого регистров и выходами элементов ИЛИ четвертой группы, входы второй группы второго органа контроля соединены соответственно с выходами элементов ИЛИ пятой группы, информационными входами второго, пятого и шестого регистров, выход третьего элемента И соединен с входами раэ- решения записи шестого и третьего регистров, выход четвертого элемента И соединен с входами разрешения записи пятого и четвертого регистров, информационные входы четвертого и восьмого коммутаторов соединены с пятым выходом блока управления, пятый информационный вход которого соединен с выходом первого органа контроля, выход второго регистра соединен с вторым выходом результата сумматора, выходы пятого и шестого регистров соединены соответственно с информационными входами первого и шестого коммутаторов, выходы седьмого коммутатора, четвертого и третьего регистров соединены соответственно с первым, вторым, третьим информационными входами логического блока, выходы которого соединены соответственно с вторыми входами элементов ИЛИ шестой группы, выходы которых соединены соответственно с входами первой группы первого органа контроля, выходы восьмого и шестого коммутаторов соединены с третьими входа11142401012

ми элементов ИЛИ соответственно пер- выходами блока управления, входы вой и второй групп, первый и второй сброса и пуска которого соединены выходы управления сумматора соедине- соответственно с входами сброса и ны соответственно с шестым и седьмым пуска сумматора.

Хг

Хз

У1

PZ

Vi

%

2

Iff

U,

Uv Wf

uv Ш

t

t t t t t t t rJ

t t

t t t

фие.г

л

| Матричный сумматор-умножитель | 1978 |

|

SU767759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричный сумматор | 1986 |

|

SU1348824A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-15—Публикация

1986-12-16—Подача