Изобретение относится к вычислительной технике и может быть использовано для синхронизации устройств автоматики и вычислительной техники.

Известно устройство для синхронизации импульсов, содержащее два триггера, пять элементов И и два инвертора.

Недостатком данного устройства является то, что оно не может обеспечить момента выдачи и снятия выходных тактовых импульсов по входному асинхронному сигналу в соответствующие разрешенные интервалы времени, что нередко необходимо в устройствах автоматики и вычислительной техники для фазовой синхронизации устройств, обменивающихся информацией, но работающих с различными частотами тактовых импульсов.

Наиболее близким техническим решением к предлагаемому является фазовый синхронизатор, содержащий задающий генератор, Ьлок из п последовательно соединенных элементов задержки, выполняющий функции формирователя импульсных последовательностей, п элементов И, п триггеров и элемент ИЛИ, причем выход задающего генератора соединен с входом первого элемента задержки, выходы блока элементов задержки с первого по п-и соединены с синхровходом соответствующих триггеров, J-вход n-го триггера соединен с инверсным выходом первого триггера, J-вход 1-го триггера, где о., (n-1)t соединен с инверсным выходом (i+1)- го триггера, К-входы триггеров соединены с шиной нулевого потенциала

Ј

XI

сл ел ю

м

синхронизатор, входы сброса в О триггеров - с входом запуска синх- рониялтора, инверсные выходы триггеров с первого по n-й соединены с первыми входами соответствующих элементов И, прямой выход первого триггера соединен с вторым входом n-го элемента И, прямой выход j-ro триггера, где j 2,,с.,п, соединен с вторым входом (j-l)-ro элемента И, третий вход n-го элемента И соединен с первым выходом блока элементов задержки, третий вход i-ro элемента И соединен с (1+1j-м выходом блока элементов задержки, выходы элементов И соединены с входами элемента ИЛИ, выход которого является выходом синхронизатора.

Зто устройство обеспечивает строго фиксированную величину временного сдвига переднего фронта первого импульса вырабатываемой на выходе последовательности тактовых импульсов относительно переднего фронта запускающего импульса, но также не может обеспечить моменты выдачи и снятия выходных тактовых импульсов по входному асинхронному сигналу в соответствующие разрешенные интервалы времени с

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения синхро- низации входной асинхронной последовательности переменного периода с соответствующими разрешенными интервалами времени.

Поставленная цель достигается тем, что в устройство для синхронизации асинхронных сигналов, содержащее тактовый генератор, распределитель импульсов, n-триггеров (где - число разрядов группы выходов распределителя импульсов), элемент ИЛИ и группу из п элементов И, причем выход тактового генератора соединен с тактовым входом распределителя импульсов, R-входы п триггеров

0

5

первым входом элемента И, второй вход которого соединен с (2п+1)-м выходом распределителя импульсов, выход элемента И является выходом устройства, прямые выходы триггеров соединены с входами элемента ИЛИ, инверсный выход j-ro триггера (j 1,с.п-1) соединен с соответствуюЩим входом каждого элемента И группы, исключая j-й и (j+l)-fi, инверсный выход n-го триггера соединен с последним входом каждого элемента И с второго по (п-1)-й груп5 пы, первый J-вход 1-го триггера соединен с i-выходом первой группы распределителя импульсов, вторые J-входы которых объединены и подключены к входу асинхронной последовательности устройства, третий J-вход n-го триггера соединен с выходом первого элемента И группы, третий J-вход j-ro триггера соединен с выходом (j-fl)-ro элемента И группы, синхровходы триггеров соединены с выходом тактового генератора, первый К-вход 1-го триггера соединен с i-ым выходом второй группы распределителя импульсов, вторые К0 входы триггеров Соединены между

собой и с выходом (п+1)-го триггера, синхровход которого является входом разрешения работы устройства, а вход сброса в нуль соединен с выхо5 дом элемента И-НЕ, входы которого соединены с инверсными выходами п триггеров,

Благодаря введению (п+1)-го триггера, элемента И-НЕ и связи между

0 ними, а также связей между выходами распределителя импульсов и первыми J-K-входами п триггеров, между инверсными1 выходами птриггеров с одной стороны и входами с второго по

5 (п-1)-й группы из пэлементов И и входами,элемента И-НЕ - с доугой, связей между выходами п элементов И и третьими J-входами птриггеров и связи между прямым выходом (п+1)-го

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297051A1 |

| Многоканальное устройство для синхронизации многомашинных комплексов | 1986 |

|

SU1406587A1 |

| Устройство для синхронизации с контролем | 1983 |

|

SU1161933A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для перебора соединений | 1982 |

|

SU1057952A1 |

| Фазовый синхронизатор | 1987 |

|

SU1432751A1 |

| Устройство для синхронизации многоканальной измерительной системы | 1984 |

|

SU1193654A1 |

| Устройство для управления группой из @ объединенных по выходу тиристорных преобразователей | 1986 |

|

SU1394376A1 |

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1684785A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

Изобретение относится к вычислительной технике и может быть использовано для синхронизации устройств автоматики и вычислительной техники. Устройство обеспечивает синхронизацию входной асинхронной последовательности переменного периода с соответствующими разрешенными интервалами времени. Целью изобретения является расширение функциональных возможностей за счет обеспечения синхронизации с переменным периодом. Цель достигается за счет введения триггера, элемента И-НЕ, элемента НЕ 2 ил.

соединены с входом начальной устайов- 50 триггера и вторыми К-входами п тригки распределителя импульсов, который является входом начальной установки устройства, инверсный выход 1-го (триггера (.о.п) соединен с . первым входом 1-го элемента И труп- , пы, введен (п+1)-й триггер, элемент И-НЕ и элемент И, причем выход элемента ИЛИ соединен с входом элемента НЕ, выход которого соединен с

геров обеспечивается расширение функциональных возможностей устройства за счет обеспечения синхронизации входной асинхронной после- довательности переменного периода с соответствующими разрешенными интервалами времени.

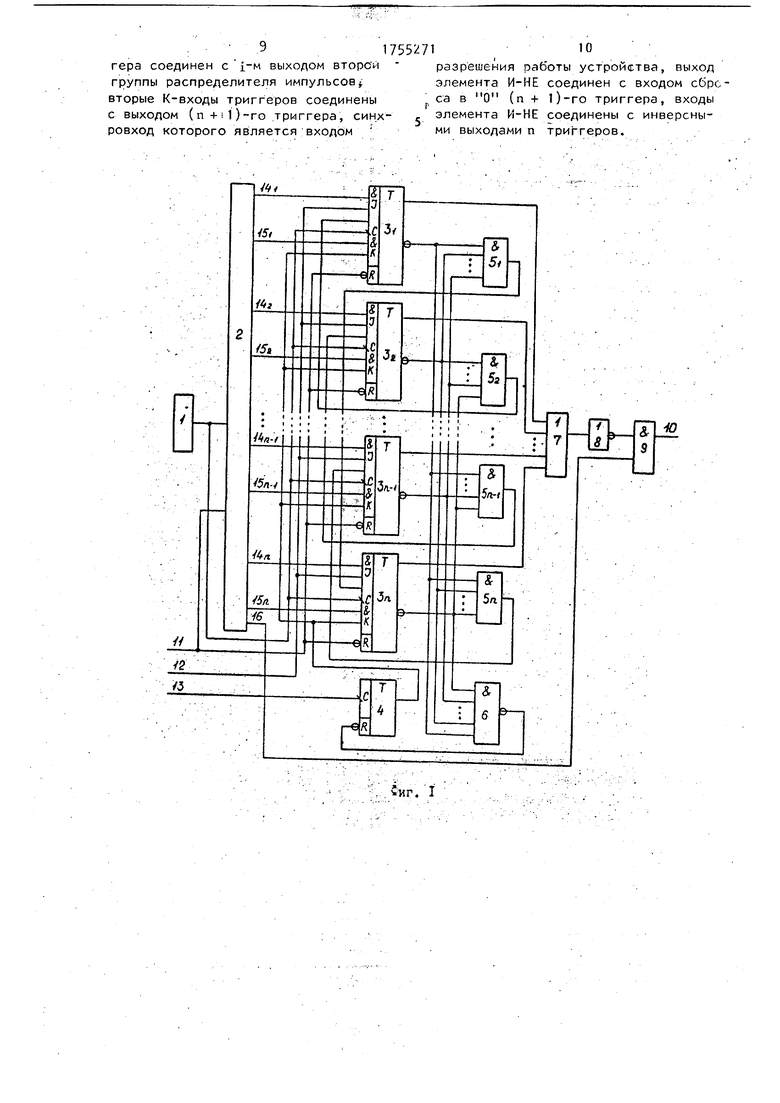

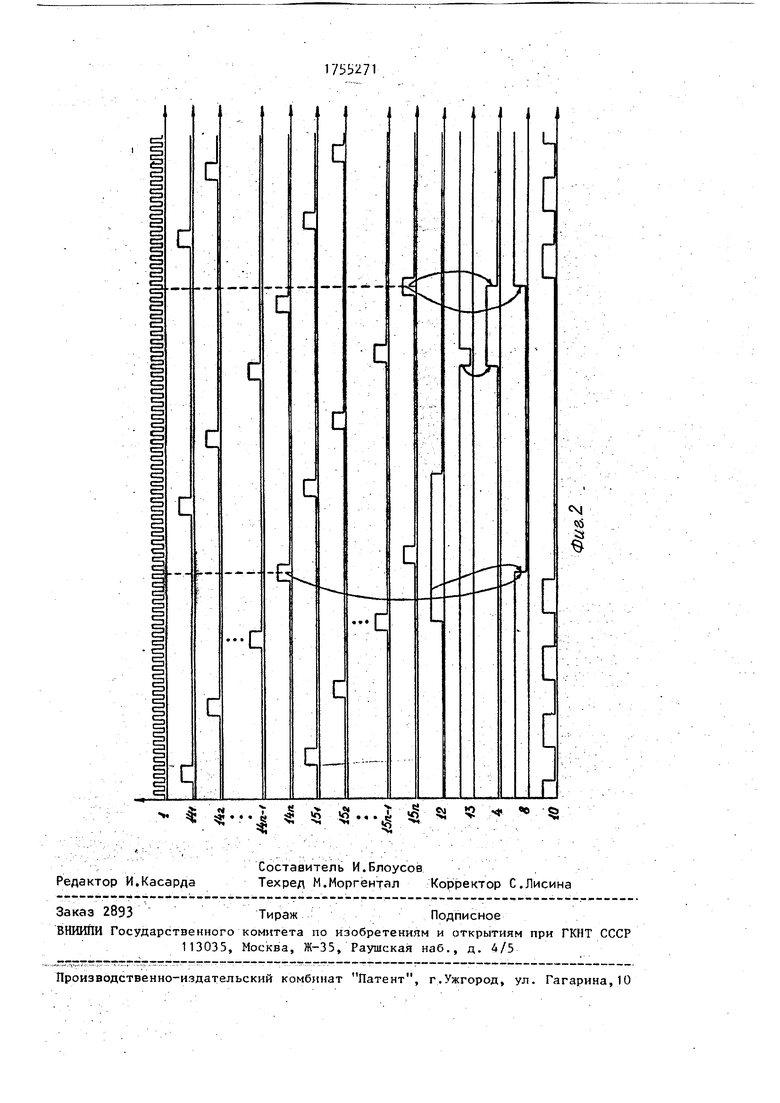

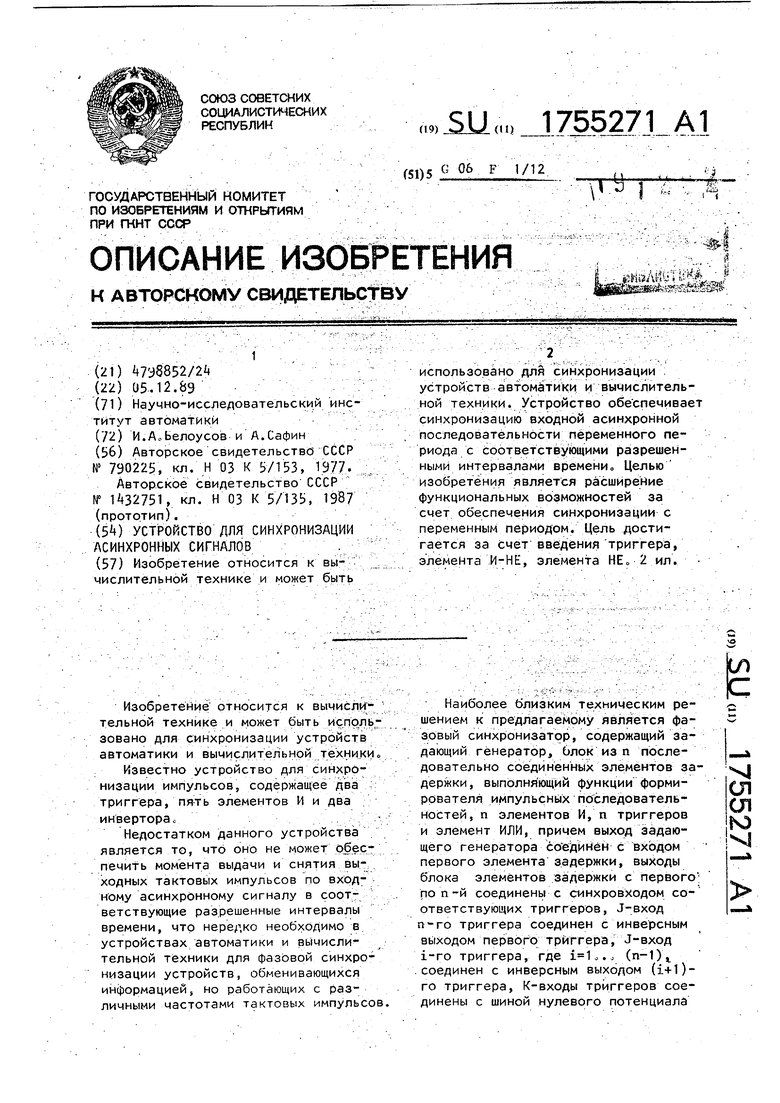

На фиг.1 представлена функциональная схема устройства; на фиг.2

один из вариантов временных диаграмм поясняющих работу.

Устройство для синхронизации асинхронных сигналов содержит тактовый генератор 1, распределитель 2 импульсов, триггеры , (п + 1)-й триггер 4, группу элементов И 5П, элемент И-НЕ 6, элемент ИЛИ 7, элемент НЕ 8, элемент И 9, выход II0 устройства, вход 11 начальной установки устройства, вход 12 асинхронной последовательности устройства, вход 13 разрешения работы устройства, выходы 14 первой группы выходов распределителя 2 импульсов, выходы 15 15п второй группы выходов распределителя 2 импульсов, (2п + 1)-й выход 16 распределителя 2 импульсов.

Выход тактового генератора 1 соединен с синхровходами триггеров 3п и с первым входом распределителя 2 импульсов, второй вход которого соединен R-входами триггеров 3,|- Зп и с входом 11 начальной установки устройства. Выходы 1 первой группы выходов распределителя 3 импульсов соединены соответственно с первыми J-входами триггеров Зц- Зп, выходы 15 п второй группы выходов - с первыми К-входами триггеров 3 Зп Вторые J-BXO- ды триггеров 3,- 3п соединены с входом 12 асинхронной последовательности устройства, а вторые К-входы - с выходом триггера 4„ Третий J-вход триггера 3ц соединен с выходом элемента И 5 третий J-вход триггер 3J (где j 1,..(п - 1)) соединен с выходом элемента И . Инверсные выходы триггеров 3f 3 ц соединены с входами элемента И-НЕ 6„ Кроме того, инверсный выход триггера 3j coe- диЯен с соответствующим входом каждого элемента И 5| - И 5п- исключая элемент И 5j4-i a инверсный выход триггера Зп соединен с последним входом каждого элемента И И 5П. Прямые входы триггеров Зц соединены с входами элемента ИЛИ 7, выход которого соединен через элемент НЕ 8 с первым входом элемента И У, второй вход которого соединен с выходом 16 распределителя 2 импульсов, а выход является выходок 10 устройства, вход 13 разрешения работы которого соединен с синхро- входом триггера , вход cbpoca в

нуль которого соединен с выходо11 элемента И-НЕ Ь.

Устройство работает следующим образом.

На вход 11 начальной установки устройства подается сигнал, obecne- чивающий на выходах распределителя 2 импульсов и на прямых выходах

Q триггеров 3 4 3 у, состояние 0м. Триггер 4 также находится а состоянии

После снятия сигнала начальной установки на входе 11 устройства

5 распределитель 2 вырабатывает последовательности импульсов на выходах Й,|- 1, соответствующих разрешенным интервалам привязки входного асинхронного сигнала (фиг.2, диаграм0 мы ), а на выходах 15«- 15ц - последовательности импульсов, соответствующих разрешенным интервалам привязки входного сигнала разрешения работы устройства (фиг.2,

5 диаграмммы 1ЬП).

До подачи асинхронного сигнала по входу 12 устройства триггеры 3ц - 3 г, и триггер t находятся в cbpo- шенном состоянии, так как на вторые

0 JK-входы триггеров 3 3 ц подается О и поступающие на их синхровходы импульсы с выхода тактового генератора 1 не изменяют их состояния, а на вхол сброса в О триггера h

5 подается О с выхода элемента И-НЕ 6. Гри этом на третьи1 J-входы триггеров Зп подается 1 с выходов элементов И S 5Л, тем самым подготавливая устройство к приему

0 асинхронного сигнала. В это время через открытый элемент И 9 на выход 10 устройства подается последовательность тактовых импульсов с выхода 16 распределителя 2.

5 На вход 12 асинхронной последовательности устройства подается импульс, передний фронт которого приходит в произвольный момент времени (фиг.2, диаграмма 12), однако при0 вязка асинхронного импульса произойдет в ближайшем разрешенном интервале с выхода распределителя 2, так как на все три J-входа триггера 3 в это время подается

5 1 и срабатывает он по заднему фронту (фронту 1/0) синхроимпульса, который расположен внутри разрешенного интервала привязки с выхода распределителя 2. В результате.

1755Z71

чего, с инверсного выхода триггера Зп подается О через элементы И 5-2.v n на третьи входы триггеров 3 Зц- тем самым блокируя срабатывание триггеров 3 1 в слу- чае, если асинхронный импульс по входу 12 устройства будет захватывать два или более разрешенных интервалов привязки (фиг.2, диаграммы 14(, 14Пг 12). При этом с прямого выхода триггера 3 и через элемент ИЛИ 7 подается 1 на вход элемента НЕ 8, О с выхода которого блокирует прохождение тактовых импульсов через элемент И 9 на выход 10 устройства (фиг.2, диаграмма 10).

На вход 13 разрешения работы устройства подается импульс в произвольный момент времени, по переднему фронту которого (фронту 1/0) срабатывает триггер 4 (фиг.2, диаграмма 13). Однако работа устройства начинается в соответствующем разрешенном интервале привязки с выхода 1Ь распределителя 2, следующем после разрешенного интервала привязки с выхода распределителя 2, так как на второй J-вход триггера это время подается О, а на первый и второй К-входы - 1. и триггер 3 сбрасывается по заднему фронту (фронту 1/0) синхроимпульса, который по времени расположен внутри разрешенного интервала с выхода 15 распределителя 2. После чего сбрасывается триггер k сигналом О с выхода элемента Й-НЕ 6, на входы которого в это время подаются Т11 с инверсных выходов триггеров 3 - Зп, и через открытый элемент И 9 на выход 10 устройства подается последовательность тактовых импульсов с выхода 16 распределителя 2.

В качестве тактового генератора 1 может быть использован кварцевый генератор импульсов, собранный по лю бой схеме. В качестве распределителя 2 импульсов может быть применен, например, 2п-разрядный распределитель, выполненный на двоичном счетчике и дешифраторе. Последовательность тактовых импульсов на выходе 46 распределителя 2 может быть полумена произвольной (необходимой в каждом конкретном случае) частоты с помощью дешифратора распределителя 2 импульсов.

8

Таким образом, предлагаемое ( устройство обеспечивает синхрониза- цию входной асинхронной последовательности переменного периода с соответствующими интервалами времени.

5

5

0

0

5

5

Формула изобретения

Устройство для синхронизации асинхронных сигналов, содержащее тактовый генератор, распределитель импульсов, п триггеров (где п - число разрядов группы выходов распределителя импульсов), элемент ИЛИ, группу из п элементов И, причем выход тактового генератора соединен с тактовым входом распределителя импульсов, R--входы п триггеров соединены с входом начальной установки распределителя импульсов, который является входом, начальной установки устройства, инверсный выход Ј-«-го триггера (,...,n) соединен с первым входом i-ro элемента И группы, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения синхронизации с переменным периодом, в него введен (п+1)-й триггер, элемент И-НЕ, и элемент И, причем выход элемента ИЛИ соединен с входом элемента НЕ, выход которого соединен с первым входом элемента И, второй вход которого

5 соединен с (2п+1)-м выходом распределителя импульсов, выход элемента И является выходом устройства, прямые выходы триггеров соединены с входами элемента ИЛИ, инверсный

выход j-ro триггера (,n-l))соединен с соответствующим входом каждого элемента И группы, исключая j-ый, и (j+lj-й инверсный выход п-го триггера соединен с последним входом каждого элемента И группы с второго по (й-1)-й, первый 1-вход 1-го триггера соединен с i-м выходом первой группы распределителя

ф импульсов, вторые I-входы которых объединены и подключены к входу асинхронной последовательности устройства, третий I-вход п-го триггера соединен с выходом первого элемента И группы, третий J-вход j-ro триггера соединен с выходом (j+1)-ro элемента И группы, синхровходы триггеров соединены с выходом тактового генератора, первый К-вход iтго триггера соединен с i-м выходом второй группы распределителя импульсов, вторые «-входы триггеров соединены с выходом (п+ 1)-го триггера, синх- ровход которого является входом

17

-

1755271 ( Ю

разрешения оаботы устройства, выход элемента И-НЕ соединен с входом сброса в О (п + 1)-го триггера, входы элемента И-НЕ соединены с инверсными выходами п триггеров.

& -2J IS

40

Јиг. I

Авторы

Даты

1992-08-15—Публикация

1989-12-05—Подача