4:. СЛ Ю Ч

памяти микропрограмм 2, мультиплексор 3, регистр 4, элемент И 5, коммутатор 6, элемент. ИЛ И 7, приоритетный элемент 8, группу блоков контроля датчиков 9. Счетчик адреса 1 обеспечивает выбор соответствующей микрокоманды из блока постоянной памяти микропрограмм 2 в соответствии с

алгоритмом работы контроллера. Приоритетный элемент 8 обеспечивает выбор адреса перехода к подпрограмме в зависимости от приоритета проверяемого логического условия при одновременном изменении нескольких приоритетных логических условий. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического управления технологическими процессами. Цель изобретения - повышение быстродействия контроллера путем организации прерывания выполнения подпрограммы на любом этапе ее выполнения при изменении значения приоритетного логического устройства. Программируемый контроллер содержит счетчик адреса 1, блок постоянной

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического управления технологическими процессами.

Известно устройство для программного управления циклическими процессами, содержащее генератор импульсов, делитель частоты, первый времязадающий блок, блок набора программ, блок испытаний органов, блок сигнализации, блок обнуления, блок датчиков окончания операций, блок сравнения, счетчик адреса, шифратор, дешифратор, второй и первый RS-триггеры, блок элементов ИЛИ.

Недостатком данного устройства является узкая область применения и низкое быстродействие.

Наиболее близким к предлагаемому является контроллер, содержащий счетчик, блок памяти, мультиплексор, регистр, эле-, мент И, причем первый вход синхронизации контроллера соединен с входом счетчика, выход которого соединен с адресным входом блока памяти, первая группа выходов которого соединена с первым входом элемента И и инверсным V-входом регистра. Вторая группа выходов блока памяти соединена с адресным входом мультиплексора и первой группой D-входов регистра, третья группа выходов блока памяти соединена с второй группой выходов регистра и D-BXOдами счетчика, входы логических условий устройства соединены с D-входами мультиплексора, выход которого соединен со вторым входом элемента И, выход которого соединен с V-входом счетчика, второй вход синхронизации контроллера соединен с Свходом регистра, выход которого является выходом микроопераций контроллера.

Недостатком этого контроллера является низкач область применения, обусловленная невозможностью использования алгоритмов, содержащих приоритетные логические устройства.

Цель изобретения - повышение быстродействия путем организации прерывания выполнения подпрограммы на любом этапе

ее выполнения при изменении значения приоритетного логического условия.

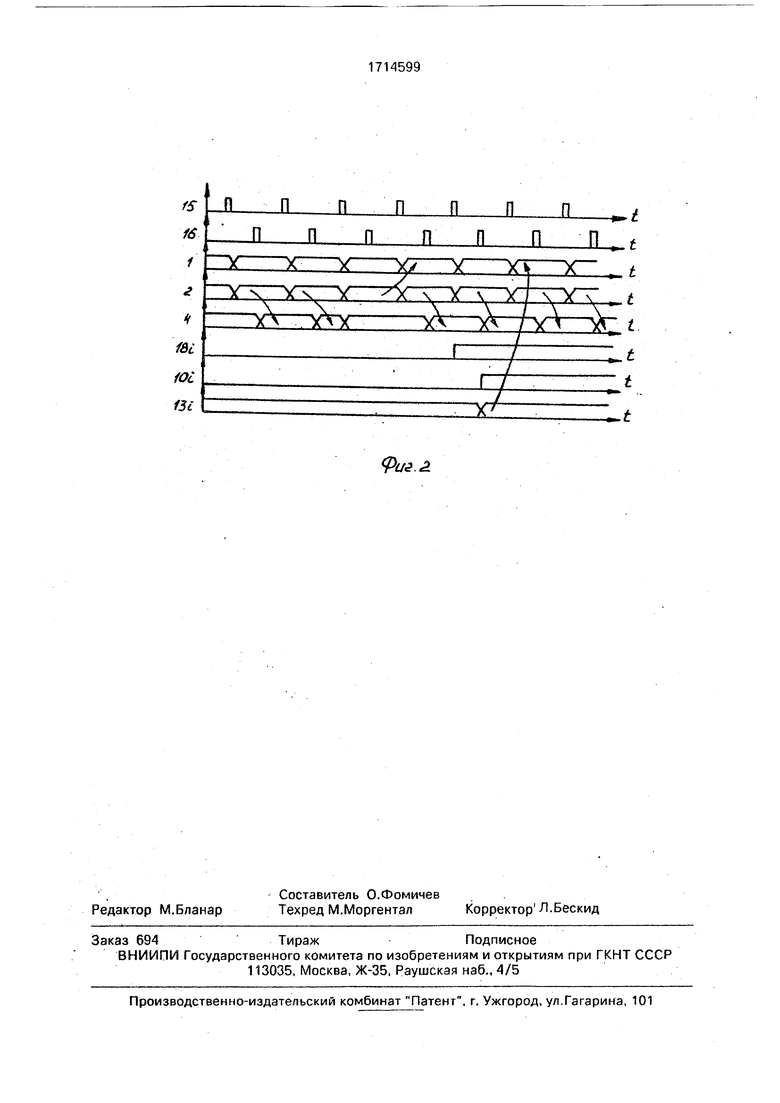

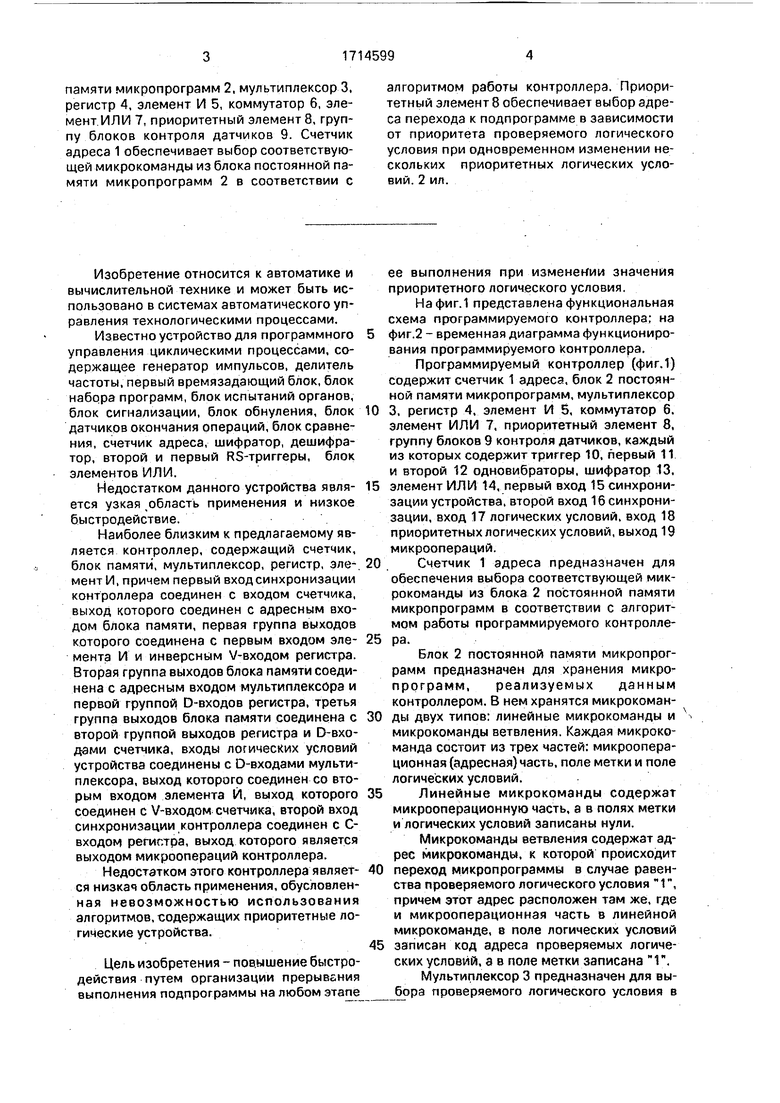

На фиг.1 представлена функциональная схема программируемого контроллера; на

фиг.2 - временная диаграмма функционирования программируемого Контроллера,

Программируемый контроллер (фиг.1) содержит счетчик 1 адреса, блок 2 постоянной памяти микропрограмм, мультиплексор

3, регистр 4, элемент И 5, коммутатор б, элемент ИЛИ 7, приоритетный элемент 8, группу блоков 9 контроля датчиков, каждый иэ которых содержит триггер 10, г ервый 11 и второй 12 одновибраторы, шифратор 13,

элемент ИЛИ 14, первый вход 15 синхронизации устройства, второй вход 16 синхронизации, вход 17 логических условий, вход 18 приоритетных логических условий, выход 19 микроопераций.

. Счетчик 1 адреса предназначен для обеспечения выбора соответствующей микрокоманды из блока 2 постоянной памяти микропрограмм в соответствии с алгоритмом работы программируемого контроллера.

Блок 2 постоянной памяти микропрограмм предназначен для хранения микропрограмм, реализуемых данным контроллером. В нем хранятся микрокоманды двух типов: линейные микрокоманды и микрокоманды ветвления. Каждая микрокоманда состоит из трех частей: микрооперационная (адресная) часть, поле метки и поле логических условий.

Линейные микрокоманды содержат микрооперационную часть, а в полях метки и логических условий записаны нули.

Микрокоманды ветвления содержат адрес микрокоманды, к которой происходит

переход микропрограммы в случае равенства проверяемого логического условия 1, причем этот адрес расположен там же, где и микрооперационная часть в линейной микрокоманде, в поле логических условий

записан код адреса проверяемых логических условий, а в поле метки записана Г. Мультиплексор 3 предназначен для выбора проверяемого логического условия в

зависимости от управляющих сигналов, поступивших на его адресный вход.

Регистр 4 продназначен для временного хранения микрооперационной части считываемой микрокоманды и выдачи ее на выход 19 микроопераций контроллера.

Элемент И 5, коммутатор б, элемент ИЛИ 7 предназначены для управления счетчиком 1 адреса.

Приоритетный элемент 8 предназначен для организации выбора адреса перехода к подпрограмме в зависимости от приоритет;а проверяемого приоритетного логического условия при одновременном изменении нескольких приоритетных логических уелоВИЙ..

Блок 9 контроля датчиков 9 (i 1, п) предназначен для формирования адреса перехода к соответствующей части подпрограммы .при изменении 1-го приоритетного логического условия, а также для формирования сигнала, управляющего счетчиком 1 адреса.

Программируемый контроллер работает следующим образом.

В исходном состоянии триггеры 10 всех блоков контроля датчиков, счетчик 1 адреса, регистр 4 находятся в нулевом состояний. Все приоритетные логические условия равнынулю.

Таким образом, на адресном входе блока 2 постоянной памяти микропрограмм находится адрес, содержащий только нули, считываются данные из ячейки блока 2 постоянной памяти микропрограмм с нулевым адресом.

По заднему фронту первого тактового импульса, поступающего на первый вход 15 синхронизации устройства, соединенный с С-входом счетчика 1 адреса, последний переходит в очередное состояние, происходит обращение к очередной (первой) ячейке блока 2 постоянной памяти микропрограмм, в которой записан начальный адрес микрокоманды. По заднему фронту первого тактового импульса, поступающему на второй вход 16 синхронизации контроллера, микрооперационная часть данной микрокоманды записывается в регистр 4, поступая на выход 19 микроопераций контроллера (фиг.2). По второму тактовому импульсу, поступающему на первый вход 15 синхронизации контроллера, счетчик 1 адреса переходит в очередное состояние, обращаясь к следующей ячейке блока 2 постоянной памяти микропрограмм. По второму тактовому импульсу, поступающему на второй вход 16 синхронизации контроллера, микрооперационная часть очередной микрокоманды записывается в регистр 4 и поступает на выход 19 микроопераций контроллера. Далее контроллер работает аналогичным образом до тех пор, пока не считана микрокоманда ветвления, в поле метки которой записана единица, в отличие от линейной микрокоманды, в поле метки которой записан ноль.

Как только на выходе блока 2 постоянной памяти микропрограмм появляется микрокоманда ветвления, единица из ее поля метки обнуляет регистр 4 (фиг.2) и поступает на второй вход элемента И 5 и (n-f 1)-й вход коммутатора 6. В поле микроопераций микрокоманд ветвления записан адрес микрокоманды перехода, к которой происходит переход к микропрограмме в случае выполнения проверяемых логических условий, код адреса которых записан в поле логических условий данной микрокоманды ветвления. Мультиплексор 3 коммутирует проверяемое логическое условие, поступающее на его Dl-вход с входов 17 логических и входов 18 приоритетных логических условий контроллера. Если проверяемое логическое условие равно 1, то элемент И 5 открывается и единица с его выхода через элемент ИЛИ 7 поступает на V-вход счетчика 1 адреса, переводя его в режим записи.

По очередному тактовому импульсу, поступающему на первый вход 15 синхронизации контроллера (фиг.2), адрес очередной микрокомандь, к которой происходит переход, проходя через (п+1) вход коммутатора 6, записывается е счетчик 1 адреса. Далее контроллер работает аналогично.

В случае, когда проверяемое логическое условие равно нулю, а элемент И 5 закрыт и счетчик 1 адреса по очередному таковому импульсу,поступающему с первого входа 15 синхронизации контроллера, переходит в очередное состояние.

В случае изменения i-ro приоритетного логического условия (1 ТТп) контроллер работает следующим образом.

По очередному тактовому импульсу, поступающему с второго входа 16 синхронизации контроллера после изменения 1-го приоритетного логического условия (фиг.2), 10 i-ro блока 9 контроля датчиков (i 1, п) переходит в единичное состояние, на его прямом выходе появляется единица. В результате на выходе первого одновибратора 11 i-ro блока контроля датчиков (1 1, п) появляется единичный импульс, длительность которого удовлетворяет условию

п Тимп 4 П,

-.

где п - период следования импульсов синхронизации контроллера.

Этот импульс, пройдя через элемент ЛИ 141-го блока 9 контроля датчиков (I ТГп). оступает на 1-й вход приоритетного элеента 8, на 1-й вход элемента ИЛУ1 7. На 1-м ходе приоритетного элемента 8 появляется диничный потенциал ткрывающий 1-й вход коммутатора 6 (I 1, п). на D-вход счетика 1 поступает адрес микрокоманды, к которой должен осуществиться переход икропрограммы при переходе в единицу i-ro приоритетного логического условия. Этот адрес поступает с выхода шифратора 13 1-го блока 9 контроля датчиков (I 1, п). анный шифратор 13 вырабатывает два адреса в зависимости от состояния 1-го приоритетного логического условия (1 1, п).

Единичный импульс, проходя через элемент ИЛИ 7 на V-вход счетчика 1 адреса, переводит последний в режим записи, и по очередному тактовому импульсу, поступающему на первый вход 15 синхронизации контроллера, адрес с выхода шифpaтo|эaJЗ 1-го блока 9 контроля датчиков , п), пройдя через кс)ммутатор 6, записывается в счетчик 1. Таким образом, происходит переход к соответствующей части микрокоманды, записанной в блоке 2 постоянной памяти микропрограмм,

В случае, когда по одному тактовому импульсу, поступающему с второго входа 16 синхронизации контроллера, происходит изменение состояния триггера 10 более чем в одном блоке 9 контроля датчиков, контроллер работает следующим образом.

Допустим, произошло изменение состояния триггера 10 в I и j блоках 9 контроля датчиков (Г 1....,п), О 1,...,п), причем i j. Тогда одновременно единичный импульс появится на выходе, элемента ИЛИ 14 1-го и j-ro блоков контроля датчиков. Эти импульсы поступают на 1-й и J-й входы приоритетного элемента 8. Но из его п выходов единичный импульс появляется только на Нм выходе.

Таким образом, открыт только 1-й Dвход коммутатора 6, смещения адресов не происходит.

Далее контроллер работает аналогично.

Формула изобретения

Программируемый контроллер, содержащий счетчик адреса, блок постоянной памяти микропрограмм, мультиплексор, регистр и элемент И, причем синхровход счетчика адреса является первым входом синхронизации контроллера, а выходы счетчика адреса соединены с адресными входами блока постоянной памяти микропрограмм, микрооперационные выходы блока постоянной памяти микропрограмм - с информационными входами регистра, выходы которого являются выходами микроопераций контроллера, выход метки блока постоянной памяти микропрограмм соединен с входом сброса регистра и первым входом элемента И, выходы логических условий блока постоянной памяти микропрограмм

соединены с адресными входами мультиплексора, выход которого соединен с вторым входом элемента И, первая группа информационных входов мультиплексора является группой входов логических услоВИЙ контроллера, синхровход регистра соединен с вторым входом синхронизации контроллера, отличающийся тем, что, с целью повышения быстродействия контроллера, в него введены коммутатор, элемент ИЛИ, приоритетный элемент и группа блоков контроля датчиков, каждый из которых содержит триггер, первый и второй одновибраторы, шифратор и элемент ИЛИ, причем микрооперационные выходы и выход метки блока постоянной памяти микропрограмм соединены соответственно с информационными входами и входом разрешения коммутатора, выходы которого соединены с информационными входами

счетчика адреса, группа входов приоритетных логических условий контроллера соединена с второй группой входов мультиплексора, а i-й разряд группы входов приоритетных логических условий контроллера соединен с информационным входом триггера i-ro (1 TTri) блока контроля датчиков группы, прямой и инверсный выходы которого соединены с соответствующими входами шифратора и соответственно с входами первого

и второго одновибраторов, выходы которых соединены с соответствующими входами элемента ИЛИ 1-го блока контроля датчиков группы, выход элемента ИЛИ i-ro блока контроля датчиков группы соединен с 1-м (i 1,

п) входом элемента ИЛИ и приоритетного элемента, выходы которого соединены соответственно с группой входов разрешения коммутатора, выход элемента И соединен с (ri+1)-M входом элемента ИЛИ, выход которого соединен с входом разрешения счетчика адреса, входы синхронизации триггеров блоков контроля датчиков группы объединены и соединены с вторым входом синхронизации контроллера, группа выходов

шифратора i-ro блока контроля датчиков группы соединена с группой информационных входов коммутатора.

Pu.

| Устройство для программного управления и контроля циклическими процессами | 1985 |

|

SU1310776A1 |

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| и др | |||

| Основы построения микроконтроллеров АСКУ, МО СССР, 1989.. | |||

Авторы

Даты

1992-02-23—Публикация

1990-05-03—Подача