II

о ел ос

I1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU940148A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для синхронизации вычислительной системы | 1987 |

|

SU1495773A1 |

| Устройство для контроля времени выполнения программы | 1983 |

|

SU1140124A1 |

| Устройство для синхронизации с контролем | 1983 |

|

SU1161933A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для контроля распределителя | 1980 |

|

SU942026A1 |

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1684785A1 |

| Устройство для контроля распределителя | 1983 |

|

SU1128260A2 |

Изобретение относится к цифровой вьтислительной технике и автоматике и может быть использовано при создании цифровых вычислительных комплексов повышенной надежности. Отличительной особенностью устройства является то, что оно позволяет совмещать по фазе и частоте одноименные импульсы генераторов и распределителей нескольких ЦВМ вычислитель - ного комплекса, распознавать расфазиг ровки и рассинхронизации неисправных генераторов и распределителей и путем своевременного исключения их влияния на работу исправных генераторов и распределителей других ЦВМ и обеспечивать их синхронную и синфазную работу. Целью изобретения является повышение надежности за сч ет исключения неисправных генераторов при расфазировке. Поставленная цель достигается за счет введения в каждый канал переключателя 5, элементов ИЛИ 6, 7, блока 10 управления, элементов 11 и 29 задержки,- элементов И 14, 16, 17,22, триггера 21,| блока 19, контроля синхронизации, блока 18 контроля распределителя импульсов. 2 з.п. ф-лы, 4 ил. S (Л с

. Фог.1 .

Изобретение относится к цифровой вычислительной технике и автоматике и может быть использовано при создании цифровых вычислительных комплексов (ЦБК) повышенной надежности, i Целью изобретения является повы- шение надежности путем исключения i неисправных генераторов при расфа- (зировке..

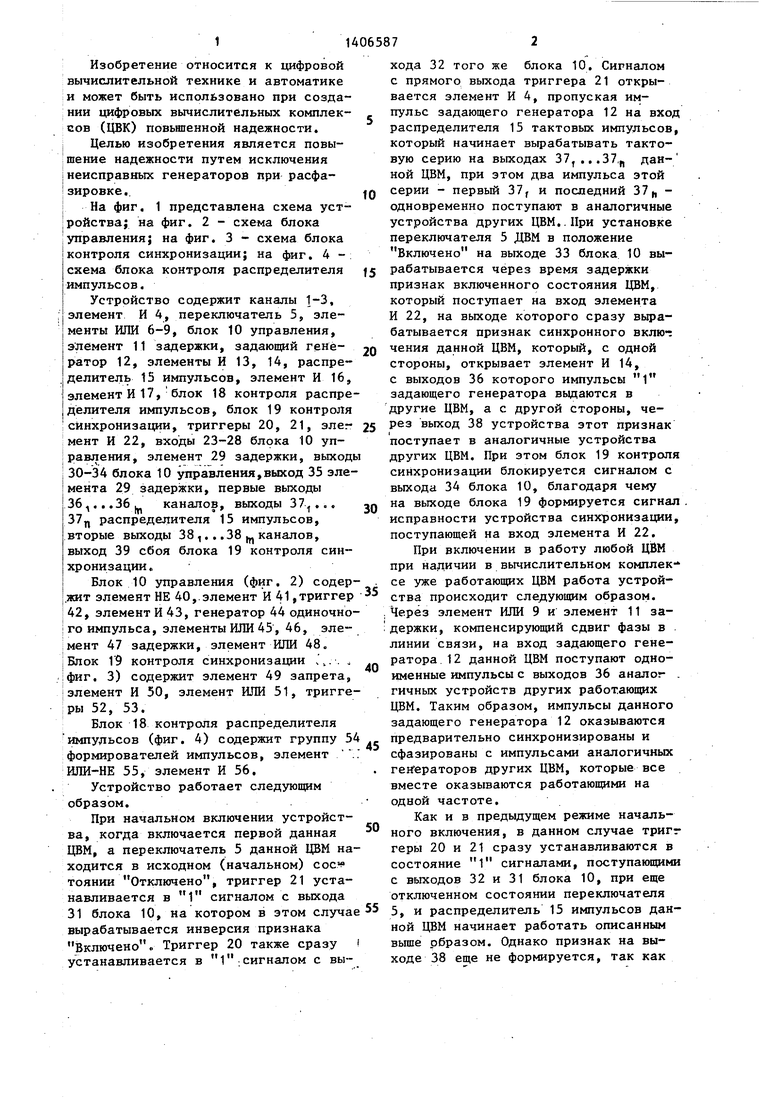

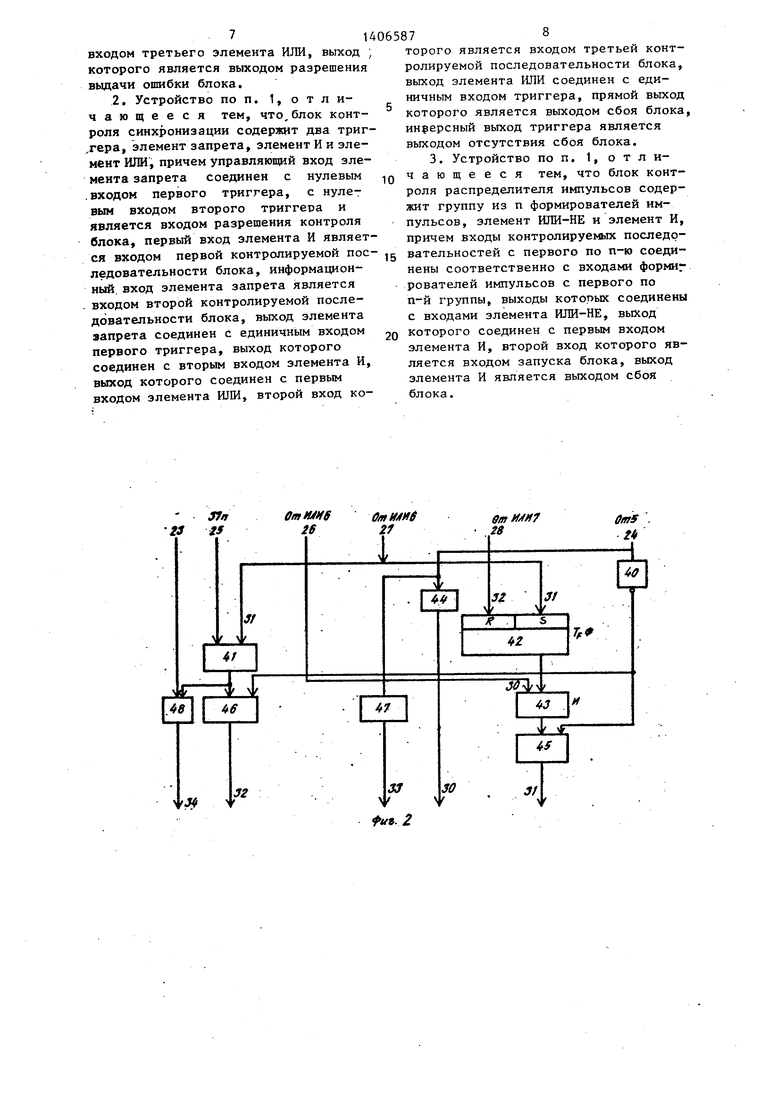

I На фиг. 1 представлена схема уст- |ройства; на фиг. 2 - схема блока {управления; на фиг. 3 - схема блока контроля синхронизации; на фиг. 4 - схема блока контроля распределителя импульсов,

Устройство содержит каналы 1-3, элемент И 4, переключатель 5, зле- I менты ИЛИ 6-9, блок 10 управления, I элемент 11 задержки, задающий гене- Iратор 12, элементы И 13, 14, распределитель 15 импульсов, элемент И 16, элемент И 17, блок 18 контроля распределителя импульсов, блок 19 контроля синхронизации, триггеры 20, 21, элег :мент И 22, входы 23-28 блока 10 уп- Еравления, элемент 29 задержки, выходы i 30-34 блока 10 управления, выход 35 эле- iмента 29 задержки, первые выходы 36д...36. каналов, выходы 37,... 37д распределителя 15 импульсов, вторые выходы 38 ,...38 каналов, выход 39 сбоя блока 19 контроля синхронизации.

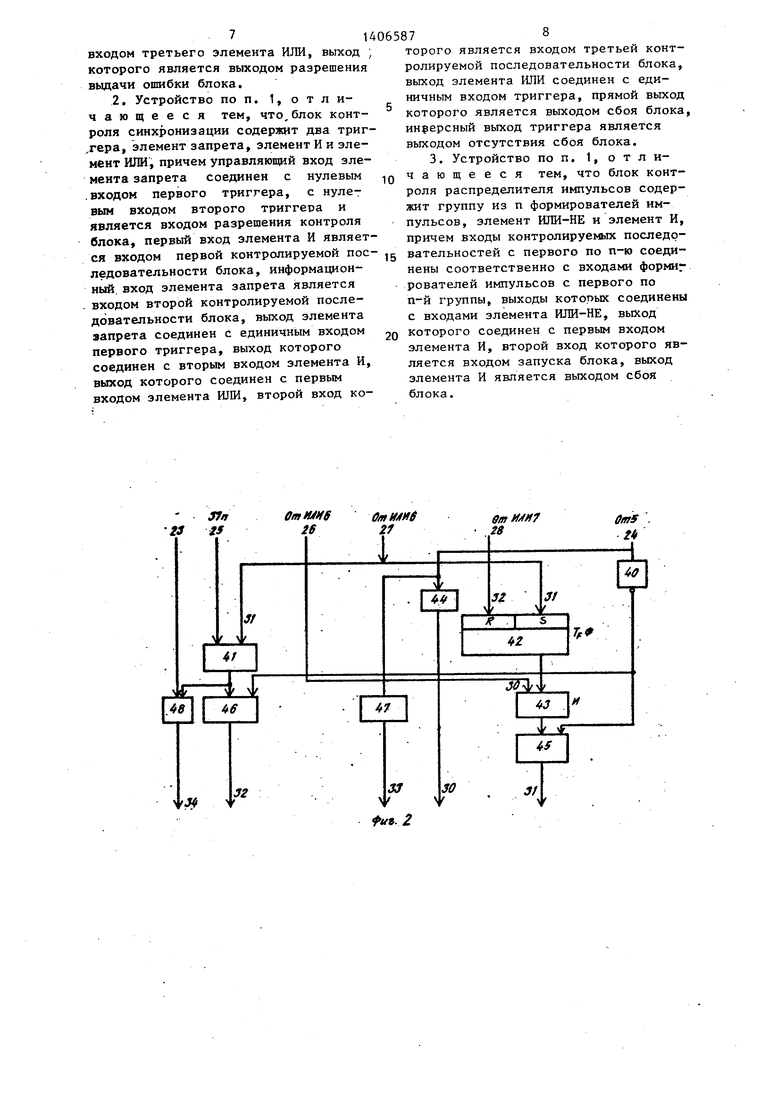

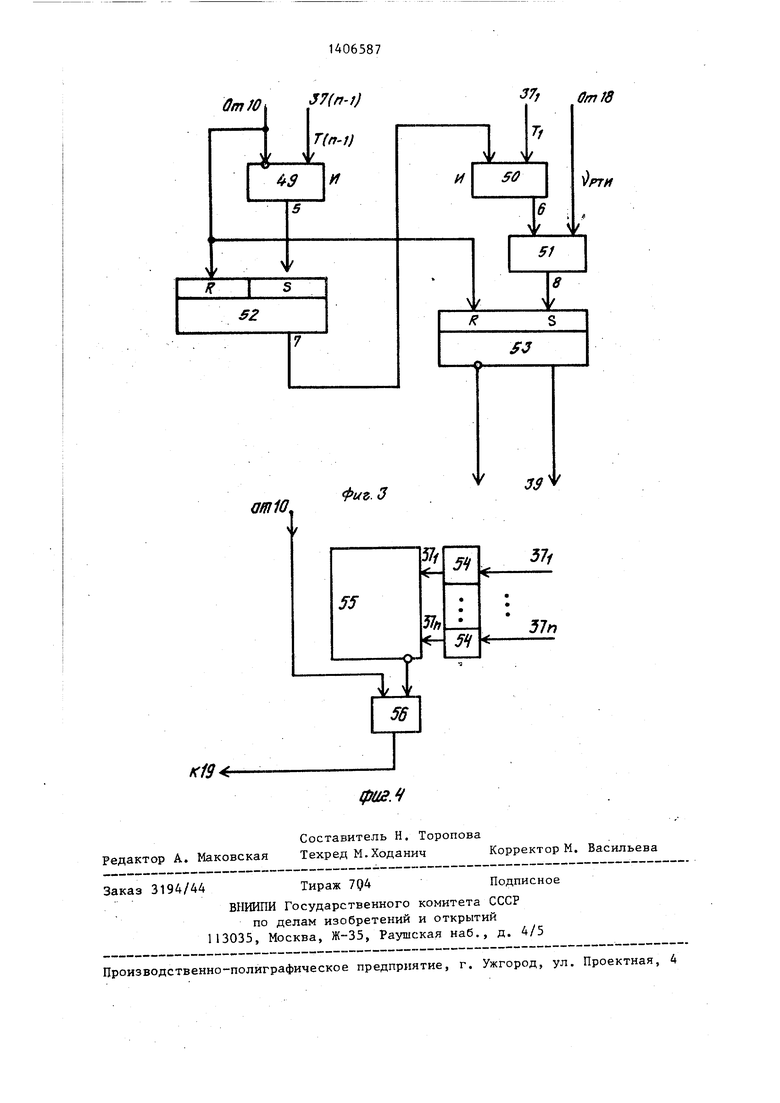

Блок 10 управления (фиг. 2) содер- .жит элемент НЕ 40,.элемент И 41,триггер 42, элемент И 43, генератор 44 одиночного импульса, элементы ИЛИ 45, 46, элемент 47 задержки, элемент ИЛИ 48, Блок Г9 контроля синхронизации .. . фиг. 3) содержит элемент 49 запрета, :элемент И 50, элемент ИЛИ 51, тригге- |ры 52, 53.

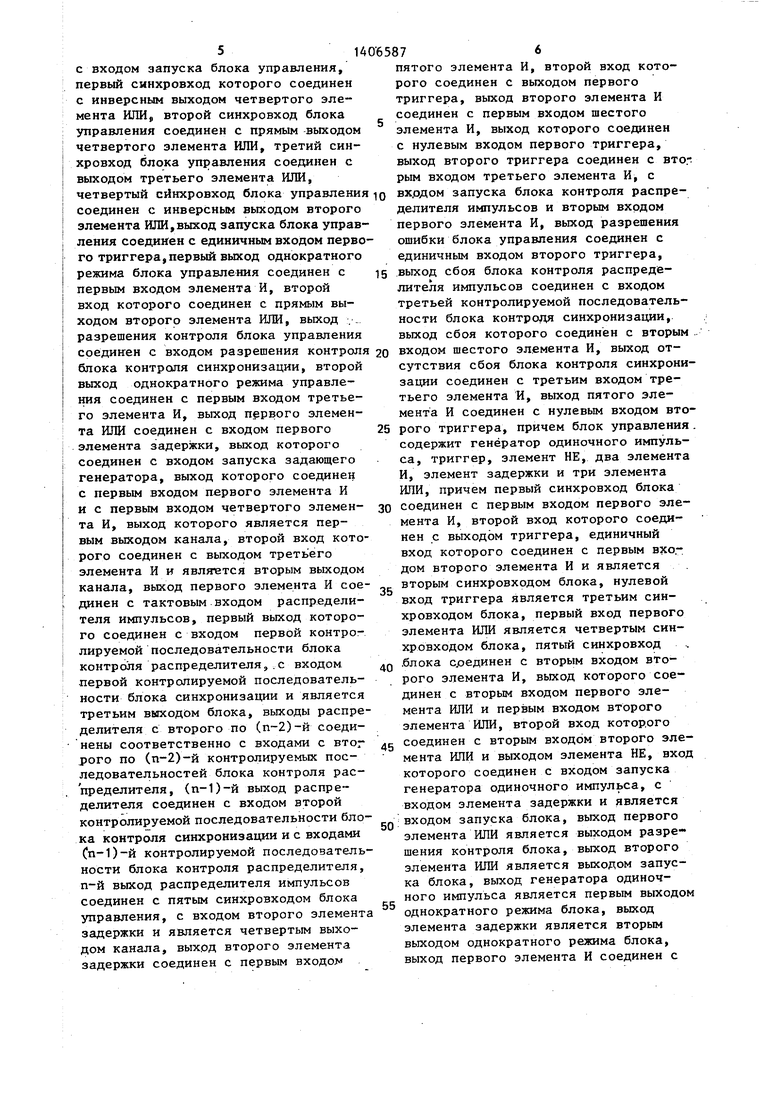

Блок 18 контроля распределителя импульсов (фиг. 4) содержит группу 54 формирователей импульсов, элемент . ШШ-НЕ 55, элемент И 56.

Устройство работает следующим образом.

При начальном включении устройства, когда включается первой данная ЦВМ, а переключатель 5 данной ЦВМ находится в исходном (начальном) сое тоянии Отключено, триггер 21 устанавливается в 1 сигналом с выхода 31 блока 10, на котором в этом случае вырабатывается инверсия признака Включено., Триггер 20 также сразу устанавливается в 1 ;сигналом с вы0

5

0

5

0

5

0

5

0

5

хода 32 того же блока 10. Сигналом с прямого выхода триггера 21 открывается элемент И 4, пропуская импульс задающего генератора 12 на вход распределителя 15 тактовых импульсов, который начинает вьфабатывать тактовую серию на выходах 37, ...37, дан- ной ЦВМ, при этом два импульса этой серии - первый 37, и последний одновременно поступают в аналогичные устройства других ЦВМ..Цри установке переключателя 5 ДВМ в положение Включено на выходе 33 блока 10 вырабатывается через время задержки признак включенного состояния ЦВМ, который поступает на вход элемента И 22, на выходе которого сразу вырабатывается признак синхронного вклюп чения данной ЦВМ, который, с одной стороны, открывает элемент И 14, с выходов 36 которого импульсы 1 задающего генератора выдаются в другие ЦВМ, а с другой стороны, через выход 38 устройства этот признак поступает в аналогичные устройства других ЦВМ. При этом блок 19 контроля синхронизации блокируется сигналом с выхода 34 блока 10, благодаря чему на выходе блока 19 формируется сигнал исправности устройства синхронизации, поступающей на вход элемента И 22.

При включении в работу любой ЦВМ при надичии в вычислительном комплек- се уже работающих ЦВМ работа устройства происходит следующим образом. , Через элемент ИЛИ 9 и элемент 11 за- держки, компенсирующий сдвиг фазы в линии связи, на вход задающего генератора 12 данной ЦВМ поступают одноименные импульсы с выходов 36 аналог . гичных устройств других работающих ЦВМ. Таким образом, импульсы данного задающего генератора 12 оказываются предварительно синхронизированы и сфазированы с импульсами аналогичных ген ераторов других ЦВМ, которые все вместе оказываются работающими на одной частоте.

Как и в предьщущем режиме начального включения, в данном случае тригг геры 20 и 21 сразу устанавливаются в состояние 1 сигналами, поступающими с выходов 32 и 31 блока 10, при еще отключенном состоянии переключателя 5, и распределитель 15 импульсов данной ЦВМ начинает работать описанным вьше образом. Однако признак на выходе 38 еще не формируется, так как

10

15

20

отсутствует сигнал с выхода 3.3 блока 10. При включении переключателя 5 в режим Включено и появлении сигнала на выходе 30 блока 10 формируется импульсный сигнал, и при наличии хотя бы одного из признаков 38 ...38 на входе элемента ИЛИ 8 на его выходе формируется сигнал, . после чего элемент И 13 вырабатывает сигнал на своем выходе, который через элемент ИЛИ 16 сбрасывает в О триггер 20, после чего последним тактовым импульсом, задержанным в блоке 10 и вьщаваемым с его выхода 35, сбрасывается в О и триггер 21 сигналом, поступающим с выхода эле- мента И 17. В результате этого закрывается элемент И 4, распределитель 15 рриостанавливается, причем фиксируется его начальное состояние за счет выбора момента времени приоста- нова. С приходом синхроимпульса на выходе 31 блока 10 формируется сигнал, по времени совпадающий с пау 25 ЗОЙ между последним и первым тактовыми импульсами тактовой серии других ЦВМ, и триггер 21 устанавливается в состояние 1, вследствие чего вновь открывается элемент И 4, и распределитель 15 импульсов данной включаемой ЦВМ начинает работать с исходного положения, выдавая тактовую сеию на выходах 37...37„ синхронно синфазно с распределителями 15 ругих ЦВМ вычислительного комплекса.35 К этому моменту времени формируется признак на выходе 33 блока 10 и, если факт синхронности и синфазности подтверждается блоком 19 путем вьщачи на его выходе сигнала исправности, то на выходе 38 элемента И 22 формиуется признак синхронизации, который, как уже указывалось, с одной стороны, оступает на выход 38 устройства и алее в аналогичные устройства других4 ЦВМ, а с другой стороны, открывает элемент И 14, обеспечивая тем самым выдачу импульсов задающего генератоа 12 через выход 36 устройства в ругие ЦВМ.50

При первом же совпадении фаз тактовых серий данного распределителя с аспределителем других ЦВМ триггер 20 устанавливается в 1 сигналом с выода 33 блока 10,тем самым блокируется 55 абота элемента И 17,и как следствие этого, сброс триггера 21 в нулевое состояние. В случае нарушения синфазности и

30

1406587

0

5

0

5 5 0

50

синхронности, работы данного распределителя 15 или задающего генератора 12 с работой одноименных распределителей и генераторов других ЦВМ вычислительного комплекса блок 19 контроля на своем выходе сбоя формирует сигнал неисправности, который через элемент ИЛИ 16 сбрасывает в О триггер 20 и затем последним тактовьгм импульсом, задержанным на время задержки элементом 29 задержки, сбрасывает в О триггер 21.

В результате этого распределитель 15 импульсов останавливается в наг ., чальном исходном состоянии, прекращается вьщача в другие ЦВМ импульсов с генератора 12 и распределителя 15, а также формирование и вьщача сигнала с выхода элемента И 22 признака синхронизации. Таким образом, полностью исключается влияние неисправности генератора и рапределителя тактовой серии на работу одноименных устройств в других ЦВМ ЦВК.

Формула изобретения

с входом запуска блока управления, первый синхровход которого соединен с инверсным выходом четвертого элемента ИЛИ, второй синхровход блока управлени5Г соединен с прямым выходом четвертого элемента ИЛИ, третий синхровход блока управления соединен с выходом третьего элемента ИЛИ,

четвертый синхровход блока управления ю вхрдом запуска блока контроля распресоединен с инверсным выходом второго элемента ИЛИ,выход запуска блока управления соединен с единичным входом первого триггера,первый выход однократного режима блока управления соединен с первым входом элемента И, второй вход которого соединен с прямым выходом второго элемента ИЛИ, выход разрешения контроля блока управления

соединен с входом разрешения контроля 20 входом шестого элемента И, выход отблока контроля синхронизации, второй выход однократного режима управления соединен с первым входом третьего элемента И, выход первого элемента ИЛИ соединен с входом первого элемента задержки, выход которого соединен с входом запуска задающего генератора, выход которого соединен с первым входом первого элемента И и с первым входом четвертого элемента И, выход которого является первым выходом канала, второй вход которого соединен с выходом третьего элемента И и являтется вторым выходом канала, выход первого элемента И соединен с тактовым входом распределителя импульсов, первый выход которого соединен с входом первой контролируемой последовательности блока контроля распределителя,.с входом первой контролируемой последовательности блока синхронизации и является третьим выходом блока, выходы распределителя с второго по ()-й соединены соответственно с входами с втог рого по (п-2)-й контролируемых последовательностей блока контроля распределителя, (п-1)-й выход распределителя соединен с входом второй контролируемой последовательности блока контроля синхронизации и с входами Сп-1)-й контролируемой последовательности блока контроля распределителя, п-й выход распределителя импульсов соединен с пятым синхровходом блока управления, с входом второго элемента задержки и является четвертым выходом канала, выход второго элемента задержки соединен с первым входо

25

30

35

сутствия сбоя блока контроля синхрони зации соединен с третьим входом третьего элемента И, выход пятого элемента И соединен с нулевым входом вто рого триггера, причем блок управления содержит генератор одиночного импульса, триггер, элемент НЕ, два элемента И, элемент задержки и три элемента ИЛИ, причем первый синхровход блока соединен с первым входом первого элемента И, второй вход которого соединен с выходом триггера, единичный вход которого соединен с первым входом второго элемента И и является вторым синхровходом блока, нулевой вход триггера является третьим синхровходом блока, первый вход первого элемента ИЛИ является четвертым синхровходом блока, пятый синхровход Q .блока с/зединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента ИЛИ и выходом элемента НЕ, вход которого соединен с входом запуска генератора одиночного импульса, с входом элемента задержки и является входом запуска блока, выход первого элемента ИЛИ является выходом разрешения контроля блока, выход второго элемента ИЛИ является выходом запуска блока, выход генератора одиночного импульса является первым выходом однократного режима блока, выход элемента задержки является вторым выходом однократного режима блока, выход первого элемента И соединен с

45

50

55

пятого элемента И, второй вход кото рого соединен с выходом первого триггера, выход второго элемента И соединен с первым входом шестого элемента И, выход которого соединен с нулевым входом первого триггера, выход второго триггера соединен с втог рым входом третьего элемента И, с

делителя импульсов и вторым вхрдом первого элемента И, выход разрешения ошибки блока управления соединен с единичным входом второго триггера, выход сбоя блока контроля распределителя импульсов соединен с входом третьей контролируемой последовательности блока контродя синхронизации, выход сбоя которого соединен с вторым

5

0

5

сутствия сбоя блока контроля синхронизации соединен с третьим входом третьего элемента И, выход пятого элемента И соединен с нулевым входом второго триггера, причем блок управления . содержит генератор одиночного импульса, триггер, элемент НЕ, два элемента И, элемент задержки и три элемента ИЛИ, причем первый синхровход блока соединен с первым входом первого элемента И, второй вход которого соединен с выходом триггера, единичный вход которого соединен с первым входом второго элемента И и является вторым синхровходом блока, нулевой вход триггера является третьим синхровходом блока, первый вход первого элемента ИЛИ является четвертым синхровходом блока, пятый синхровход Q .блока с/зединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента ИЛИ и выходом элемента НЕ, вход которого соединен с входом запуска генератора одиночного импульса, с входом элемента задержки и является входом запуска блока, выход первого элемента ИЛИ является выходом разрешения контроля блока, выход второго элемента ИЛИ является выходом запуска блока, выход генератора одиночного импульса является первым выходом однократного режима блока, выход элемента задержки является вторым выходом однократного режима блока, выход первого элемента И соединен с

5

0

5

входом третьего элемента ИЛИ, выход ; которого является выходом разрешения вьздачи ошибки блока.

торого является входом третьей контролируемой последовательности блока, выход элемента ИЛИ соединен с еди- ничньш входом триггера, прямой выход которого является выходом сбоя блока инрерсный выход триггера является выходом отсутствия сбоя блока.

нены соответственно с входами формиг рователей импульсов с первого по п-й группы, выходы которых соединены с входами элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И, второй вход которого является входом запуска блока, выход элемента И является выходом сбоя блока.

УУ 23 25

OmtUHS 26

торого является входом третьей контролируемой последовательности блока, выход элемента ИЛИ соединен с еди- ничньш входом триггера, прямой выход которого является выходом сбоя блока, инрерсный выход триггера является выходом отсутствия сбоя блока.

нены соответственно с входами формиг рователей импульсов с первого по п-й группы, выходы которых соединены с входами элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И, второй вход которого является входом запуска блока, выход элемента И является выходом сбоя блока.

вт 28

OittS

ut.2

отЮ,

фиг. J

55

к 19

37f

0f7J/8

37/

5

571

57/,

5Н

57п

фиа.

| Патент США № 3932847, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Многоканальное устройство для синхронизации многомашинных комплексов | 1979 |

|

SU783779A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-30—Публикация

1986-04-29—Подача