Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах функционирующих в СОК, схемах контроля по модулю.

Известен сумматор по модулю, содержащий первый и второй узлы формирования обратного кода, блок суммирования, элемент И, формирователь импульсов, триггер, группу элементов И.

Недостатком известного устройства является большое количество оборудования. Наиболее близким к предлагаемому по технической сущности является одноразрядный сумматор комбинационного типа с переменным основанием п, содержащий 2 группы по п одноразрядных сумматоров, две группы элементов И, группу элементов ИЛИ, инвертор и элемент ИЛИ, информационными входами операндов являются входы верхнего ряда одноразрядных сумматоров, выходы которых соединены с входами нижней линейки одноразрядных сумматоров, на другой вход которого подается переполнение (16-п) и со вторыми входами первой группы элементов И, переносы в старший разряд старших разрядов обоих рядов сумматоров являются входами элемента ИЛИ, выход которого через инвертор соединен с первыми входами первой группы элементов И и первыми входами второй группы элементов И, выходы первой и второй групп элементов И являются входами элементов ИЛИ, выход элементов ИЛИ являются выходом устройства.

Недостатком известного устройства является большое количество оборудования. Целью изобретения является снижение аппаратурных затрат,

Цель достигается тем, что в известном устройстве, содержащем две группы одноразрядных двоичных сумматоров, группу элементов И и эпемент ИЛИ, причем, первые и вторые информационные входы одноразрядных датчиков сумматоров первой группы соединены со входами соответствующих разрядных значений соответственно первого и второго операндов устройства, вход переноса каждого одноразрядного двоичного сумматора первой группы кроме первого, сое, нен с выходом переноса предыдущего поразрядного двоичного сумматора той же группы, выходы суммы одноразрядных двоичных сумматоров первой группы соединены с первыми информа- ционными входами соответствующих одноразрядных двоичных сумматоров второй группы, выходы суммы которых соединены с выходами результата сумматора, вход переноса каждого одноразрядного

двоичного сумматора второй группы, кроме первого соединен с выходом переноса предыдущего одноразрядного сумматора той же группы, выходы переноса последних

одноразрядных двоичных сумматоров первой и второй групп соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первыми входами элементов И группы, введены новые

связи, вторые входы элементов И группы соединены со входами соответствующих разрядных значений модуля сумматора, а выходы - со вторыми информационными входами соответствующих одноразрядных

двоичных сумматоров второй группы, третий вход элемента ИЛИ соединен со входом запуска сумматора.

Элемент ИЛИ устройства выполнен трехвходовым.

В основу работы предлагаемого устройства положено следующее:

Si «|4-$|Д ,

0)

где Si - сумма, а и /3 - операнды, /}- модуль (основание).

Возьмем модуль М 2П (где п - количество разрядов, необходимых для представ- ления max {/}}, такой что М р, , тогда выражение (1) можно представить в виде

Г , +

Si ai+fi+ept I Ј,

(2)

35 где p. М -pi -код переполнения модуля р , до модуля М, а

40

С,

0. if GS +/9i pi 1 , faj+/ i p,

45

«i +p М , если oi +Д pi a +fi +pt М , если o /oi.

Таким образом, выражение (2) позволяет реализовать на двоичном п-разрядном сумматоре сумматор по переменному модулю.

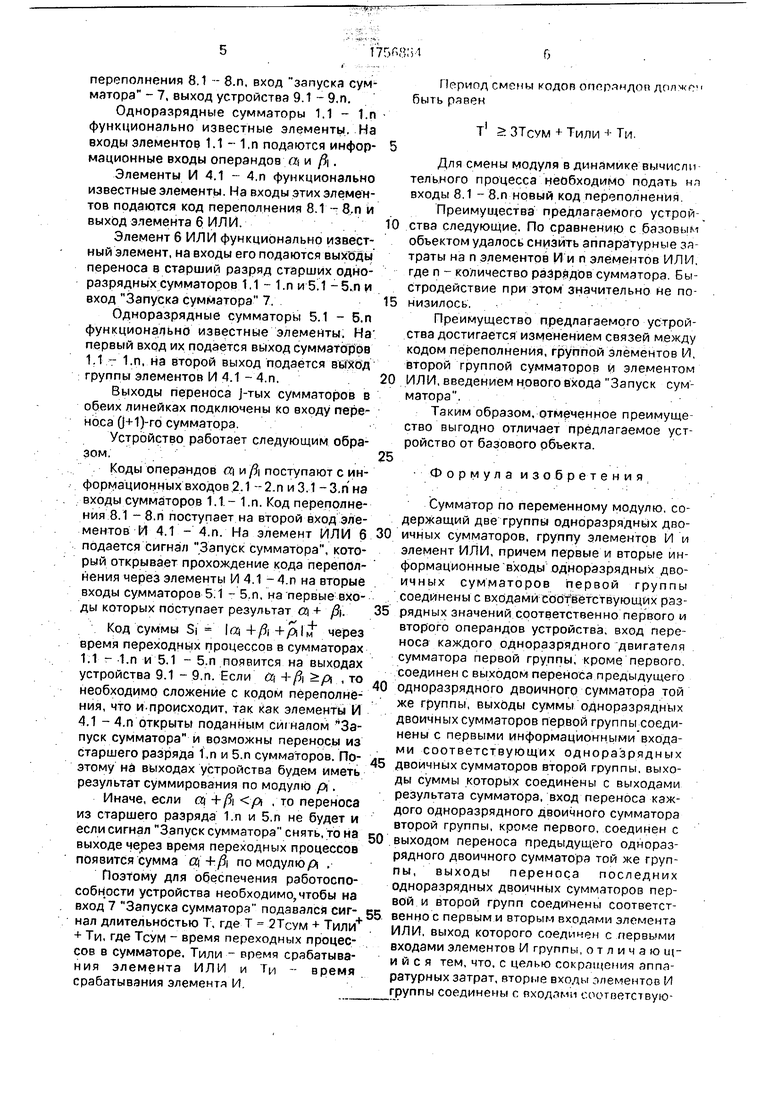

На чертеже пр/ едена функциональная схема сумматора по переменному модулю. Сумматор по переменному модулю содержит первую группу из п-одноразрядных сумматоров 1.1 - 1.п, вторую группу из п

одноразрядных сумматоров 5.1 - 5,п, группу элементов И 4.1 - 4.п, элемент 6 ИЛИ, информационные входы операндов а и fi 2.1 - 2.п и3.1 -З.п, информационный вход кода

переполнения 8.1 - 8.п, вход запуска сумматора - 7. выход устройства 9.1 - 9,п.

Одноразрядные сумматоры 1.1 - 1.п функционально известные элементы. На входы элементов 1.1 - 1.п подаются информационные входы операндов а и fi.

Элементы И 4.1 - 4,п функционально известные элементы. На входы этих элементов подаются код переполнения 8.1 - 8.п и выход элемента б ИЛИ.

Элемент 6 ИЛИ функционально известный элемент, на входы его подаются выходы переноса в старший разряд старших одноразрядных сумматоров 1,1 - 1 .п и 5.1 - 5.п и вход Запуска сумматора 7.

Одноразрядные сумматоры 5.1 - б.п функционально известные элементы. На первый вход их подается выход сумматоров 1.1 - 1.п. на второй выход подается выход группы элементов И 4.1 - 4.п.

Выходы переноса J-тых сумматоров в обеих линейках подключены ко входу переноса (|+1)-го сумматора

Устройство работает следующим образом.

Коды операндов а поступают с информационных входов 2.1 - 2.п и 3.1 - З.п на входы сумматоров 1.1 - 1.п. Код переполнения 8.1 - 8.п поступает на второй вход элементов И 4.1 - 4.п. На элемент ИЛИ б подается сигнал Запуск сумматора, который открывает прохождение кода переполнения через элементы И 4.1 - 4.п на вторые входы сумматоров 5.1 - 5.п, на первые входы которых поступает результат а + р.

Код суммы Si , +р|1м через время переходных процессов в сумматорах 1.1 - 1.п и 5.1 - б.п появится на выходах устройства 9.1 - 9.п. Если Сх Л-{$ р , то необходимо сложение с кодом переполнения, что и-происходит, так как элементы И 4.1 - 4.п открыты поданным си налом Запуск сумматора и возможны переносы из старшего разряда 1,п и б.п сумматоров. Поэтому на выходах устройства будем иметь результат суммирования по модулю р .

Иначе, если сц p , то переноса из старшего разряда 1.п и 5,п не будет и если сигнал Запуск сумматора снять, то на выходе через время переходных процессов появится сумма по модулю/и .

Поэтому для обеспечения работоспособности устройства необходимо, чтобы на вход 7 Запуска сумматора подавался сиг- нал длительностью Т, где Т 2Тсум + Тили+ + Гц, где ТСУМ - время переходных процессов в сумматоре. Тили - время срабатывания элемента ИЛИ и Ги - время срабатывания элемента И

15

0

5

10

5

0

5

0

5

0

Период смсчш кодов опсряндоп быть рявен

Т1 ЗТсУМ + Тили н Ти

Для смены модуля в динамике вычисли тельного процесса необходимо подать нл входы 8.1 - 8.п новый код переполнения

Преимущества предлагаемого устрой ства следующие. По сравнению с базовым объектом удалось снизить аппаратурные зя траты на п элементов И и п элементов ИЛИ. где п - количество разрядов сумматора Быстродействие при этом значительно не понизилось.

Преимущество предлагаемого устройства достигается изменением связей между кодом переполнения, группой элементов И, второй группой сумматоров и элементом ИЛИ, введением нового входа Запуск сумматора.

Таким образом, отмеченное преимуще ство выгодно отличает предлагаемое устройство от базового объекта.

Формула изобретения

Сумматор по переменному модулю, содержащий две группы одноразрядных двоичных сумматоров, группу элементов И и элемент ИЛИ, причем первые и вторые информационные входы одноразрядных двоичных сумматоров первой группы соединены с входами соответствующих разрядных значений соответственно первого и второго операндов устройства, вход переноса каждого одноразрядного двигателя сумматора первой группы, кроме первого соединен с выходом переноса предыдущего одноразрядного двоичного сумматора той же группы, выходы суммы одноразрядных двоичных сумматоров первой группы соединены с первыми информационными входами соответствующих одноразрядных двоичных сумматоров второй группы, выходы суммы которых соединены с выходами результата сумматора, вход переноса каждого одноразрядного двоичного сумматора второй группы, кроме первого, соединен с выходом переноса предыдущего одноразрядного двоичного сумматора той же груп- пы, выходы переноса последних одноразрядных двоичных сумматоров первой и второй групп соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первыми входами элементов И группы, отличаю щ- и и с я тем, что, с целью сокращения аппаратурных затрат, вторые входы элементов И группы соединены с входлми соотгзетствую

щих разрядных значений модуля суммато- одноразрядных двоичных сумматоров втора, а выходы - с вторыми информационны- рой группы, третий вход элемента ИЛИ сое- ми входами соответствующих динен с входом запуска сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1501047A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для умножения | 1982 |

|

SU1156064A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Устройство для сложения по модулю | 1982 |

|

SU1064278A1 |

| Устройство для умножения | 1987 |

|

SU1501045A1 |

| СУММАТОР КОДОВ "1 ИЗ N" | 1997 |

|

RU2129730C1 |

Изобретение относится к вычислитель ной технике и может бьГть использовано в специализированных вычислительных устройствах, функционирующих в СОК, схемах контроля по модулю, Цель изобретения - снижение аппаратурных затрат. Сумматор содержит две группы одноразрядных сумматоров 1, 5, группу элементов И 4, элемент ИЛИ 6, два входных операнда 2, 3, вход модуля 8, вход запуска 7 и выход 9. 1 ил

| Сумматор по модулю | 1982 |

|

SU1134939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| Приспособление к индикатору для определения момента вспышки в двигателях | 1925 |

|

SU1969A1 |

| рис | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-08-23—Публикация

1990-11-26—Подача