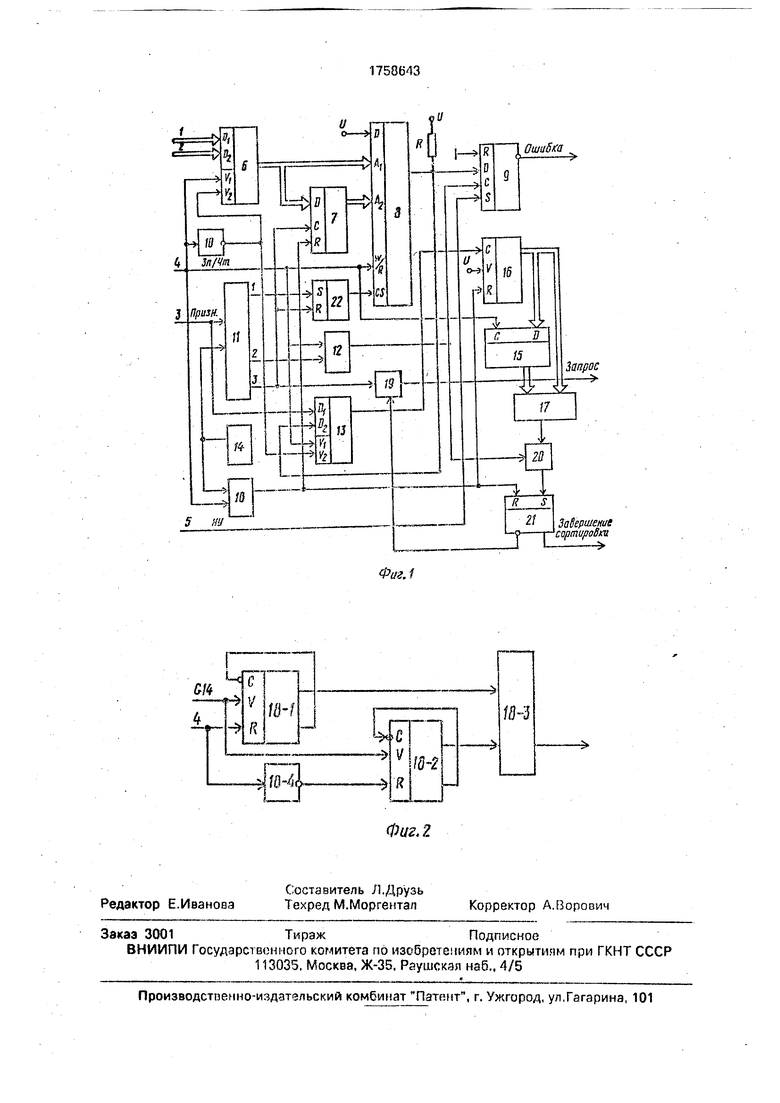

18-2, элементы ИЛИ 18-3, НЕ 18-4. Блок 8 памяти содержит П одноразрядных ячеек по числу П сравниваемых байтов а кодовых последовательностях.

Устройство работает следующим обра- зом. Для сортировки заданных упорядоченных последовательностей кодов в устройстве обеспечивается режим записи эталонной последовательности и режим сравнения сортируемой и эталонной после- довательности кодов. Режим записи эталонной последовательности задается по входу 4 потенциальным сигналом низкого уровня. Этот сигнал непосредственно и через элемент НЕ 10 управляет коммутаторами б, 13 и подключает входы 1 через коммутатор 6 к адресным входам блока 8 памяти и к регистру 7, вход 3 через коммутатор 13 - к входу счетчика 16, закрывает элемент И 12, устанавливает по входу W/R в блоке 8 памяти режим записи, управляет формирователем 18 импульсов, который устанавливает в нуль регистр 7, счетчик 16 и триггер 21. Триггер 21 открывает элемент И 19. Сигнал начальной установки по входу 5 включает триггер 9, При этом снимается сигнал ошибки с его инверсного выхода. После этого на входы 1 поступают параллельные коды эталонной последовательности. Каждый байт последовательности сопровождается признаком информации в виде единичного сигнала, поступающего на вход 3 устройства. Первый байт через коммутатор 6 подается на первые адресные входы блока 8 памяти и на входы блока 8 памяти и на входы реги- стра 7,

Признак информации по входу 3 включает распределитель 11 и через коммутатор 13 подается на тактовый вход счетчика 16, который считает число байтов в последова- тельности. Распределитель 11 в одном цикле формирует три импульсных сигнала. Сигнал с первого выхода распределителя 11 включает триггер 22, сигнал с выхода которого поступает на вход выборки 8 памяти. Адрес ячейки блока 8 памяти задается кодом текущего байта и кодом предыдущего байта последовательности, который хранится в регистре 7. Для первого байта последовательности код в регистре 7 - нулевой. В ячейку с указанным адресом первый импульс распределителя записывает сигнал лог. 1,т.к. на D-вход блока 8 памяти постоянно подан сигнал лог.Г. Сигнал со второго выхода распределителя 11 не воздействует на триггер 9, т.к. элемент И 12 закрыт сигналом низкого уровня с входа 4 устройства. Сигнал с третьего выхода распределителя 11 отключает триггер 22, подается на тактовый вход регистра 7. фиксирует

в нем код текущего байта последовательности и через элемент И 19 выдает сигнал запроса следующего второго байта эталонной последовательности. Для второго байта адрес ячейки блока 8 памяти, в которую записывается сигнал лог.1, содержит код второго байта с выходов коммутатора 6 и код первого байта с выхода регистра 7 и т.д. Таким образом, после прохождения всех байтов эталонной последовательности о одноразрядных ячейках блока 8, адресуемых предыдущим и последующим байтами, записаны сигналы лог. 1. в остальных ячейках - лог.О. Число байтов эталонной последовательности подсчитывается счетчиком 16. Признаком окончания эталонной последовательности является выставление по входу 4 потенциального сигнала высокого уровня. Этот сигнал устанавливает на входе W/R блока 8 памяти режим считывания, открывает элемент И 12, подключает через коммутатор 6 входы 2 устройства к регистру 7 и адресным входам блока 8 памяти, через коммутатор 13 - выход блока 8 памяти к входу счетчика 16, включает формирователь 18 импульсов. Кроме того, по фронту сигнала с входа 4 в регистр 15 переписывается число байтов эталонной последовательности с выходов счетчика 16. Импульс формирователя 18 отключает триггер 21, устанавливает в нуль регистр 7, счетчик 16. Устройство подготавливается для приема сортируемой последовательности кодов, которая подается по входем 2 устройства. Каждый байт сортируемой последовательности сопровождается также сигналом-признаком, который по входу 3 включает распределитель 11. В режиме сравнения в случае правильности сортируемой последовательности первый импульс распределителя 11 считывает из ячеек блока 8 памяти, адресуемых кодами текущих и предыдущих байтов последовательности, сигналы лог.Г, который подаются на D- вход триггера 9, и через элемент И 20 опрашивает выход блока 17 сравнения. Третий импульс распределителя 11 обеспечивает, как и в режиме записи эталонной последовательности, фиксирование кода предыдущего байга сортируемой последовательности в регистре 7, сброс в нуль триггера 22 и запрос информации через элемент И 19. Счет- чик 16 подсчитывает число байт сортируемой последовательности, которое сравнивается с числом в регистре 15 с помощью блока 17 сравнения. При совпадении указанных чисел блок 17 выдает сигнал, открывающий элемент И 20. В текущем цикле обработки последнего байта последовательности второй импульс распределителя

11 через элементы И 12, И 20 включаеттриг- гер 21. Триггер 21 выдает сигнал завершения сортировки и блокирует через элемент И 19 сигнал запроса информации.

В случае искажения байтов или нарушения их очередности в сортируемой последовательности коды на адресных входах блока 8 памяти адресуют одноразрядные ячейки, в которых записан сигнал лог.О. При этом второй импульс распределителя 11 через элемент И 12 устанавливает в нуль триггер 9, с инверсного выхода которого выдается сигнал ошибки.

В предложенном устройстве обеспечивается сравнение байтов сортируемой последовательности с эталонной последовательностью без записи и хранения этих кодов в блоке памяти, что позволяет сократить объем памяти и сортировать коды по принадлежности их данному массиву и по очередности их поступления в массиве.

Формула изобретения

Устройство для сравнения кодов, содержащее генератор импульсов, счетчик, блок памяти, первый и второй коммутаторы, элемент НЕ, отличающееся тем, что, с целью расширения области применения за счет выделения заданной последовательности кодов, в него ведены первый и второй регистры, распределитель импульсов, первый, второй и третий триггеры, формирователь импульсов, первый, второй и третий элементы И, блок сравнения, причем информационные входы эталонных и сортируемых чисел устройства соединены соответственно с информационными входами первой и второй групп первого коммутатора, выходы которого соединены с информационными входами первого регистра и адресными входами первой группы блока памяти, адресные входы второй группы которого подключены к выходам первого регистра, вход установки в О которого объединен с входами установки в О счетчика, первого триггера и выходом формирователя импульсов, тактовый вход которого объединен с выходом генератора импульсов и тактовым входом распределителя, управляющий вход которого соединен

с входом признака информации устройства и первым информационным входом второго коммутатора, второй информационный вход которого соединен с информационным входом второго триггера и выходом блока памяти, информационный вход которого подключен к шине логической единицы устройства, вход установки режима запись-чтение соединен с входом установки режимов

устройства, с тактовым входом второго регистра, с первым входом первого элемента И. с управляющим входом формирователя импульсов, с первыми управляющими входами первого и второго коммутаторов и через элемент Н Е - с вторыми управляющими входами первого и второго коммутаторов, выход второго коммутатора соединен с тактовым входом счетчика, выходы которого соединены с информационными входами

второго регистра и второй группы входов блока сравнения, первая группа входов которого соединена с выходами второго регистра, выход блока сравнения соединен с первым входом второго элемента И, второй

вход которого соединен с синхровходом второго триггера и выходом первого элемента И, второй вход которого соединен с вторым выходом распределителя, первый выход которого соединен с входом установки в единичное состояние третьего триггера, выход которого подключен к входу выборки кристалла блока памяти, вход установки в О третьего триггера соединен с тактовым входом первого регистра, третьим

выходом распределителя и первым входом третьего элемента И, второй вход которого соединен с инверсным выходом первого триггера, вход установки в единичное состояние которого соединен с выходом второго

элемента И, инверсный выход второго и прямой выход первого триггеров являются соответственно выходами сигнала ошибки и завершения сортировки устройства, выход третьего элемента И - выходом запроса информации устройства, вход начальной установки устройства соединен с входом установки в единичное состояние второго триггера, вход установки в О которого подключен к шине логического нуля устройства.

Завершение coptnupoBni -

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для вывода информации | 1989 |

|

SU1732349A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для считывания и отображения графической информации | 1986 |

|

SU1506459A1 |

| Устройство для контроля объектов | 1985 |

|

SU1363141A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

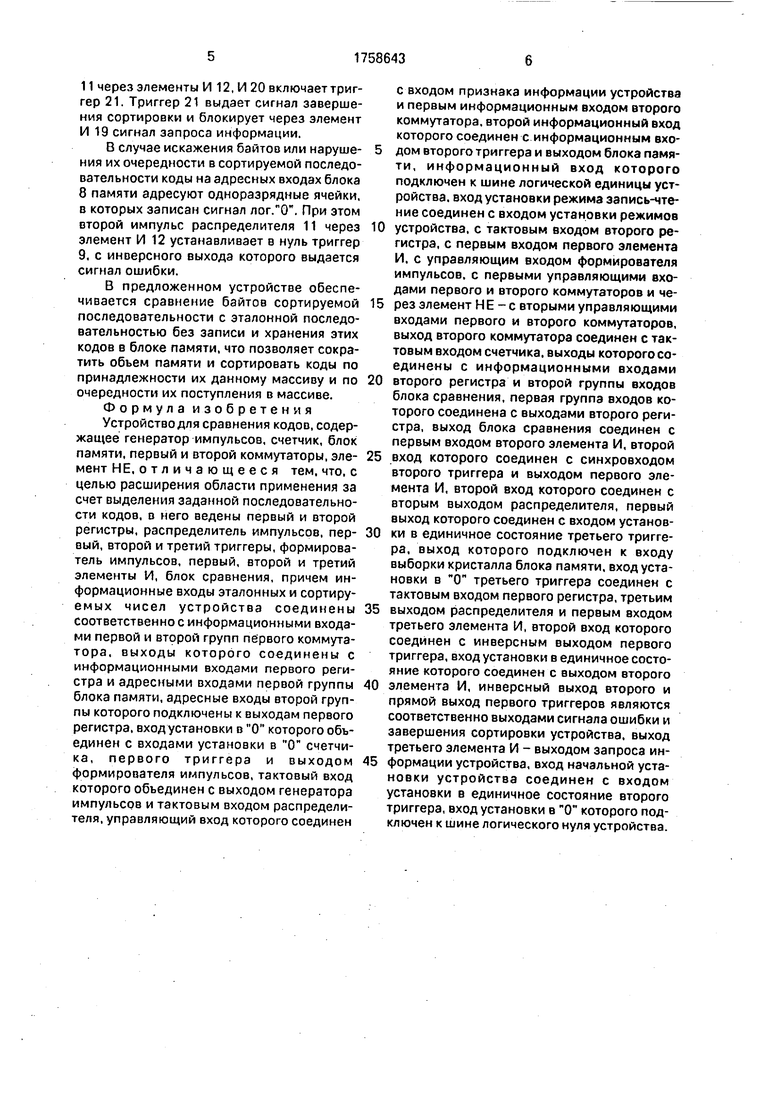

Изобретение относится ; области вычислительной техники и может Сып. использовано о системах обработки информации. Цель изобретения - расширение области применения за счет выделения заданной последовательности кодои. Устройство содержит коммутатор, регистры, блок памяти, триггеры, элемент НС, распределитель им- пульсов, коммутатор, генератор импульсов, сметчик, блок сравнения, формирователь импульсов, элементы И. В устройстве реализуется режим записи эталонной последовательности кодов и режим сравнения Изобретение относится к области вычислительной техники и 6мть использовано в системах обработки информации. Цель изобретения - расширение области применения устройства зз счет выделз- нил заданной последовательности кодов. Функциональная схема устройства приведена кз чертеже иг. 1, пример выполнения формирователя импульсов - на фиг.2. Устройство содержит сходы 1 эталонной информационной последовательности, входы рабочей последовательности с эталонной. Коды эталонной последовательности и рабочей последовательности подаются на входы. Импульсы сопровождения включают распределитель, который формируют импульс выборки блока памяти, импульс записи в триггер ошибки и импульс запроса информации. Коды эталонной последовательности формируют адреса ячеек блока памяти, в которые записываются сигналы лог.Т . Число входов в последовательности подсчитывается счетчиком и фиксируется в регистре. При сравнении кодов рабочей последовательности из блока 8 считываются сигналы лог, 1, которые удерживают триггер сшибки в единичном состоянии, и сигнал ошибки не формируется. При нарушении последовательности кодов или сбоях из ячеек блока памяти считывается сигнал лог.О, триггер ошибки устанавливаются в нуль и выдается сигнал ошибки. Состояния регистра и счетчика сравниваются блоком сравнения, который включает триггер, и выдается сигнал окончания проверки. 2 ил. 2 сортируемой информационной последовательности, вход 3 признака информации, вход 4 установки режима, вход 5 начальной установки, коммутатор 6, регистр 7, блок 8 памяти, триггер 9, элемент НЕ 10, распределитель 11 импульсов, элемент И 12. коммутатор 13, генератор 14 импульсов, регистр 15, счетчик 16, блок 17 сравнения, формирователь 18импульсоо, элемент И 19, элемент И 20, триггеры 21, 22. Формирователь 18 импульсов (фиг.2) содержит счетчики 18-1, V| сл 00 о со

| Насос | 1917 |

|

SU13A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для сравнения кодов | 1984 |

|

SU1171778A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1992-08-30—Публикация

1990-10-03—Подача