1136314

Изобретение относится к автоматизированным системам контроля цифровых и аналоговых устройств и может быть применено при контроле функционирования в реальном масштабе времени сложных быстродействующих многоканальных электронных и релейных объектов, на входы которых необходимо подавать времязависимые последователь- .Q ности и на выходах вести допусковый контроль ответных реакций по ампли- туде и по времени.

Цель изобретения - повышение быстродействий устройства.

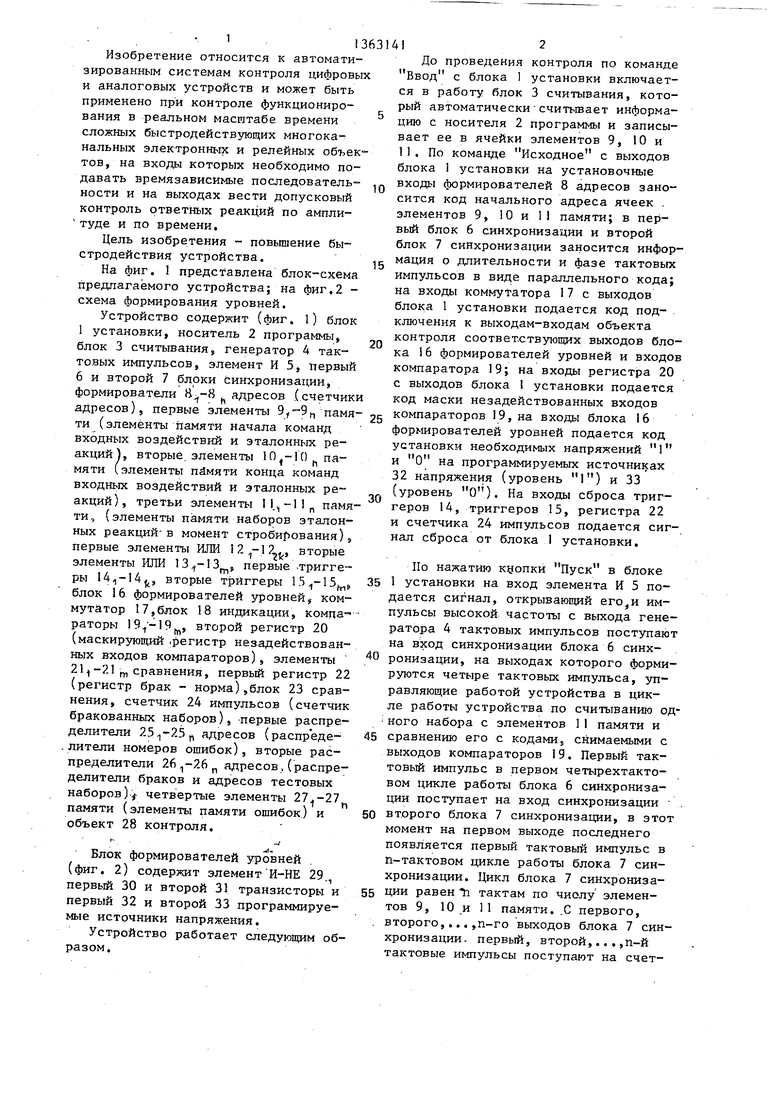

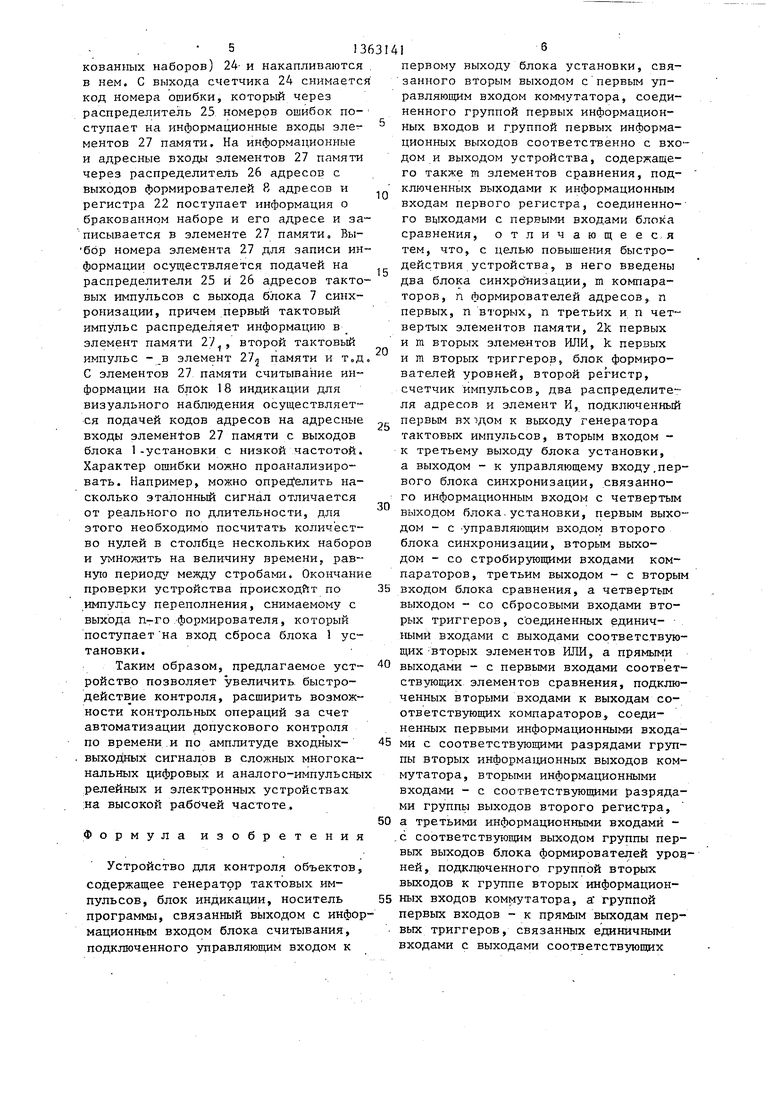

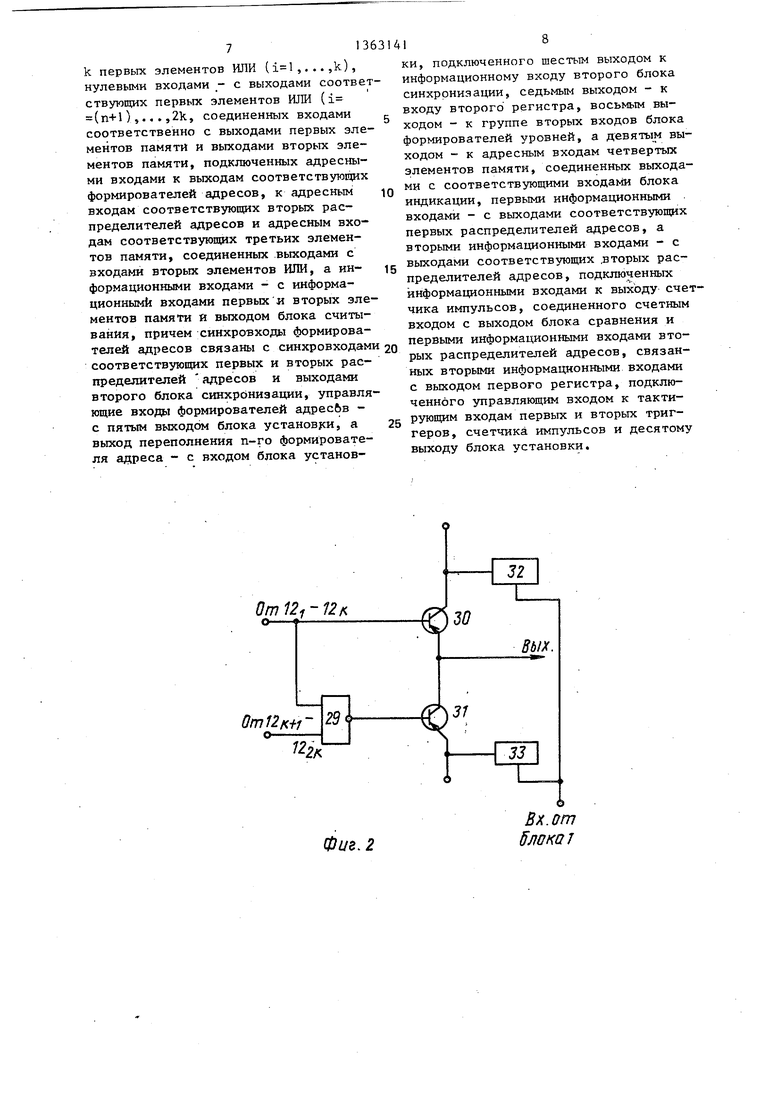

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 - схема формирования уровней.

Устройство содержит {фиг. 1) блок 1 установки, носитель 2 программы, блок 3 считывания, генератор 4 тактовых импульсов, элемент И 5, первый 6 и второй 7 блоки Ьинхронизации, ормирователи адресов .(счетчики дресов), первые элементы 9,-9 памя- ок ти (элементы памяти начала команд входных воздействий и эталонных реакций), вторые, элементы паяти (элементы памяти конца команд входных воздействий и эталонных реакций), третьи элементы 11.,-11„ памяти, (элементы памяти наборов эталонных реакций в момент строби|)ования), первые элементы ИЛИ 2 -1 , вторые элементы ИЛИ , первые -триггеры , вторые триггеры 35 блок 16 формирователей уровней комутатор 17,блок 18 индикации, компа- раторы 19., -19, второй регистр 20 (маскирующий .регистр незадействованных входов компараторов), элементы . 2Ц-.1 р, сравнения, первый регистр 22 (регистр брак - норма),блок 23 сравнения, счетчик 24 импульсов (счетчик бракованных наборов), первые распреелители адресов (распреде- 45 ители номеров ошибок), вторые расределители адресов,(распреелители браков и адресов тестовых наборов) четвертые элементы 27..-27 амяти (элементы памяти ошибок) и 50 объект 28 контроля.

30

Блок формирователей уровней (фиг. 2) содержит элемент И-НЕ 29., первый 30 и второй 31 транзисторы и первый 32 и второй 33 программируемые источники напряжения.

Устройство работает следующим образом.

g

к 5 5 0

0

5

2

До проведения контроля по команде Ввод с блока 1 установки включается в работу блок 3 считывания, который автоматическисчитьгоает информацию с носителя 2 программы и записывает ее в ячейки элементов 9, 10 и 11. По команде Исходное с выходов блока 1 установки на установочные входы формирователей 8 адресов заносится код начального адреса ячеек . элементов 9, 10 и 11 памяти; в первый блок 6 синхронизации и второй блок 7 синхронизации заносится информация о длительности и фазе тактовых импульсов в виде параллельного кода; на входы коммутатора 17 с выходов блока 1 установки подается код под- ключения к выходам-входам объекта контроля соответствующих выходов блока 16 формирователей уровней и входов компаратора 19; на входы регистра 20 с выходов блока 1 установки подается код маски незадействованных входов компараторов 19, на входы блока 16 формирователей уровней подается код установки необходимых напряжений 1 и О на программируемых источниках 32 напряжения (уровень 1) и 33 (уровень О). На входы сброса триггеров 14, триггеров 15, регистра 22 и счетчика 24 импульсов подается сигнал сброса от блока 1 установки.

По нажатию куопки Пуск в блоке 1 установки на вход элемента И 5 подается сиг нал, открывающий его,,и импульсы высокой частоты с выхода генератора 4 тактовых импульсов поступают на вход синхронизации блока 6 синхронизации, на выходах которого формируются четыре тактовых импульса, управляющие работой устройства в цикле работы устройства по считыванию одного набора с элементов 11 памяти и сравнению его с кодами, снимаемыми с выходов компараторов 19. Первый тактовый импульс в первом четырехтактовом цикле работы блока 6 синхронизации поступает на вход синхронизации второго блока 7 синхронизации, в этот момент на первом выходе последнего появляется первый тактовый импульс в п-тактовом цикле работы блока 7 синхронизации. Цикл блока 7 синхронизации равен fi тактам по числу элементов 9, 10 и 11 памяти. .С первого, второго,...,п-го выходов блока 7 синхронизации, первый, второй,...,п-й тактовые импульсы поступают на счет313

ные входы соответственно первого, второго,...,п-го формирователей 8 адреса. На выходах каждого формирователя 8 адреса формируются коды адресов: по первому тактовому импульсу с блока 7 синхронизации - на выходе первого формирователя 8 адреса, по второму - на выходе второго,....по п-у - на выходе п-го формирователя. Коды адресов с выходов формирователей 8 адресов поступают на адресные входы элементов 9, 10 и 11 йамяти tкoд адреса с выходов первого формирователя 8 адреса - на адресные входы первых элементов 9, И), и 11, памяти, в момент формирования первого тактового импульса на выходе блока 7 синхронизации; код адреса с выходов второго формирователя 8 адреса - на адресные входы вторых элементов 92 (j j к llj памяти, в моменты формирования второго тактового импульса на выходе блока 7 синхронизации и т.д. Блок 7 синхронизации вырабатывает I циклов по числу считываемых слов из элементов 9, 10 и 11 памяти. В каждом цикле в блоке 7 синхронизации вырабатывается п тактов. Таким образом, для считывания всех слов с элементов 9, 10 и 11 памяти блок 7 вырабатывает кп .тактов.

С информационных выходов каждого элемента 9 . памяти считывается пословно информация и .поступает на входы элементов ИЛИ 12 с номерами от 1 до k.

; С информационных выходов каждого элемента 10 памяти считывается пословно информация и поступает на входы элементов ИЛИ 12 с номерами от k+1 до 2k.

С информационных выходов каждого элемента 11 памяти, считывается пословно информация и поступает на входы элементов ИЛИ 13. Считывание информа- ции с элементов 9, 10 и 11 памяти происходит последовательно, сначала информация считывается с первых элементов, затем с вторых и т.д., затем с п-х, затем снова с первых и т.д.,. причем, кажда 1Й элемент ИЛИ 12-и 13 собирает информацию какого-либо определенного разрядаслов, считанных с п элементов 9, 10 и 11 памяти.

Информация с выходов элементов ИЛИ 12.-12. поступает на единичные установочные входы триггеров 14, информация с выходов на установочные нулевые входы триггеров 14, ин

формация с выходов элементов ИЛИ 13 - на единичные установочьгые входы триггеров 15. Состояние триггеров 14 не изменяется в момент считывания первого слова с элементов 10 памяти j, и изменяется в моменты считывания с элементов 10 информации о конце команд входных воздействий и эталонных реакций. ..С выходов триггеров 14 информация во временных последовательностях поступает на управляющие входы блока 16 формирователей уровней, с первой группы выходов которого через коммутатор 17 информация поступает на входы объекта 28 контроля, с второй группы выходов - на входы компараторов 19j на вторые входы которого поступает информация с выходов объекта 28 контроля через коммутатор 17, на стробирующие входы компараторов 19 подаются импульсы с выхода блока 6 синхронизации (2-й тактовый импульс). В моменты поступления стробов на входы компараторов 19 происходит сравнение напряжений О и М снимаемых с выходов объекта контроля, с их эталонными значениями набора, снимаемого с второй группы выходов блока 16. С выходов компараторов 19 на входы блока элементов 21 сравнения поступает двухпозиционный код; причем при норме с выходов компараторов высоких уровней снимается код 1, О, а с выходов компараторов низких уровней - код О, 1, при браке с выходов снимается код О, О.

В элементах 21 сравнения происхо- дит сравнение кодов, снимаемых с выхдов компараторов 19, с кодами набора снимаемыми с триггеров 15, результат сравнения заносится.в регистр 22 (регистр брак - норма). Если в регистре 22 все единицы, то это свидетельствует о соответствии , кодов эталонного и реального наборов;,наличие в рарядах блока 22 нулей свидетельствует о иесравнении наборов. С выходов -регистра 22 информация пост пает на входы блока 23 сравнения. Третий тактовый импульс с выхода блока 6 синхронизации опрагшвает блок 23 сравнения с высокой частотой. В моменты, когда.идет опрос блока 23 сравнения, с его выхода появятся импульсы в том случае, если в регистре 22 были разряды с нулевой информацией при сравнении наборов. Эти импульсы поступают на счетный вход счетчика (бракованных наборов) 24- и накапливаются в нем. С выхода счетчика 24 снимаетс код номера ошибки, который через распределитель 25, номеров ошибок поступает на информационные входы элементов 27 памяти. На информационные и адресные входы элементов 27 памяти через распределитель 26 адресов с выходов формирователей 8 адресов и регистра 22 поступает информация о бракованном наборе и его адресе и записывается в элементе 27 памяти, Вы- ббр номера элемента 27 для записи информации осуществляется подачей на распределители 25 и 26 адресов тактовых импульсов с выхода блока 7 синхронизации, причем первый тактовый импульс распределяет информацию в

элемент памяти 27., второй тактовый

1

импульс - в элемент 27,j памяти и т.д С элементов 27 памяти считывание информации на блок 18 индикации для визуального наблюдения осуществляется подачей кодов адресов на адресные входы элeмёнtoв 27 памяти с выходов блока 1-установки с низкой частотой. Характер ошибки можно проанализировать. Например, можно определить насколько эталонный сигнал отличается от реального по длительности, для этого необходимо посчитать количество нулей в столбце нескольких наборо и умножить на величину времени, равную периору между стробами. Окончани проверки устройства происходит по импульсу переполнения, снимаемому с выхода п-го/формирователя, который поступает на вход сброса блока 1 установки.

Таким образом, предлагаемое устройство позволяет увеличить быстродействие контроля, расширить возможности контрольных операций за счет автоматизации допускового контроля по времени.и по амплитуде входных- выходных сигналов в сложных многоканальных цифровых и аналого-импульсны релейных и электронных устройствах ;на высокой рабочей частоте.

Формула изобретения

Устройство для контроля объектов, содержащее генератор тактовых импульсов, блок индикации, носитель программы, связанный выходом с информационным входом блока считывания, подключенного управляющим входом к

первому выходу блока установки, свя- занного вторым выходом с первым управляющим входом коммутатора, соединенного группой первых информационных входов и группой первых информационных выходов соответственно с входом и выходом устройства, содержащего также m элементов сравнения, подключенных выходами к информационным входам первого регистра, соединенно-- го выходами с первыми входами блока сравнения, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены два блока синхронизации, m компара

5

0

Б

торов, п формирователей адресов, п первых, п вторых, п третьих и п четвертых элементов памяти, 2k первых и m вторых элементов ЩШ, k первых и m вторых триггеров, блок формирователей уровней, второй регистр, счетчик импульсов, два распределителя адресов и элемент И, подключенный первым к выходу генератора тактовых импульсов, вторым входом - к третьему выходу блока установки, а выходом - к управляющему входу,первого блока синхронизации, связанного информационным входом с четвертым выходом блока-установки, первым выходом - с -управляющим входом второго блока синхронизации, вторым выходом - со стробирующими входами компараторов, третьим выходом - с вторым входом блока сравнения, а четвертым выходом - со сбросовыми входами вторых триггеров, с оединенных единич- - нымй входами с выходами соответствующих -вторых элементов РШИ, а прямыми выходами - с первыми входами соответствующих элементов сравнения, подключенных вторыми входами к выходам соответствующих компараторов соединенных первыми информационными входами с соответствующими разрядами rpjrn- пы вторых информационных выходов коммутатора, вторыми информационными входами - с соответствующими разрядами группы выходов второго регистра, а третьими информационньми входами - с соответствующим выходом группы первых выходов блока формирователей ней, подключенного группой вторых выходов к группе вторых информацион- 5 ных входов коммутатора, а группой

первых входов - к прямым выходам пер- вых триггеров, связанных единичными входами с выходами соответствующих

0

5

0

713

k первых элементов ИЛИ (,...,k), нулевыми входами - с выходами соответствующих первых элементов ИЛИ (i (п+1),...,2k, соединенных входами соответственно с выходами первых элементов памяти и выходами вторых элементов памяти, подключенных адресными входами к выходам соответствующих формирователей адресов, к адресньш входам соответствующих вторых распределителей адресов и адресным входам соответствующих третьих элементов памяти, соединенных выходами с входами вторых элементов ИЛИ, а ин- формационными входами - с информационными входами первых и вторых элементов памяти и выходом блока считывания, причем синхровходы формирователей адресов связаны с синхровходами соответствующих первых и вторых распределителей адресов и выходами второго блока синхронизации, управляющие входы формирователей адресЬв - с пятым выходом блока установки, а выход переполнения п-го формирователя адреса - с входом блока установки, подключенного шестым выходом к информационному входу второго блока синхронизации, седьмым выходом - к входу второго регистра, восьмым выходом - к группе вторых входов блока формирователей уровней, а девятым выходом - к адресным входам четвертых элементов памяти, соединенных выходами с соответствующими входами блока индикации, первыми информационными входами - с выходами соответствуюпщх первых распределителей адресов, а вторыми информационными входами - с выходами соответствующих .вторых распределителей адресов, подключенных информационными входами к выходу счечика импульсов, соединенного счетным входом с выходом блока сравнения и первыми информационными входами вторых распределителей адресов, связанных вторыми информационными входами с выходом первого регистра, подключенного управляющим входом к тактирующим входам первых и вторых триггеров, счетчика импульсов и десятому выходу блока установки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки параметров непериодических импульсных сигналов | 1986 |

|

SU1336027A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля больших интегральных схем памяти | 1984 |

|

SU1179375A1 |

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля монотонно изменяющегося кода | 1988 |

|

SU1658190A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1262506A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

Изобретение относится к автоматизированным системам контроля .цифровых и аналоговых устройств и может быть применено при контроле функционирования в реальном масштабе времени быстродействующих объектов. Цель изобретения - повьшение быстродейст й .Вия устройства. Устройство содержит блок 1 установки, носитель программы 2, блок 3 считывания, генератор 4 тактовых импульсой, элемент И 5, первый 6 и второй 7 блоки синхронизации, формирователи 8,-8 адресов, первые , вторые 10 ,-10 и третьи элементы памяти, первые элементы Ш1И l,- . ,вторые элементы ИЛИ , первые 14,-14 и вторые триггеры, блок 16 формирователей уровней, коммутатор 17, блок 18 индикации, компараторы 19,- 19,второй регистр 20, элементы 21 сравнения, первый регистр 22,. блок 23 сравнения, счетчик 24 импульсов, первые 25.,-25f, и вторые распределители аДресов, четвертые элементы памяти 27 -27,. 2 ил. с (Л оо О5 о:

Omj2j 72 А

Qm12n+j 2л

Фиг. 2

о

Вх.от 5лока7

| ОПИСАНИЕ ИЗОБРЕТЕНИЯ | 0 |

|

SU377738A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля электронных объектов | 1978 |

|

SU679945A1 |

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-12-30—Публикация

1985-11-21—Подача