Изобретение относится к автоматике и вычислительной технике И может быть использовано для построения высоконадежных микропроцессорных систем.

Целью изобретения является повышение достоверности информации и расширение области применения устройства за .счет возможности работы в дуплексном режиме..

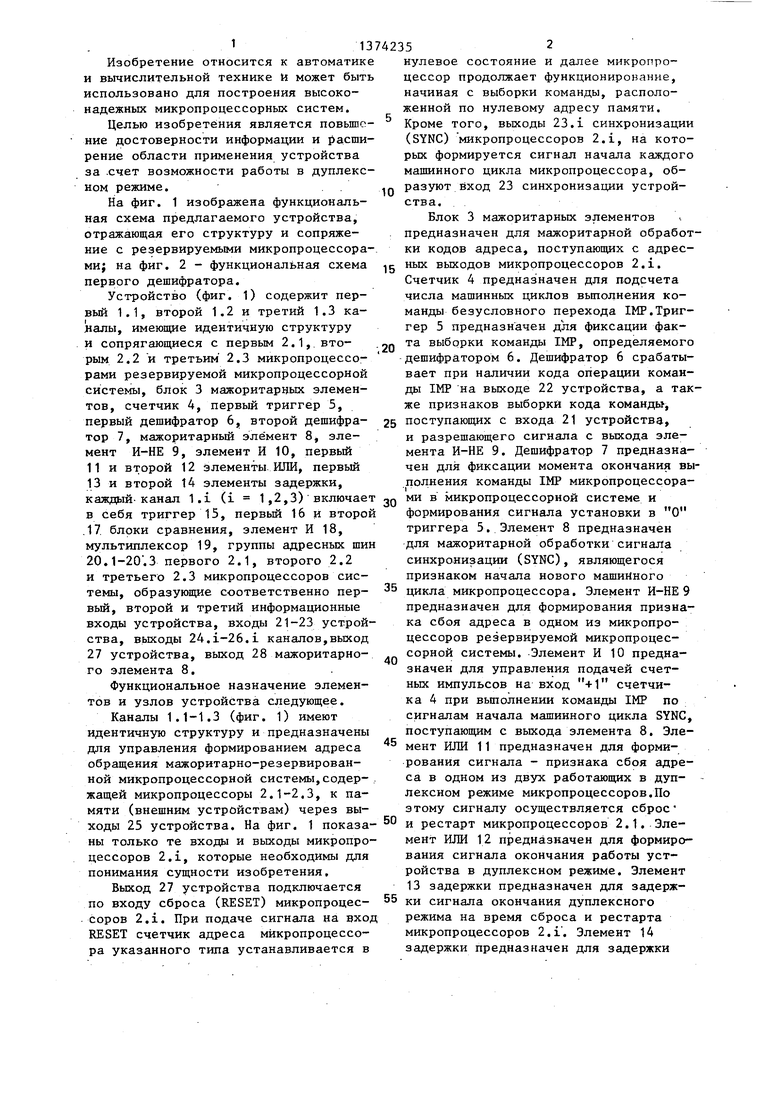

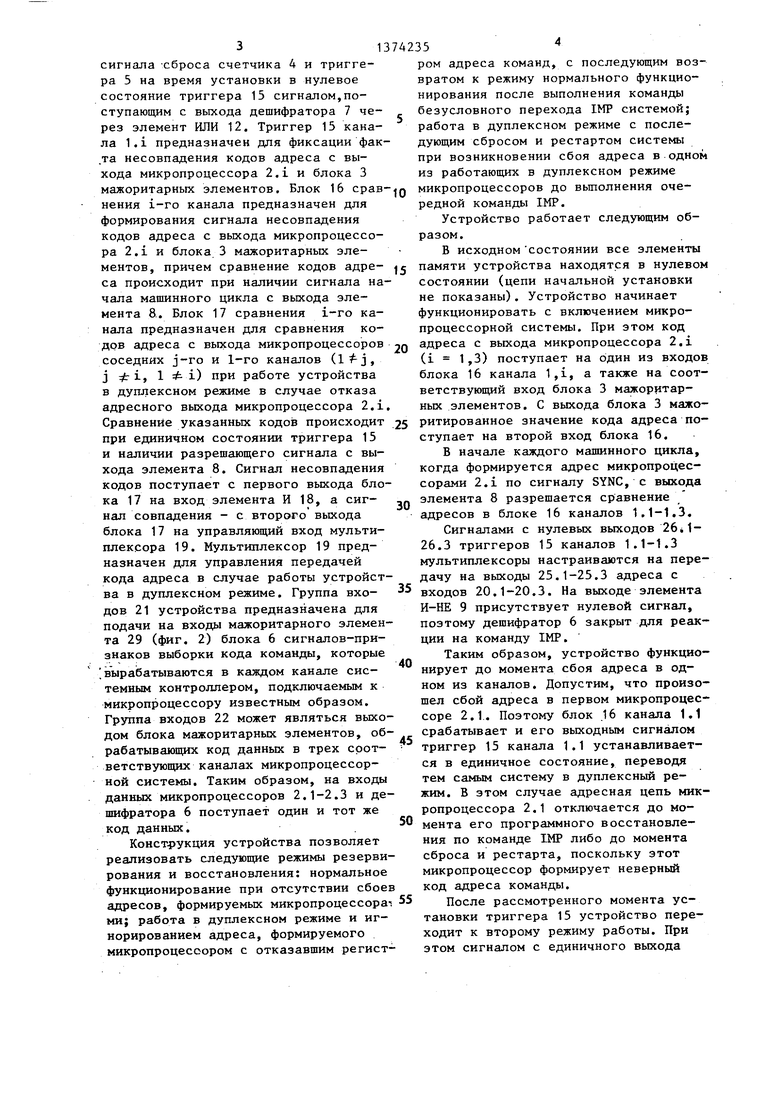

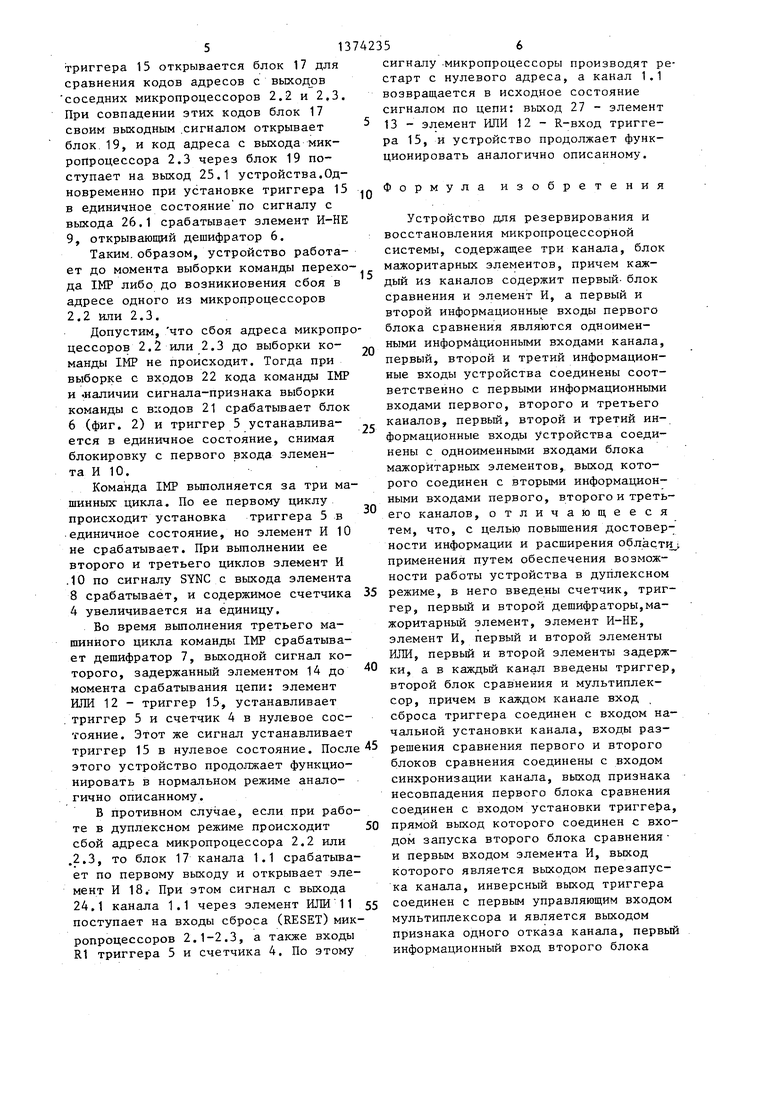

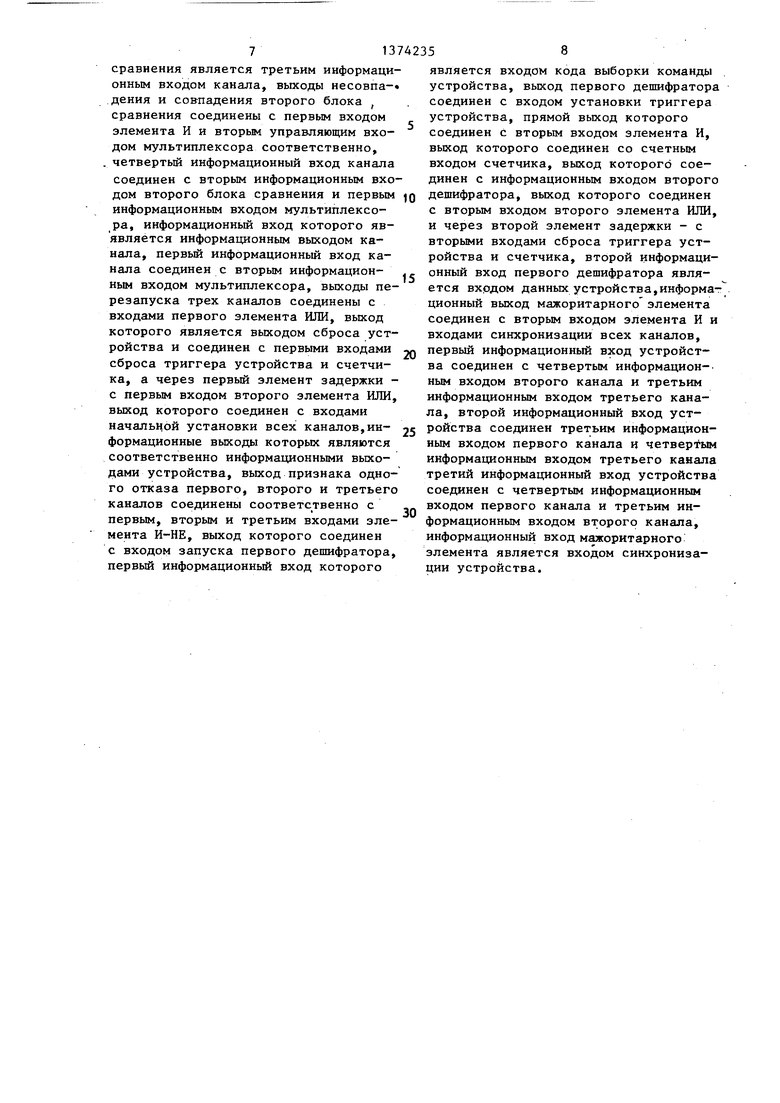

На фиг. 1 изображена функциональная схема предлагаемого устройства, отражающая его структуру и сопряжение с резервируемыми микропроцессорами; на фиг, 2 - функциональная схема первого дешифратора.

Устройство (фиг. 1) содержит пер- вьй 1.1, второй 1.2 и третий 1.3 ка- Зналы, имеющие идентичную структуру и сопрягающиеся с первым 2.1,.вто- рым 2.2 и третьим 2.3 микропроцессорами резервируемой микропроцессорной системы, блок 3 мажоритарных элементов, счетчик 4, первый триггер 5, первый дешифратор 6, второй дешифра- тор 7, мажоритарный элемент 8, элемент И-НЕ 9, элемент И 10, первый 11 и второй 12 элементы ИЛИ, первый 13 и второй 14 элементы задержки, каждый-канал 1.1 (i 1,2,3) включает в себя триггер 15, первый 16 и второй .17 блоки сравнения, элемент И 18, мультиплексор 19, группы адресных шин 20.1-20.3 первого 2.1, второго 2.2 и третьего 2.3 микропроцессоров системы, образующие соответственно пер- вый, второй и третий информационные входы устройства, входы 21-23 устройства, выходы 2,i-26,1. каналов,выход 27 устройства, выход 28 мажоритарно- го элемента 8.

Функциональное назначение элементов и узлов устройства следующее.

Каналы 1.1-1.3 (фиг. 1) имеют идентичную структуру и предназначены для управления формированием адреса обращения мажоритарно-резервированной микропроцессорной системы,содержащей микропроцессоры 2.1-2,3, к памяти (внешним устройствам) через выходы 25 устройства. На фиг. 1 показа- ны только те входы и выходы микропроцессоров 2.1, которые необходимы для понимания сущности изобретения.

Выход 27 устройства подключается по входу сброса (RESET) микропроцес- соров 2.1. При подаче сигнала на вход RESET счетчик адреса микропроцессора указанного типа устанавливается в

g

Q 5 Q

5

нулевое состояние и далее микропроцессор продолжает функционирование, начиная с выборки команды, расположенной по нулевому адресу памяти. Кроме того, выходы 23.1 синхронизации (SYNC) микропроцессоров 2.1, на которых формируется сигнал начала каждого машинного цикла микропроцессора, образуют вход 23 синхронизации устройства.

Блок 3 мажоритарных элементов предназначен для мажоритарной обработки кодов адреса, поступающих с адресных выходов микропроцессоров 2.1. Счетчик 4 предназначен для подсчета числа машинных циклов выполнения команды безусловного перехода IMP.Триггер 5 предназначен для фиксации факта выборки команды IMP, определяемого дешифратором 6. Дешифратор 6 срабатывает при наличии кода операции команды IMP на выходе 22 устройства, а также признаков выборки кода команды, поступающих с входа 21 устройства, и разрешающего сигнала с выхода элемента И-НЕ 9. Дешифратор 7 предназначен для фиксации момента окончания выполнения команды IMP микропроцессорами в микропроцессорной системе и формирования сигнала установки в О триггера 5. Элемент 8 предназначен для мажоритарной обработки сигнала синхронизации (SYNC), являющегося признаком начала нового машинного цикла микропроцессора. Элемент И-НЕ9 предназначен для формирования признака сбоя адреса в одном из микропроцессоров резервируемой микропроцессорной системы. Элемент И 10 предназначен для управления подачей счетных импульсов на вход +1 счетчика 4 при выполнении команды IMP по сигналам начала машинного цикла SYNC, поступающим с выхода элемента 8. Элемент ШШ 11 предназначен для формирования сигнала - признака сбоя адреса в одном из двух работающих в дуплексном режиме микропроцессоров.По этому сигналу осуществляется сброс и рестарт микропроцессоров 2.1. Элемент ИЛИ 12 предназначен для формирования сигнала окончания работы устройства в дуплексном режиме. Элемент 13 задержки предназначен для задержки сигнала окончания дуплексного режима на время сброса и рестарта микропроцессоров 2.1. Элемент 14 задержки предназначен для задержки

сигнала -сброса счетчика 4 и триггера 5 на время установки в нулевое состояние триггера 15 сигналом,поступающим с выхода дешифратора 7 через элемент ИЛИ 12. Триггер 15 канала 1.1 предназначен для фиксации фак- .та несовпадения кодов адреса с выхода микропроцессора 2.1 и блока 3 мажоритарных элементов. Блок 16 сравнения 1-го канала предназначен для формирования сигнала несовпадения кодов адреса с выхода микропроцессора 2.1 и блока 3 мажоритарных элементов, причем сравнение кодов адре- са происходит при наличии сигнала начала машинного цикла с выхода элемента 8. Блок 17 сравнения 1-го канала предназначен для сравнения кодов адреса с выхода микропроцессоров соседних j-ro и 1-го каналов (, j i, 1 : 1) при работе устройства в дуплексном режиме в случае отказа адресного выхода микропроцессора 2.1 Сравнение указанных кодов происходит при единичном состоянии триггера 15 и наличии разрешающего сигнала с выхода элемента 8. Сигнал несовпадения кодов поступает с первого выхода блока 17 на вход элемента И 18, а сигнал совпадения - с второго выхода блока 17 на управляющий вход мультиплексора 19. Мультиплексор 19 предназначен для управления передачей кода адреса в случае работы устройства в дуплексном режиме. Группа вхо- дов 21 устройства предназначена для подачи на входы мажоритарного элемента 29 (фиг. 2) блока 6 сигналов-признаков выборки кода команды, которые

вырабатываются в каждом канале системным контроллером, подключаемым к микропроцессору известным образом. Группа входов 22 может являться выходом блока мажоритарных элементов, обрабатывающих код данных в трех соответствующих каналах микропроцессорной системы. Таким образом, на входы данных микропроцессоров 2.1-2.3 и дешифратора 6 поступает один и тот же код данных.

Конструкция устройства позволяет реализовать следующие режимы резервирования и восстановления: нормальное функционирование при отсутствии сбоев адресов, формируемых микропроцессора ми; работа в дуплексном режиме и игнорированием адреса, формируемого микропроцессором с отказавшим регист

0

л с 5

5

0

0

5

0

ром адреса команд, с последующим возвратом к режиму нормального функционирования после выполнения команды безусловного перехода IMP системой; работа в дуплексном режиме с последующим сбросом и рестартом системы при возникновении сбоя адреса в одном из работающих в дуплексном режиме микропроцессоров до вьшолнения очередной команды IMP.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии (цепи начальной установки не показаны). Устройство начинает функционировать с включением микропроцессорной системы. При этом код адреса с выхода микропроцессора 2.1 (,3) поступает на один из входов блока 16 канала 1,1, а также на соответствующий вход блока 3 мажоритарных элементов. С выхода блока 3 мажо- ритированное значение кода адреса поступает на второй вход блока 16.

В начале каждого машинного цикла, когда формируется адрес микропроцессорами 2.1 по сигналу SYNC, с выхода элемента 8 разрешается сравнение адресов в блоке 16 каналов 1.1-1.3.

Сигналами с нулевых выходов 26 И - 26.3 триггеров 15 каналов 1.1-1.3 мультиплексоры настраиваются на передачу на выходы 25.1-25.3 адреса с входов 20.1-20.3. На выходе элемента И-НЕ 9 присутствует нулевой сигнал, поэтому дешифратор 6 закрыт для реакции на команду IMP.

Таким образом, устройство функционирует до момента сбоя адреса в одном из каналов. Допустим, что произошел сбой адреса в первом микропроцессоре 2.1. Поэтому блок 16 канала 1.1 срабатывает и его выходным сигналом триггер 15 канала 1.1 устанавливается в единичное состояние, переводя тем самым систему в дуплексный режим. В этом случае адресная цепь микропроцессора 2.1 отключается до момента его программного восстановления по команде IMP либо до момента сброса и рестарта, поскольку этот микропроцессор формирует неверный код адреса команды.

После рассмотренного момента установки триггера 15 устройство переходит к второму режиму работы. При этом сигналом с единичного выхода

триггера 15 открывается блок 17 для сравнения кодов адресов с выходов

соседних микропроцессоров 2.2 и 2,3. При совпадении этих кодов блок 17 своим выходным .сигналом открывает блок 19, и код адреса с выхода микропроцессора 2.3 через блок 19 поступает на выход 25.1 устройства.Одновременно при установке триггера 15 в единичное состояние по сигналу с выхода 26.1 срабатывает элемент И-НЕ 9, открывающий дешифратор 6.

Таким, образом, устройство работает до момента выборки команды перехода IMP либо до возникновения сбоя в адресе одного из микропроцессоров 2.2 или 2.3.

Допустим, что сбоя адреса микропр цессоров 2.2 или 2.3 до выборки команды IMP не происходит. Тогда при выборке с входов 22 кода команды IMP и .наличии сигнала-признака выборки команды с входов 21 срабатывает блок 6 (фиг. 2) и триггер 5 устанавливается в единичное состояние, снимая блокировку с первого входа элемента И Ю.

Команда IMP вьшолняется за три машинных: цикла. По ее первому циклу происходит установка триггера 5 в единичное состояние, но элемент И 10 не срабатывает. При выполнении ее второго и третьего циклов элемент И

.10 по сигналу SYNC с выхода элемента 8 срабатывает, и содержимое счетчика 4 увеличивается на единицу.

Во время вьшолнения третьего машинного цикла команды IMP срабатывает дешифратор 7, выходной сигнал которого, задержанный элементом 14 до момента срабатывания цепи: элемент ИЛИ 12 - триггер 15, устанавливает триггер 5 и счетчик 4 в нулевое состояние. Этот же сигнал устанавливает триггер 15 в нулевое состояние. После этого устройство продолжает функционировать в нормальном режиме аналогично описанному.

В противном случае, если при работе в дуплексном режиме происходит сбой адреса микропроцессора 2.2 или

.2.3, то блок 17 канала 1.1 срабатьгеа- ет по первому выходу и открывает элемент И 18.- При этом сигнал с выхода 24.1 канала 1.1 через элемент ИЛИ 11 поступает на входы сброса (RESET) микропроцессоров 2.1-2.3, а также входы R1 триггера 5 и счетчика 4. По этому

0

5

0

5

0

5

0

5

0

5

сигналу -микропроцессоры производят рестарт с нулевого адреса, а канал 1.1 возвращается в исходное состояние сигналом по цепи: выход 27 - элемент 13 - элемент ИЛИ 12 - К-вход триггера 15, и устройство продолжает функционировать аналогично описанному.

Формула изобретения

Устройство для резервирования и восстановления микропроцессорной системы, содержащее три канала, блок мажоритарных элементов, причем каждый из каналов содержит первый- блок сравнения и элемент И, а первый и второй информационные входы первого блока сравнения являются одноименными информационными входами канала, первый, второй и третий информационные входы устройства соединены соответственно с первыми информационными входами первого, второго и третьего каналов, первый, второй и третий информационные входы устройства соединены с одноименными входами блока мажоритарных элементов, выход которого соединен с вторыми информационными входами первого, второго и третьего каналов, отличающееся тем, что, с целью повышения достоверности информации и расширения области применения путем обеспечения возможности работы устройства в дуплексном режиме, в него введены счетчик, триггер, первый и второй дешифраторы,мажоритарный элемент, элемент И-НЕ, элемент И, первый и второй элементы ИЛИ, первьй и второй элементы задержки, а в каждый канал введены триггер, второй блок сравнения и мультиплексор, причем в каждом канале вход сброса триггера соединен с входом начальной установки канала, входы разрешения сравнения первого и второго блоков сравнения соединены с входом синхронизации канала, выход признака несовпадения первого блока сравнения соединен с входом установки триггера, прямой выход которого соединен с входом запуска второго блока сравнения и первым входом элемента И, выход которого является выходом перезапуска канала, инверсный выход триггера соединен с первым управляющим входом мультиплексора и является выходом признака одного отказа канала, первый информационный вход второго блока

сравнения является третьим информационным входом канала, выходы несовпа- дения и совпадения второго блока , сравнения соединены с первым входом элемента И и вторым управляющим входом мультиплексора соответственно, . четвертый информационный вход канала соединен с вторым информационным вхоявляется входом кода выборки команды устройства, выход первого дешифратора соединен с входом установки триггера устройства, прямой выход которого соединен с вторым входом элемента И, выход которого соединен со счетным входом счетчика, выход которого соединен с информационным входом второго

дом второго блока сравнения и первым д дешифратора, выход которого соединен

информационным входом мультиплексора, информационный вход которого яв- является информационным выходом канала, первый информационный вход канала соединен с вторым информационным входом мультиплексора, выходы перезапуска трех каналов соединены с входами первого элемента ИЛИ, выход которого является выходом сброса устройства и соединен с первыми входами сброса триггера устройства и счетчика, а через первый элемент задержки - с первым входом второго элемента ИЛИ, выход которого соединен с входами начальной установки всех каналов,ин- формационные выходы которых являются соответственно информационными выходами устройства, выход признака одного отказа первого, второго и третьего каналов соединены соответственно с

первым, вторым и третьим входами элемента И-НЕ, выход которого соединен с входом запуска первого дешифратора, первьй информационный вход которого

является входом кода выборки команды устройства, выход первого дешифратора соединен с входом установки триггера устройства, прямой выход которого соединен с вторым входом элемента И, выход которого соединен со счетным входом счетчика, выход которого соединен с информационным входом второго

п 5

0

с вторым входом второго элемента ИЛИ, и череэ второй элемент задержки - с вторыми входами сброса триггера устройства и счетчика, второй информационный вход первого дешифратора является входом данных устройства,информационный выход мажоритарного элемента соединен с вторым входом элемента И и входами синхронизации всех каналов, первый информационный вход устройства соединен с четвертым информационным входом второго канала и третьим информационным входом третьего канала, второй информационный вход устройства соединен третьим информационным входом первого канала и четвертым информационным входом третьего канала третий информационный вход устройства соединен с четвертым информационным входом первого канала и третьим информационным входом второго канала, информационный вход мажоритарного элемента является входом синхронизации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Трехканальное устройство для управления синхронизацией микропроцессорной системы | 1985 |

|

SU1352475A1 |

| Многоканальное устройство для управления пуском и рестартом при сбоях микропроцессорной системы | 1985 |

|

SU1247869A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

Изобретение относится к области автоматики и вычислительной техники, может быть использовано для построения высоконадежных микропроцессорных систем. Устройство предназначено для использования в резервируемых трехканальных микропроцессорных системах для реализации мажоритарной обработки адресных сигналов и организации работы системы в дуплексном режиме при сбое в одном канале, что обеспечивает более широкую по сравнению с прототипом область применения устройства и позволяет повысить достоверность информации за счет возможности устройства в дуплексном режиме. Указанные преимущества обеспечиваются за счет введения в каждый канал триггеров и соответствующих связей, позволяющих фиксировать наличие сбоя в каждом из каналов и отключать неисправный канал, введения дополнительных блоков сравнения в каждый канал, позволяющих выявить наличие повторного сбоя, т.е. возникшего при работе в дуплексном режиме,, а также введения дешифраторов и счетчика, позволяющих осуществлять восстановление микропроцессорной системы по команде безусловного перехода. 2 ил. S (Л :о 4 Ю : :л

| Мажоритарно-резервированное устройство | 1981 |

|

SU982187A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мажоритарно-резервированное устройство | 1983 |

|

SU1156077A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-15—Публикация

1986-06-25—Подача