Изобретение относится к электронике и может использоваться в устройствах усиления электрических сигналов.

Известен выходной ключевой каскад импульсного усилителя 1, содержащий первый n-p-n-транзистор, базовый контакт которого является входом устройства. Коллектор подключен к первому контакту первого резистора и базе второго п-р-п-тран- зистора, эмиттер подключен к первому контакту второго резистора и базе третьего п-р- n-транзистора. Второй контакт первого резистора подключен к коллектору второго n-p-n-транзистора и положительной шине питания. Второй контакт второго резистора подключен к эмиттеру третьего п-р-п-тран- зистора и общему проводу. Эмиттер второго n-p-n-транзистора подключен к коллектору третьего n-p-n-транзистора и образуют выходи/ю линию.

Недостаток данного устройства состоит в то и, что во время переключения выходного каскада из состояния логического О в состояние логической 1 и во время обратного переключения происходит кратковременное протекание сквозного тока через второй и третий n-p-n-трэнзисторы. Это снижает КПД устройства и его надежность.

Известен также выходной ключевой каскад импульсного усилителя 2, содержащий первый и второй логические элементы НЕ. причем вход первого элемента НЕ образует входную шину устройства. Выход первого элемента НЕ соединен со входом второго элемента НЕ и с базой второго р-п- р-транзистора и базой второго п-р-п-тран- зистора. Коллектор второго р-п-п-тран- зисторз соединен с коллектором второго п- p-n-транзистора и с первым контактом резистора (нагрузки). Выход второго элемента НЕ соединен с базой первого р-п-р-транзи- стора и с базой второго п-р-п-транзитора. Коллектор первого p-n-p-транзистора соединен с коллектором первого п-р-п-транзи- стора и со вторым контактом резистора (нагрузки). Эмиттер первого р п-р-трэнзи- стора соединен с эмиттером второго р-п-р- транзистора и с положительной шиной

Ч

Ј

ig

|ЧЭ

питания. Эмиттер первого п-р-п-транзисто- ра соединен с эмиттером второго п-р-п- транзистора и с общим проводом.

Недостаток данного устройства состоит в том, что во время переключения выходного кс-скада импульсного усилителя из состо- яния логического О в состояние логической 1 и обратно происходит кратковременное протекание сквозного тока по цепи: положительная шина питания, первый p-n-p-транзистор, первый п-р-п-транзи- стор, общий провод, а также по цепи; положительная шина питания, второй р-п-р- транзистор, второй n-p-n-транзистор, общий провод. Это снижает КПД устройства и его надежность.

Цепь изобретения - повышение КПД и надежности устройства.

Эта цель достигается тем, что в выходной ключевой каскад импульсного усилите- ля, содержащий первый и второй логические элементы НЕ, первый и второй p-n-p-транзисторы, первый и второй п-р-п- транзисторы, резистор, выход первого элемента НЕ соединен с базой второго n-p-n-транзистора, а выход второго элемента НЕ соединен с базой первого р-п-р-тран- зистора, эмигтер которого соединен с эмиттером второго p-n-p-транзистора и с положительной шиной питания, а коллектор второго p-n-p-транзистора соединен с коллектором второго n-p-n-транзистора и с первым выводом резистора, коллектор первого p-n-p-транзистора соединен с коллектором первого n-p-n-транзистора и со вторым выводом резистора, эмиттер первого п-р-п- транзистора соединен с эмиттером второго n-p-n-транзистора и с общим проводом, дополнительно ведены третий элемент НЕ, первый и второй элементы И-НЕ, первый и второй элементы ИЛИ-НЕ, первый, второй третий и четвертый элементы задержки, вход третьего элемента НЕ соединен со входной шиной, а также со вторым входом второго элемента И-НЕ и вторым входом второго элемента ИЛИ-НЕ, выход третьего элемента НЕ соединен с первым входом первого элемента И-НЕ и первым входом первого элемента ИЛИ-НЕ. выход первого элемента И-НЕ соединен через первый элемент задержки с базой второго р-п-р-тран- зисторэ и первым входом второго элемента И-НЕ, выход которого через второй элемент задержки соединен со вторым входом первого элемента И-НЕ и входом первого элемента НЕ, выход первого элемента ИЛИ-НЕ через третий элемент задержки соединен с входом второго элемента НЕ и первым входом второго элемента ИЛИ-НЕ, выход которого через четвертый элемент задержки соединен с базой первого п-р-п- транзистора.

Сравнительный анализ предлагаемого устройства с прототипом показывает, что

заявляемое устройство отличается наличием новых элементов: элемента НЕ, элементов И-НЕ, ИЛИ-НЕ, а также элементов задержки и их связями с остальными элементами схемы. Таким образом, заявляемое

0 устройство соответствует критерию изобретения новизна,

Предложенное техническое решение соответствует критерию существенные отличия, поскольку при поиске не обнаруже5 ны устройства, содержащие отличительные признаки заявленного устройства.

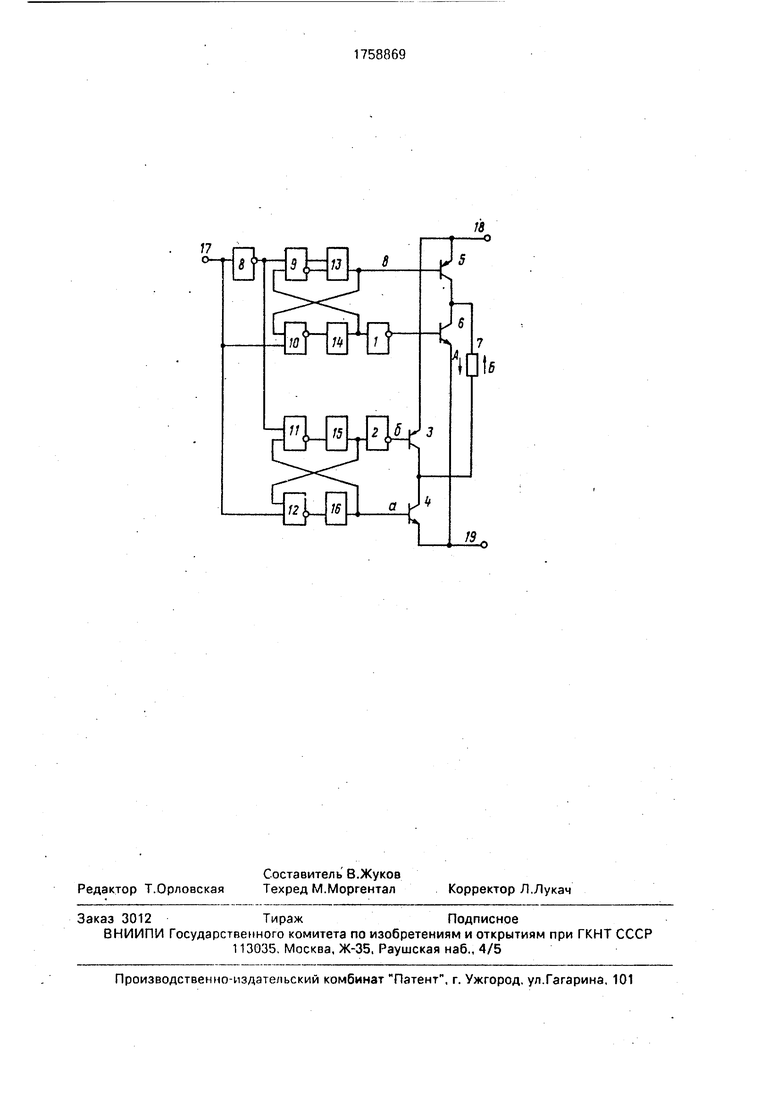

На фиг.1 представлена структурная схема устройства, которое содержит первый элемент НЕ 1, второй элемент НЕ 2, первый

0 р-п-р-трназистор 3, первый п-р-п-транзи- стор 4, второй р-п-р-транзистор 5, второй п-р-п-транзистор 6, резистор 7, третий элемент НЕ 8, первый элемент И-НЕ 9, второй элемент И-НЕ 10, первый элемент ИЛИ-НЕ

5 11, второй элемент ИЛИ-НЕ 12, первый второй, третий, четвертый элементы задержки

13- 16, входную шину 17, положительную шину 18, общий провод 19.

Вход третьего элемента НЕ 8 подклю- 0 чен ко второму входу второго элемента И- НЕ 10, второму входу второго элемента И-НЕ 12 и входной шине 17. Выход третьего элемента НЕ 8 соединен с первым входом первого элемента И-НЕ 9 и первым входом 5 первого элемента ИЛИ-НЕ 11, Выход первого элемента И-НЕ 9 подключен к входу первого элемента 13 задержки, выход которого подключен к первому входу второго элемента И-ИЕ 10 и базе второго р-п-р- 0 транзистора 5. Выход второго элемента И-НЕ 10 подключен к входу второго элемента

14задержки, выход которого подключен к входу первого элемента НЕ 1. Выход первого элемента НЕ 1 подключен к базе второго

5 n-p-n-трэнзистора б. Выход первого элемента ИЛИ-НЕ 11 соединен с входом третьего элемента 15 задержки, выход которого соединен со входом второго элемента НЕ 2 и первым входом второго элемента ИЛИ-НЕ

0 12. Выход второго элемента ИЛИ-НЕ 12 соединен с входом четвертого элемента 16 задержки, выход которого соединен со вторым входом первого элемента ИЛИ-НЕ 11 и базой первого n-p-rt-транзистора 4. Выход

5 второго элемента НЕ 2 соединен с базой первого p-n-p-транзистора З. Коллектор первого р-п-р-транзистора 3 соединен с коллектором первого п-р-п-транзистора 4 и со вторым контактом резистора 7. Коллектор второго р-п-р-транзистора 5 соединен с коллектором второго n-p-n-транзистора бис контактом резистора 7. Эмиттер первого р- п-р-транзистора 3 подключен к эмиттеру второго р-п-р-транзистора 5 и положительной шине 18 пшания. Эмиттер первого п-р- п-транзистора 4 соединен с эмиттером второго п-р-п-трзнзистора 6 и общим проводом 19.

Временная диаграмма работы устройства приведена на фиг.2.

Устройство работает следующим образом. При входном сигнале на входной шине 17, соответствующем логическому О, на выходе второго элемента И-НЕ 10 установится сигнал уровня логической 1. После прохождения этого сигнала через второй элемент 14 задержки он поступает на второй вход первого элемента И-НЕ 9 вход первого элемента НЕ 1. В результате этого на выходе первого элемента НЕ 1 имеется сигнал уровня логического О (фиг.2,г). Следовательно, второй n-p-n-транзистор б закрыт. На первый вход первого элемента И-Н Е 9 поступает сигнал уровня логической 1. На его выходе формируется сигнал уровня логического О, который через элемент 13 задержки поступает на базу второго р-п-р-транзистора 5 (фиг.2,в). В результате этого второй р-п-р-транзистор 5 открыт. С выхода третьего элемента НЕ 8 на первый вход первого элемента ИЛ И-НЕ 11 поступает сигнал уровня логической 1. На выходе первого элемента ИЛИ-НЕ 11 установится сигнал уровня логического О, который через третий элемент 15 задержки поступает на вход второго элемента НЕ 2 и на первый вход второго элемента ИЛИ-НЕ 12. В результате этого на выходе второго элемента ИЛИ-НЕ 12 имеется сигнал уровня логической 1, который через четвертый элемент 16 задержки поступает на базу первого п-р- п-транзистора 4 (фиг.2,а). На выходе второго элемента НЕ 2 установится также уровень логической 1 (фиг.2,б). Следовательно, первый р-п-р-транзистор 3 закрыт, а первый п-р-п-траизистор 4 открыт. В результате этого ток по резистору 7 протекает в направлении А (сверху вниз).

При поступлении на вход устройства сигнала уровня логической 1 на выходах третьего элемента НЕ 8 и на выходе второго элемента ИЛИ-НЕ 12 установятся сигналы уровня логического О. Вследствие этого закроется первый п-р-п-транзистор 4. На выходе первого элемента И-НЕ 9 установится сигнал уровня логической 1, который через первый элемент задержки поступит на базу второго р-п-р-транзистора 5 и закроет его. Прекратится ток через резистор. Затем сигнал уровня логического О,

сформированный на выходе второго элемента И-НЕ 10, поступает через второй элемент 14 задержки на вход первого элемента НЕ 1. На его выходе формируется сигнал

уровня логической 1, который открывает второй п-р-п-транзистор 6. Входной сигнал логической 1 поступает также на вход второго элемента ИЛИ-НЕ 12, Вследствие этого на выходе второго элемента ИЛИ-НЕ 12

0 формируется сигнал логического О, который через четвертый элемент 16 задержки поступает на базу первого п-р-п-транзисто- ра 4 и закрывает его. Данный сигнал логического О поступает также на второй вход

5 первого элемента ИЛИ-НЕ 11, На выходе первого элемента 11 ИЛИ-НЕ формируется сигнал логической 1, который через третий элемент 15 задержки поступает на вход второго элемента НЕ 2. На его выходе форми0 руется сигнал уровня логического О, которым открывается первый р-п-р-транзистор 3. Начинает протекать ток через резистор 7 в направлении Б (снизу вверх). В связи с разделением по времени процесса

5 закрывания ранее открытых транзисторов (4 и 5) от процесса открывания ранее закрытых транзисторов (3 и 6) при изменении входного сигнала от уровня О до уровня 1 протекание сквозных токов через тран0 зисторы (5 и 6, 3 и 4) сведено к минимуму.

При изменении уровня входного сигнала от логической 1 до логического О на выходе второго элемента И-НЕ 10 устанавливается сигнал логической 1. Далее этот

5 сигнал через второй элемент 14 задержки поступает на второй вход первого элемента И-НЕ 9 и вход первого элемента НЕ 1. На выходе первого элемента ИЛИ-НЕ 11 устанавливается уровень логического О. Далее

0 сигнал логического О проходит через третий элемент 15 задержки и поступает на вход второго элемента НЕ 2 и первый вход второго элемента ИЛИ-НЕ 12. На выходе второго элемента Н Е 2 устанавливается уро5 вень логической 1. Первый р-п-р-транзистор 3 закрывается. Под воздействием входного сигнала, равного логическому О, на выходе второго элемента И-НЕ 10 устанавливается сигнал уровня логической 1.

0 Через промежуток времени, равный времени задержки t3 второго элемента 14 задержки, данный сигнал логической 1 поступает на вход первого элемента НЕ 1. На выходе данного элемента формируется

5 сигнал логического О, который закрывает второй п-р-п-транзистор 6, Ток через резистор 7 прекращается. На выходе второго элемента ИЛИ-НЕ 12 устанавливается уровень логической 1. Далее данный сигнал проходит через четвертый элемент 16 задержки и через время задержки, равное t3, открывает первый n-p-n-транзистор А. На выходе первого элемента И-НЕ 9 устанав- ливается уровень логического О. Далее сигнал уровня логического О проходит че- рез первый элемент задержки 13 и открывает второй р-п-р-транзистор 5. Начинает протекать ток в направлении А (сверху вниз) через резистор 7.

В связи с разделением во времени про- цесса закрывания открытых транзисторов (3 и б) от процесса открывания ранее закрытых транзисторов (5 и 4) при изменении уровня входного сигнала от логической 1 до логического О протекание сквозных токов че- рез транзисторы (5 и 6, 3 и 4) сведено к минимуму.

Таким образом, е сравнении с прототипом значение динамической мощности в выходном ключевом каскаде импульсного усилителя близко к нулю. Следовательно, в предложенном устройстве повышены КПД и его надежность. Кроме того, значительно снижен уровень помех, генерируемых по цепям питания.

Формула изобретения

Выходной ключевой каскад импульсного усилителя, содержащий первый и второй элементы НЕ, первый и второй р-п-р-тран- зисторы, первый и второй п-р-п-транзисто- ры, резистор, выход первого элемента НЕ соединен с базой второго п-р-п-транзисто- ра, выход второго элемента НЕ соединен с базой первого p-n-p-транзистора, эмиттер

которого соединен с эмиттером второго р-п- р-транзистора и с положительной шиной питания, а коллектор второго p-n-p-транзистора соединен с коллектором второго n-p-n-транзистора и с первым выводом резистора, коллектор первого р-п-р- транзистора соединен с коллектором первого n-p-n-транзистора и со вторым выводом резистора, эмиттер первого п-р-п- транзистора соединен с эмиттером второго n-p-n-транзистора и с общим проводом, о т- личающийся тем, что, с целью повышения надежности работы, введены третий элемент НЕ,первый и второй элементы И- НЕ, первый и второй элементы ИЛИ-ИЕ, первый, второй, третий, четвертый элементы задержки, вход третьего элемента НЕ соединен со входной шиной, а также со вторым входом второго элемента И-НЕ и вторым входом второго элемента ИЛИ-НЕ, выход третьего элемента НЕ соединен с первым входом первого элемента ИЛИ-НЕ, выход первого элемента И-НЕ соединен через первый элемент задержки с базой второго p-n-p-транзистора и с первым входом второго элемента И-НЕ, выход которого через второй элемент задержки соединен со вторым входом первого элемента И-НЕ и входом первого элемента НЕ, выход первого элемента ИЛИ-НЕ через третий элемент задержки соединен с входом второго элемента ИЛИ-НЕ, выход которого соединен через четвертый элемент задержки с базой первого п-р-п-транзистора

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| Транзисторно-транзисторный инвертор | 1989 |

|

SU1651372A1 |

| Преобразователь логического уровня | 1979 |

|

SU786006A1 |

| Устройство задержки | 1989 |

|

SU1793535A1 |

| Устройство согласования логических элементов с линией задержки | 1983 |

|

SU1152081A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| Формирователь сигналов | 1982 |

|

SU1020985A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| Одноразрядный сумматор | 1988 |

|

SU1599854A1 |

| Устройство согласования | 1983 |

|

SU1138942A1 |

Использование: в электронике, в частности в выходных каскадах микросхем. Сущность изобретения. Устройство содержит: элементы НЕ /1.2,8/, транзисторы р-п- р-типа /3,5/, транзисторы п-р-п-типа /4,6/, резистор /7/, элементы И-НЕ /9,10/. элементы ИЛИ-НЕ /11.12/, элементы задержки /13 - 16/. выходную шину /17/. 1 ил.

| Гольденберг Л.М | |||

| Импульсные и цифровые устройства | |||

| М.: Связь, 1973 | |||

| с.496 | |||

| Жаров А., Колобов Б, Индивидуальный дозиметр | |||

| - Юный техник, 1990 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

Авторы

Даты

1992-08-30—Публикация

1990-06-18—Подача