r, 4 «T3sj|,eiC i S йт а-1я Ai Aasja je-iA i

(21Г4890810/24 1(22)19.10.90

(46) 30.09.92. Бюл. №36 (72) И.Ё.Анкудинов, А.М.Зыков, С.А.Удинцев

vV Ч.ЙЙядш0-,- (56) Авторское свидетельство СССР .- № 1Б32Ш, F 7/72Г1988.

)r.tir.t.. .й Х WX

вторское свидетельство СССР 16978, , 1988; СвТорскоё свидетельство СССР клГб Об F7/49; 1988: ) СУММАТОР ПО МОДУЛЮ ПЯТЬ

Vvft & ч - -г if

20 з

Т

З&к: ««Cj-i,,--

..,,.л..2,,.

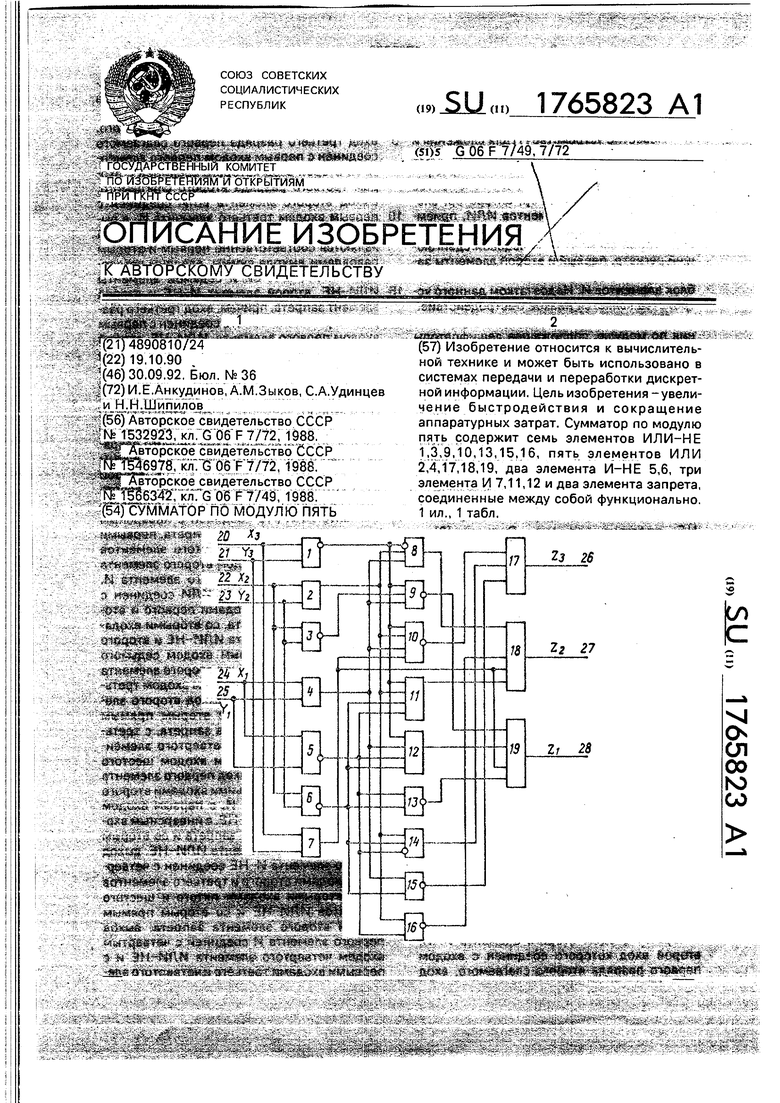

(57) Изобретение относится к вычислительной технике и может быть использовано в системах передачи и переработки дискретной информации. Цель изобретения -увеличение быстродействия и сокращение аппаратурных затрат. Сумматор по модулю пять содержит семь элементов ИЛИ-НЕ 1,3,9,10,13,15,16, пять элементов ИЛИ 2,4,17,18,19, два элемента И-НЕ 5,6, три элемента И 7,11,12 и два элемента запрета, соединенные между собой функционально. 1 ил., 1 табл.

j.uia.urii;- .&

с

/7

Zj 25

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной структуры | 1988 |

|

SU1573456A1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2012038C1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2018931C1 |

| Сумматор по модулю пять | 1988 |

|

SU1566342A1 |

| Устройство для формирования остатка по модулю | 1989 |

|

SU1736006A1 |

| Сумматор по модулю пять | 1991 |

|

SU1803911A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797110A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Сумматор по модулю пять | 1989 |

|

SU1658142A1 |

Мiri .

2J Уг

ЁГ

Oj

«пц ЧИвМйГ

J. - j- ггГ Z:. - .,

Ј J

ЈAMJi.

-ft-Јra«i - ее ,.4.4.

#i

И 1

йCO

АI

Я

2г г

/7

И

0

J

/5

Zt 28

VJ о

СЛ 00 Ю CA

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и переработки дискретной информации.

Известно устройство сложения и вычитания чисел по модулю, содержащее первый дешифратор, вычитатель, первый и второй блоки элементов И, блок элементов ИЛИ, второй дешифратор, шифратор, элемент ИЛИ, группу элементов ИЛИ, приемный регистр, первый элемент И, элемент НЕ, второй элемент И, кольцевой сдвигающий регистр, первый и второй элементы запрета, схему сравнения, счетчик и третий блок элементов И. Недостатком данного устройства является низкое быстродействие.

Известно также устройство 2 сложения по модулю, содержащее дешифраторы младших и старших разрядов, матрицу элементов И, дешифратор квадранта, блок элементов ИЛИ, группу шифраторов, коммутатор. Низкое быстродействие данного устройства обусловливается большой логической глубиной его схемы.

Наиболее близким по технической сущности к предлагаемому изобретению является выбранный в качестве прототипа сумматор 3 по модулю пять, содержащий восемь элементов ИЛИ, пятнадцать элементов И, элемент И-НЕ, три элемента ИЛИ- НЕ, элемент запрета. Сумматор 3 обеспечивает сложение исходных трехразрядных операндов по модулю пять.

Недостатками прототипа являются его низкое быстродействие и высокие аппаратурные затраты. Логическая глубина схемы составляет пять вентилей (G0-5). Общее количество элементов в схеме равно Млэо 28. Количество элементовходов по Квайну составляет Зкво 68.

Таким образом, низкое быстродействие прототипа обусловлено большой логической глубиной его схемы.

Цель изобретения - повышение быстродействия сумматора по модулю пять за счет уменьшения логической глубины его схемы и сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в сумматор по модулю пять, содержащий первый, второй, третий, четвертый и пятый элементы ИЛИ, первый, второй и третий элементы И, первый, второй и третий элементы ИЛ И-НЕ, первый элемент И-НЕ, первый элемент запрета, входы первого и второго трехразрядных слагаемых и трехразрядный выход суммы, причем вход первого разряда первого слагаемого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с входом первого разряда второго слагаемого, вход

второго разряда первого слагаемого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с входом второго разряда второго слагаемого, вход третьего разряда первого слагаемого соединен с первым входом первого элемента И, второй вход которого соединен с входом третьего разряда второго слагаемого, выход второго элемента ИЛИ соединен с

0 первым входом третьего элемента И, а выходы третьего и четвертого элементов ИЛИ являются соответственно первым и вторым разрядами выхода суммы, введены четвертый, пятый, шестой и седьмой элементы

5 ИЛИ-НЕ, второй элемент И-НЕ и второй элемент запрета, причем, вход третьего разряда первого слагаемого соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с входом третьего

0 разряда второго слагаемого, вход второго разряда первого слагаемого соединен с первыми входами второго элемента ИЛИ- НЕ и второго элемента И-НЕ, вторые входы которых соединены с входом второго разря5 да второго слагаемого, вход первого разряда первого слагаемого соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с входом первого разряда второго слагаемого, выход первого

0 элемента ИЛИ-НЕ соединен с инверсным входом первого элемента запрета, первыми входами третьего и четвертого элементов ИЛИ-НЕ, первым входом второго элемента И и вторым входом третьего элемента И,

5 выход первого элемента ИЛИ соединен с первыми прямыми входами первого и второго элементов запрета, со вторыми входами четвертого элемента ИЛИ-НЕ и второго элемента И и с первым входом седьмого

0 элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен со вторым входом третьего элемента ИЛИ-НЕ, выход второго элемента ИЛИ соединен с вторым прямым входом первого элемента запрета, с треть5 им входами третьего и четвертого элементов ИЛИ-НЕ и с первым входом шестого элемента ИЛИ-НЕ, выход первого элемента И-НЕ соединен с третьими входами второго и третьего элементов И, с первым входом

0 пятого элемента ИЛИ-НЕ, с инверсным входом второго элемента запрета и со вторым входом седьмого элемента ИЛИ-НЕ, выход второго элемента И-НЕ соединен с четвертыми входами второго и третьего элементов

5 И, со вторыми входами пятого и шестого элементов ИЛИ-НЕ и со вторым прямым входом второго элемента запрета, выход первого элемента И соединен с четвертым входом четвертого элемента ИЛИ-НЕ и с первыми входами третьего и четвертого 1 - %sЈiM S W««JEik:W ;- « W - - - sli s- ;SJ V: l- --:-:.:-::.vWiSj; ;v-Q:|: ;K-.f; iae«JaS S BSi3t эл-, iл У 1 аШШ ЙМааШ;м аУ| йШаШаа& v J,.

ментов ИЛИ, выход первого элемента за- ИЛИ 4. Выходы пятого 17, четвертого 18 и

v. V i -W -Ј & v f Ј %Ј«a e 4«i« .-..«im. - -- ,.. ..„.....---л™.-f w

прШ) соедйн ЖШтдатао оТгГчётвёрто- го эЖмёнтё ИЛИ, третий вход которого Кьмог элёмента Ё ход треТье1гр элемента ЙЛИ- р Щс динен со вторым входом третьего ;;,У лшеЩаИЛИ, третий вход которого соеди- Ш(Щ ан н йв со13о1 т|5ё Ш ЖШе1нта И, выход

.. -.--У; : 1 ДШ; ± а - №Ат | i - -.. - - - - --г-. .Г

е ШртОгЬ ШШёйта ИЛИ-НЕ соединен с

вц рои вход которого соединен с выходом втотретьего Ту элементов ИЛИ являются соот- ветственнр выхрдами третьего 26, второго 27 и. первого разряда суммы. Вход 20 третьего разряда первого слагаемого соединен с первым вхбдом первого элемента ИЛИ-НЕ 1ивхрд 21 третьего разряда второго слагаемого - с вторым входом первого элемента ИЛИ-НЕ 1, вход 22 второго разряда первого

ЙЯоТ 11 т1бТй э11емент аil/ШИ, вто- 10 сл гаемого - с первым входами второго

элемента ИЛЙ-НЕ 3 и второго элемента

jWW(-- 2 i Ј a « «bi№« ,.-. Ya-1; ir- у

Щ «Ш Й емеьгрГЗапрета, выход второгоИ-НЕ 6, ко вторым входам которых подI i S -MrtSSEESLl fflilSii. 2Ј15еРтым ВХ°Д°Мк™чен вход 23 второго разряда второго

;г |Щ ртоТо Ш1м тТ ИлИ, выход пятогослагаемого. Вход 24 первого разряда первос четвертым 15 гр слагаемого соединен с первым входом

;|| M g rpfrfer5 eWRTa ЙЛ1/Г выход шее-первого элемента И-НЕ 5, ко второму входу

I S llJ -HE9Pe eHc третьим ., , ..( |мента- ИлИ| выход кото

ттт г&т щ тхбяа m& -m mwfbr т: Сравнение с прототипом показывает,

20

второму входу

которого подключен;вхбд 25 первого разряда второго слагаемргр Вь1хрд первого эле- мента ..веРсным входом элемента запрета 8, с пер- выми ходами третьего 9 и четвертого 10 I M B Jt -R Taji1кжвс пз Р вы ми вхо- дамй втррогр If и третьего элементов И. ьГхрд г1ервргрэлемента 1 Л с

между эле

н fTWи TfeWEr т о р 17 ai т aIK ж е | Р ШШ е е1лёШНтШИ71Й-Н Е, tf Элементаi И-ИЕ, элемента запрета. Следоif-JJftj S l iSo i tessMaaK™ ---- . -

т вательно, заявляемый сумматор по модулю

изобретения

.jAb MftiiK.AiUiiM ii i... ... ,- ,...-- .-.-.. -

йя новизна.

Использование указанных выше эле- Мён1 бв й 5ЧТзей обусловливает появление

йдаШКЙ ЙЖЙйЛЯЙ 8 - ---- -....---.,.,., - -.-,. .

новых свойств, приводящих к повышению быстродействия сумматора по модулю пять. Это позволяет сделать вывод о соответстaf -

30

первым прямым входом первого элемента запрета 8, с вторым входом четвертого элемента ИЛЙ-НЁ 10, вторым входом второго элемента И 11, с первым прямым входом второго элемента запрета 14 и с первым входом седьмого элемента ИЛИ-НЕ 16. Выход второго элемента ИЛЙ-НЕ 3 соединен со вторым входом третьего элемента ИЛИ- НЕ 9. Выход второго элемента ИЛ И 4 соединен с вторым прямым входом первого

«. элемента запрета 8, с третьим входом третьйю существенные отличия.

эд| JHa epTexe представлена схема сумма- модул ю гТять.

45

его элемента ИЛИ-НЕ 9, с третьим входом четвертого элемента ИЛИ-НЕ 10, с вторым входом третьего элементаГ И Т21 иТе первым входом шестого элемента ИЛИ-НЕ 15. Выход второго элемента И-НЕ 6 соединен с четвертыми входами второго 11 и третьего 12 элементов И, с вторым прямым входом второго элемента запрета 14, с вторым входом пятого элемента ИЛИ-НЕ13 и с вторым входом шестого элемента ИЛИ-НЕ 15. Выход первого элемента Й-НЁ 5 соединен с третьими входами второго 11 и третьего 12

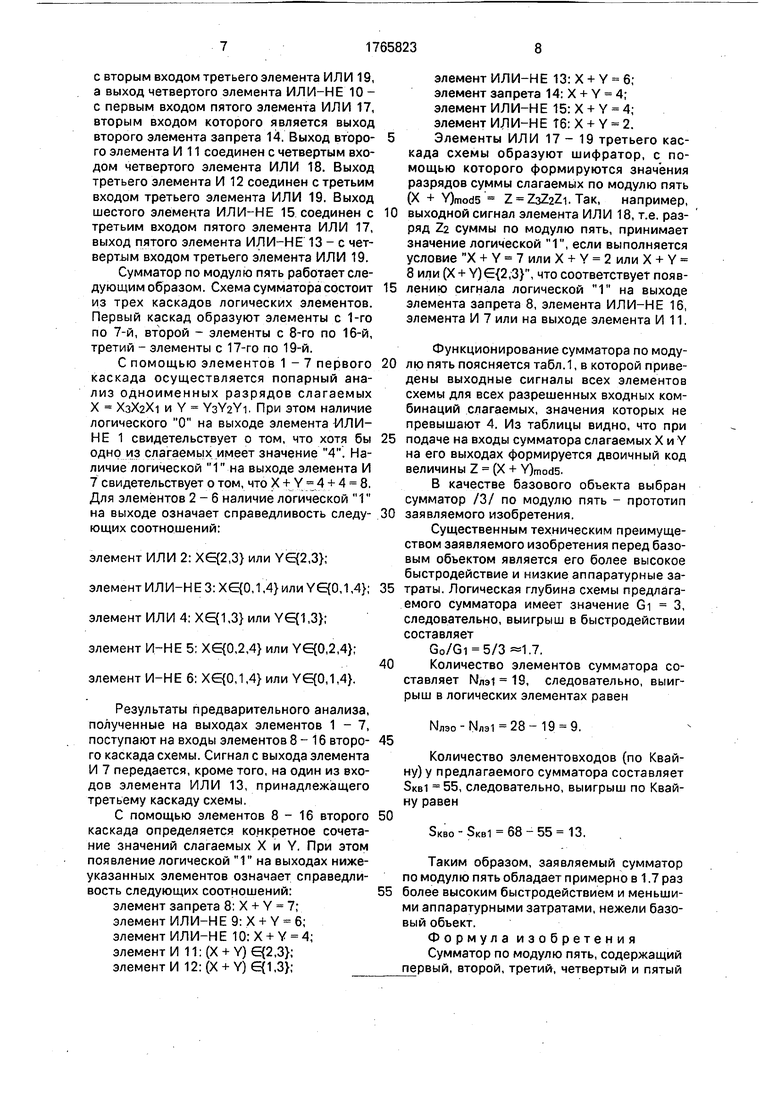

Сумматор по модулю пять содержит

-элШент ИЛИ-НЕ 1, элемент ИЛИ 2, эле- 40

-ЩЙт Й71 , элемент ЙЛИ 4, элементы

f Л, 3 .jVjftA. Ло 1г-Л А й1 ч -;к; -vbv-. .. ч,.-,. ,-,. -.-.- - - ...-. . ч...-.-.

/ И-НЕ 5 и 6, элемент И 7, элемент запрета 8, ШиеЖ ИШ-НЕТ и 10; элементы И 11 и ; 12, элемент Й Л И-НЁ 13, элемент запрета

14, элементьГИЛЙ7НЕ 15 и 16, элементы,

ИЛИ 17 18Т19 входы 20 - 25 разрядов опе р айдов ,)Щь1 2В -28 разрядов результаJ cJ-JHpn этом вход 20 третьего разряда элементов И, с первым входом седьмого nipt of б слагаеШТб соединён с пёрвымЪхб- элемента ЙЛ Й-НЁ 13, с инверсным входом

дЫСГгГе р вТог о1 л1емен та И 7, вход 21 третьего 50 второго элемента запрета 14 и с вторым . р а§ряда втс Ј Ъа ёШ1о с1тЪрым вхо- Ґ6дГм едгЖг

nepWfo эле(е1нта И 7, вход 22 второго ход первого элемента И 7 соединен с чет 4 fife5Ce 1 W itl4 -«S Ј Ј ii5iF%L -i; - -J 3 : - - -;------ -- 1 : з г4 аж-ч;-и-.-1-; ; ., 1 - -ла ь--ава«дк-..ч &&&ь 1&ъЬв&$ф.УЬ аЈ.ъ--.УЧ Д -ХЬ---.:.. - -... ра вдаТт рвог слатаемрго - с первым вхо- ртым входом четв1ртоге элемента i до ё оТ б ШШШта ЙТ1Й 2, вход 23 вто- ИЛЙ-НЁ: 10, первыми входами

-рого разря 1Щ 1 Шга%1 третьего элементов ИЛИ. входом первого элеме нта ИЛИ 2, вход 24 Выход первого элемента запрета 8 соеди- первого разряда первого слага мбгр йен с

пёрвы м в Ь 9м т рбТо э11емҐнт Й ИЛИ 18,третьим входом которого является

Шбд 25 первого разряда второго слагав- выход седьмого элемента ИЛИ-НЕ 16. Вы- Ъf S - fS Ж Щffoff Щi эneW§ нfa ход третьег 6 эл1мШт1 Ж1:: Н Е 9 соединен

гч,- . „ Л- „ -

v J. «V .

„ -V

,.tsg1765823

&

6

S W««JEik:W ;- « W - - - sli s- ;SJ V: l- --:-:..

ЭЙЙЙ|: . J ftii .;

л У 1 аШШ ЙМааШ;м аУ| йШаШаа& v J,.

а- ИЛИ 4. Выходы пятого 17, четвертого 18 и

,.. ..„.....---л™.-f w

третьего Ту элементов ИЛИ являются соот- ветственнр выхрдами третьего 26, второго 27 и. первого разряда суммы. Вход 20 третьего разряда первого слагаемого соединен с первым вхбдом первого элемента ИЛИ-НЕ 1ивхрд 21 третьего разряда второго слагаемого - с вторым входом первого элемента ИЛИ-НЕ 1, вход 22 второго разряда первого

сл гаемого - с первым входами второго

первого элемента И-НЕ 5, ко второму входу

второму входу

которого подключен;вхбд 25 первого разряда второго слагаемргр Вь1хрд первого эле- мента ..веРсным входом элемента запрета 8, с пер- выми ходами третьего 9 и четвертого 10 I M B Jt -R Taji1кжвс пз Р вы ми вхо- дамй втррогр If и третьего элементов И. ьГхрд г1ервргрэлемента 1 Л с

первым прямым входом первого элемента запрета 8, с вторым входом четвертого элемента ИЛЙ-НЁ 10, вторым входом второго элемента И 11, с первым прямым входом второго элемента запрета 14 и с первым входом седьмого элемента ИЛИ-НЕ 16. Выход второго элемента ИЛЙ-НЕ 3 соединен со вторым входом третьего элемента ИЛИ- НЕ 9. Выход второго элемента ИЛ И 4 соединен с вторым прямым входом первого

элемента запрета 8, с третьим входом треть

его элемента ИЛИ-НЕ 9, с третьим входом четвертого элемента ИЛИ-НЕ 10, с вторым входом третьего элементаГ И Т21 иТе первым входом шестого элемента ИЛИ-НЕ 15. Выход второго элемента И-НЕ 6 соединен с четвертыми входами второго 11 и третьего 12 элементов И, с вторым прямым входом второго элемента запрета 14, с вторым входом пятого элемента ИЛИ-НЕ13 и с вторым входом шестого элемента ИЛИ-НЕ 15. Выход первого элемента Й-НЁ 5 соединен с третьими входами второго 11 и третьего 12

элементов И, с первым входом седьмого элемента ЙЛ Й-НЁ 13, с инверсным входом

с вторым входом третьего элемента ИЛИ 19, а выход четвертого элемента ИЛИ-НЕ 10 - с первым входом пятого элемента ИЛИ 17, вторым входом которого является выход второго элемента запрета 14. Выход второ- го элемента И 11 соединен с четвертым входом четвертого элемента ИЛИ 18. Выход третьего элемента И 12 соединен с третьим входом третьего элемента ИЛИ 19. Выход шестого элемента ИЛИ-НЕ 15 соединен с третьим входом пятого элемента ИЛИ 17, выход пятого элемента ИЛИ-НЕ 13 - с четвертым входом третьего элемента ИЛИ 19.

Сумматор по модулю пять работает следующим образом. Схема сумматора состоит из трех каскадов логических элементов. Первый каскад образуют элементы с 1-го по 7-й, второй - элементы с 8-го по 16-й, третий - элементы с 17-го по 19-й.

С помощью элементов 1 - 7 первого каскада осуществляется попарный анализ одноименных разрядов слагаемых X XaXaXi и Y YsYaYi. При этом наличие логического О на выходе элемента МЛИ- НЕ 1 свидетельствует о том, что хотя бы одно из слагаемых имеет значение 4. Наличие логической 1 на выходе элемента И 7 свидетельствует о том, что X + Y 4 + 4 8. Для элементов 2-6 наличие логической 1 на выходе означает справедливость следу- ющих соотношений:

элемент ИЛИ 2: ,3} или YE{2,3}; элемент ИЛИ-НЕ 3:XG{0,1,4} или YE{0,1,4}; элемент ИЛИ 4: X 6(1,3} или Y 6(1,3}; элемент И-НЕ 5: X 6(0,2,4} или Y 6(0,2,4};

элемент И-НЕ 6: X 6(0,1,4} или Y 6(0,1,4}.

Результаты предварительного анализа, полученные на выходах элементов 1 - 7, поступают на входы элементов 8-16 второ- го каскада схемы. Сигнал с выхода элемента И 7 передается, кроме того, на один из входов элемента ИЛИ 13, принадлежащего третьему каскаду схемы.

С помощью элементов 8-16 второго каскада определяется конкретное сочетание значений слагаемых X и Y. При этом появление логической 1 на выходах нижеуказанных элементов означает справедливость следующих соотношений:

элемент запрета 8: X + Y 7;

элемент ИЛИ-НЕ 9: X + Y 6;

элемент ИЛИ-НЕ 10: X + Y 4;

элемент И 11: (X + Y) 6(2,3};

элемент И 12: (X + Y) 6(1,3};

5 10

15

0 5 0

5

0

5

0 5

элемент ИЛИ-НЕ 13: X + Y 6;

элемент запрета 14: X + Y 4;

элемент ИЛИ-НЕ 15: X + Y 4;

элемент ИЛИ-НЕ Т6: X + Y 2.

Элементы ИЛИ 17-19 третьего каскада схемы образуют шифратор, с помощью которого формируются значения разрядов суммы слагаемых по модулю пять (X + Y)mod5 Z ZsZ2Zi. Так, например, выходной сигнал элемента ИЛИ 18, т.е. разряд Z2 суммы по модулю пять, принимает значение логической 1, если выполняется условие X + Y 7 или X + Y 2 или X + Y 8 или (X + Y)6{2,3}, что соответствует появлению сигнала логической 1 на выходе элемента запрета 8, элемента ИЛИ-НЕ 16, элемента И 7 или на выходе элемента И 11.

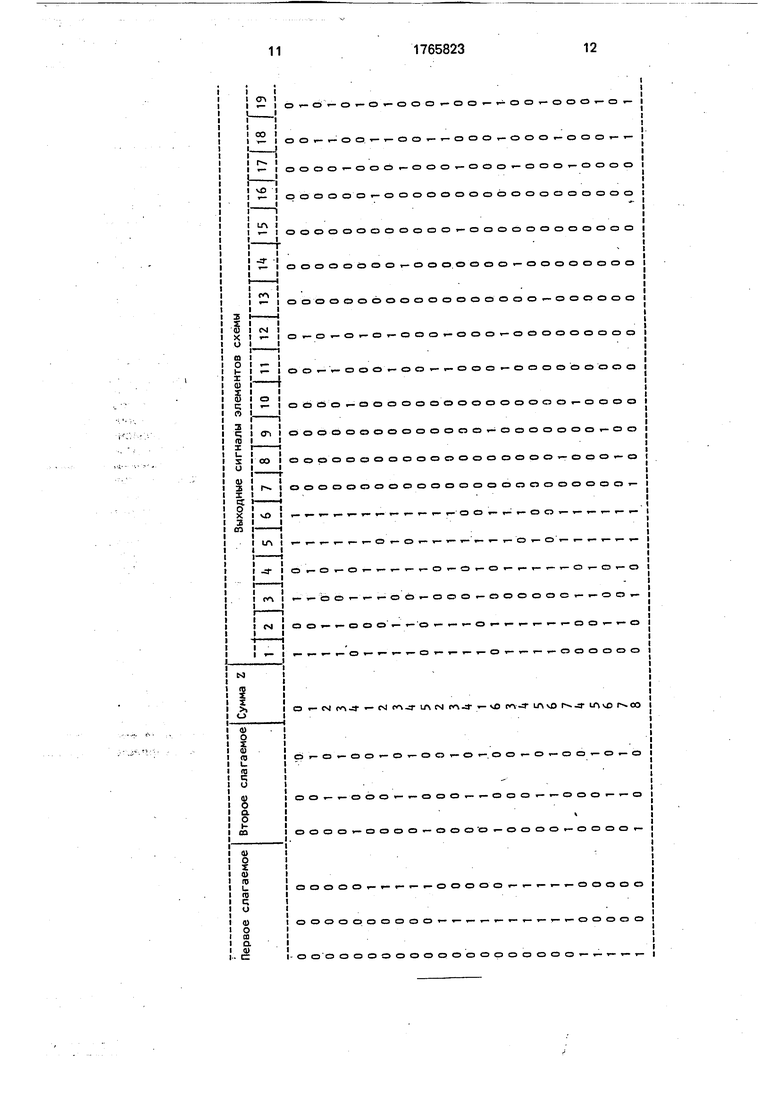

Функционирование сумматора по модулю пять поясняется табл.1, в которой приведены выходные сигналы всех элементов схемы для всех разрешенных входных комбинаций слагаемых, значения которых не превышают 4. Из таблицы видно, что при подаче на входы сумматора слагаемых X и Y на его выходах формируется двоичный код величины Z (X + Y)mod5.

В качестве базового объекта выбран сумматор /3/ по модулю пять - прототип заявляемого изобретения.

Существенным техническим преимуществом заявляемого изобретения перед базовым объектом является его более высокое быстродействие и низкие аппаратурные затраты. Логическая глубина схемы предлагаемого сумматора имеет значение GI 3, следовательно, выигрыш в быстродействии составляет

G0/Gi .7.

Количество элементов сумматора составляет Млэ1 19, следовательно, выигрыш в логических элементах равен

МЛЭо-Млэ1 28-19 9.

Количество элементовходов (по Квай- ну) у предлагаемого сумматора составляет 5кв1 55, следовательно, выигрыш по Квай- ну равен

Зкво - SKB1 68 - 55 13.

Таким образом, заявляемый сумматор по модулю пять обладает примерно в 1.7 раз более высоким быстродействием и меньшими аппаратурными затратами, нежели базовый объект.

Формула изобретения Сумматор по модулю пять, содержащий первый, второй, третий, четвертый и пятый

элементы ИЛИ, первый, второй и третий элементы И, первый, второй и третий элементы ИЛИ-НЕ, первый элемент И-НЕ, первый элемент запрета, входы первого и второго сЖг Шых трёх- 5 разрядный суммы причем вход первого разр йд1ГШрвВг6 слагаемогсГсоеданен с4 ЁКодбм втррого элемента ИЛИ,

второй вход которого соединен г ИзхЪдом первого р а зряда второго слагаемого, вход 10

Гвтор г р зШ Р 0 2 0 0 пеЭвымЛзХодом первого элемента

уШИ, второй вход которого соединен с входом BTdplbro разряда второго слагаемого, вход третьего разряда первого слагаемого 15 соединен Ь первым входом первого элемента И, второй вход которого соединен с вхо- Жм т 1- аШЩа тШ)гЪ сЯ1гаемог5: 1 BlJxbft BflJporo элемента ИЛИ соединен с первым вадш ть-ёГо элемента И, з ьы- 20 ходы т ёт6егб и четвертого элементов ИЛИ являТо я б т1ётств15 нно первым и вторым разр а м 1&Гх дав18Умм ыГо тличающий- с я , с цёлГью увеличения быстродей- Мвия и сокращения аппаратурных затрат, в 25 не о йвеШн й че тв ертый, пятый, и-естой и седьмой элементы ИЛИ-НЕ, второй элемент И-НЕ и вторЪ й элемект запрета, при- че м в х од Гретьего разряда первого слагаёмо1Ро динекГс пёр вь1м §х6дом пер - 30 вого эле меьта Ш1И-НЕ, второй вход которой ё %Щвм третьего разряда второго firfafaeMoro, вход второго разряда первого Слагаемого соединен с первыми входами Што рого элемента ИЛИ-НЕ и вто- 35 рого элемента И-НЕ, вторые входы которых сОёДиненТ входом второго разряда второ- оГслагаеЙпгТэ, вход первого разряда первого сла га ё 5 6 сЫйй н н с первый входом пЪрвЪ1г1:Гэлегм1 нта И-НЕ, второй вход кото- 40 рого соединен с входом перэого разряда второго с лаг15емргЪ, выход первого элемента И Л И-НЁ соединён с инверсным входом первогоТ лёмента запрета, пераыми входами третьего и четвертого элементов ИЛИ- 45

НЕ, первым входом второго элемента И ч

- -$ А 4s & № -« $1 ,о

f

ff

t

Ь s f& $5 t « Й SS, О

/

.JZ & C Cj

1 XSl 4S- «3 Э {-«I

J S -«& да -fe s, «: «X -4 « -M.

fГ

- « - «) sp r$ & И j0 a

V

v

-

вторым входом третьего элемента И, выход первого элемента ИЛИ соединен с первыми прямыми входами первого и второго элементов запрета, с вторТямй входами четвертого ИЛИ-НЕ и второго элемента И и с первым входом седьмого элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с вторым входом третьего элемента ИЛИ-НЕ, выход второго элемента ИЛИ соединен с вторым прямым входом первого эле мейта запрету с третьими входами третьего и четвертого элементов ИЛИ-НЕ и с первым входом шестого элемента ИЛИ- МЕ, выход первого элемента И-НЕ соединен с третьими входами второго и третьего элементов И, с первым входом пятого элемента ИЛИ-НЕ, с инверсным входом второго запрета1 vf € вторым входом седьмого элемента , выход второго элемента И-НЕ соединен с четвертыми входами второго и третьего элементов И, с вторыми входами пятого wJuiecToro элементов ИЛИ-НЕ и с вторым прямым входом второго элемента запрета, выход первого элемента И соединен с четвертым входом четвертого элемента ИЛИ-НЕ м с первыми входами третьего и четвертого элементов ИЛИ, зычод первого элемента запрета соединен вторым БХО/ЮМ четвертого элемента ИЛИ, третий вход -оторого соединен с выходом седьмого эг,емента ИЛИ-НЕ, выход третьего элемента ЙТМ-НЕ соединен с вторым входом трче- ьего Элемента ИЛИ, третий вход которого сое дине н с выходом третьего элемента И, выход четвертого элемента ИЛИ-НЕ соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом второго элемента запрета, выход второго элемента И соединен с четвертым входом четвертого элемента ИЛИ, выход пятого элемента ИЛИ-НЕ соединен с четвертым входом третьего элемента ИЛИ, выход шестого элемента ИЛИ-НЕ соединен с третьим входов пятого элемента ИЛИ, выход которочэ является третьим разрядом вухода сумматора по модулю пять

I

r

лз

Авторы

Даты

1992-09-30—Публикация

1990-10-19—Подача