высокого приоритета. Устройство-для формирования сигналов прерываний содержит регистр 1 прерьюаний, регистр 2 кода периферийного устройства, п элементов 3 запрета (п - число запросных входов устройства), п-1 элементов ИЛИ 4, мультиплексор 5, генератор 6 импульсов, первый - третий триггеры 7-9, дешифратор tO, приори1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании вычислительных систем.

Цель изобретения - повышение быстродействия устройства.

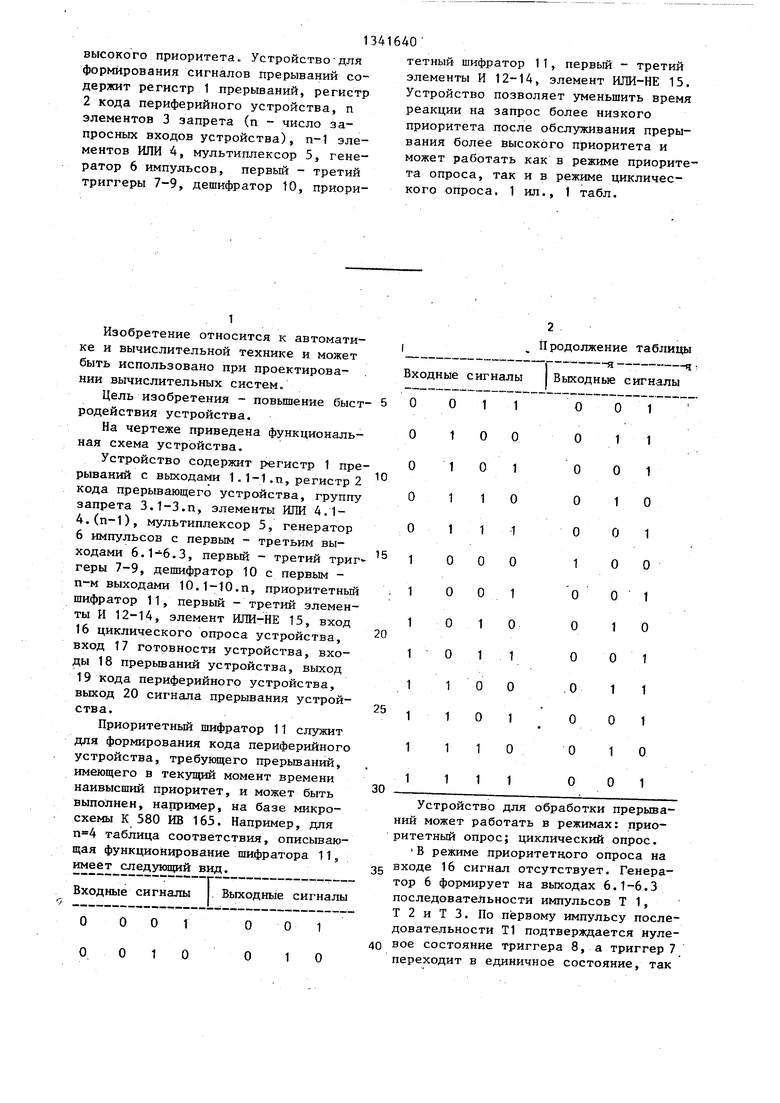

На чертеже приведена функционгшь- ная схема устройства.

Устройство содержит регистр 1 прерываний с выходами 1.1-1.п, регистр 2 кода прерывающего устройства, группу запрета 3.1-З.п, элементы ИЛИ 4.1- 4.(п-1), мультиплексор 5, генератор 6 импульсов с первым - третьим выходами 6..3, первый - третий триггеры 7-9, дешифратор 10 с первым - п-м выходами 10.1-IO.n, приоритетный шифратор 11, первый - третий элементы И 12-14, элемент ИЛИ-НЕ 15, вход 16 циклического опроса устройства, вход 17 готовности устройства, входы 18 прерьшаний устройства, выход 19 кода периферийного устройства, выход 20 сигнала прерывания устройства.

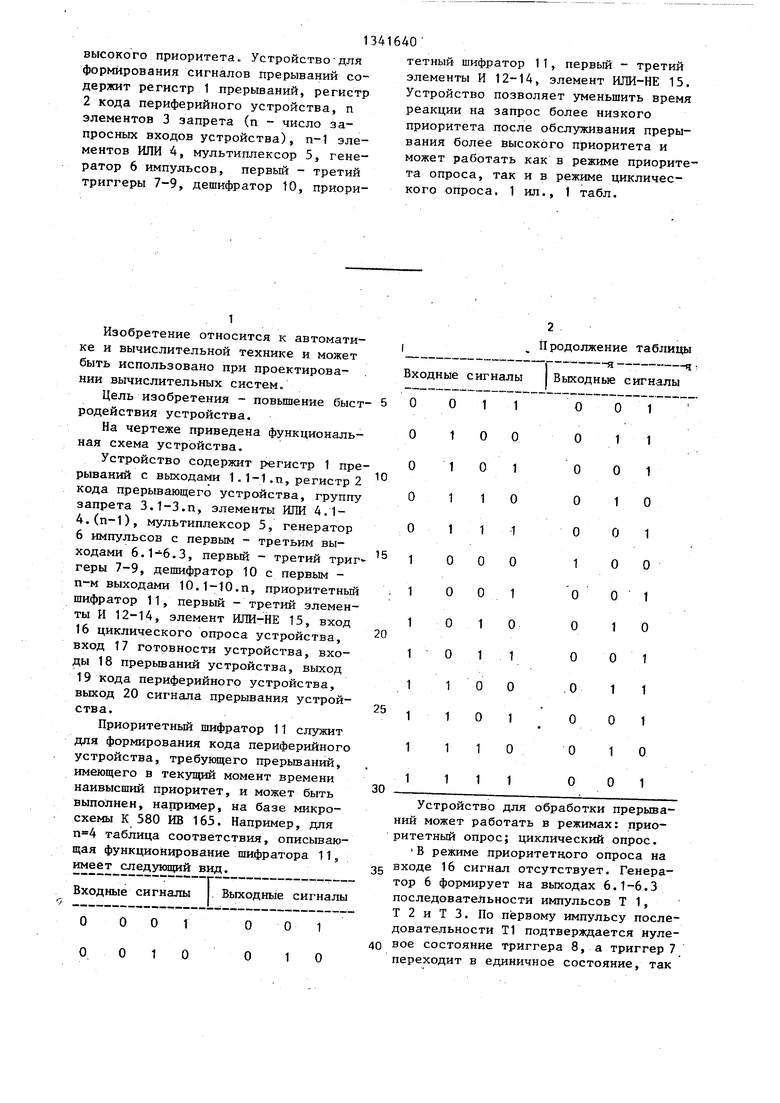

Приоритетньш шифратор 11 служит для формирования кода периферийного устройства, требующего прерьшаний, имеющего в текущий момент времени наивысший приоритет, и может быть выполнен, например, на базе микросхемы К 580 ИВ 165. Например, для таблица соответствия, описывающая функционирование шифратора 11 имеет следующий вид.

Входные сигналы О 001

1. Выходные сигналы

О 1

О

О 1

О

1 О

тетный шифратор 11, первый - третий элементы И 12-14, элемент ИЛИ-НЕ 15, Устройство позволяет уменьшить время реакции на запрос более низкого приоритета после обслуживания прерывания более высокого приоритета и может работать как в режиме приоритета опроса, так и в режиме циклического опроса, 1 ил., 1 табл.

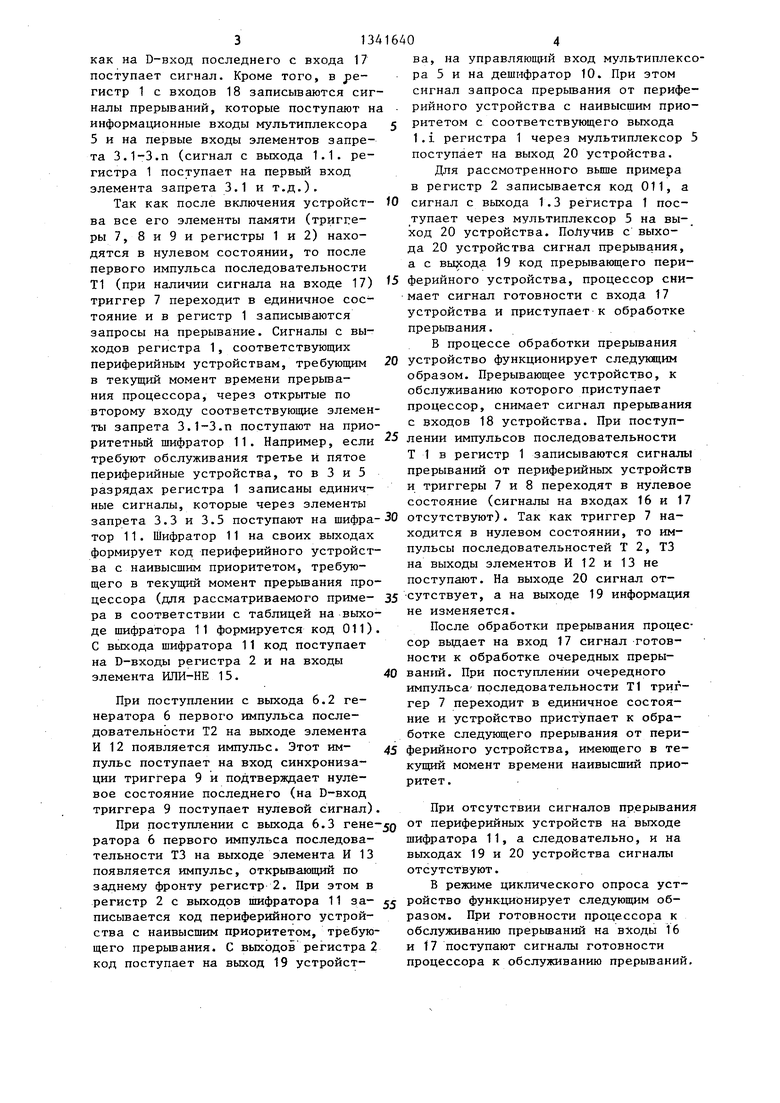

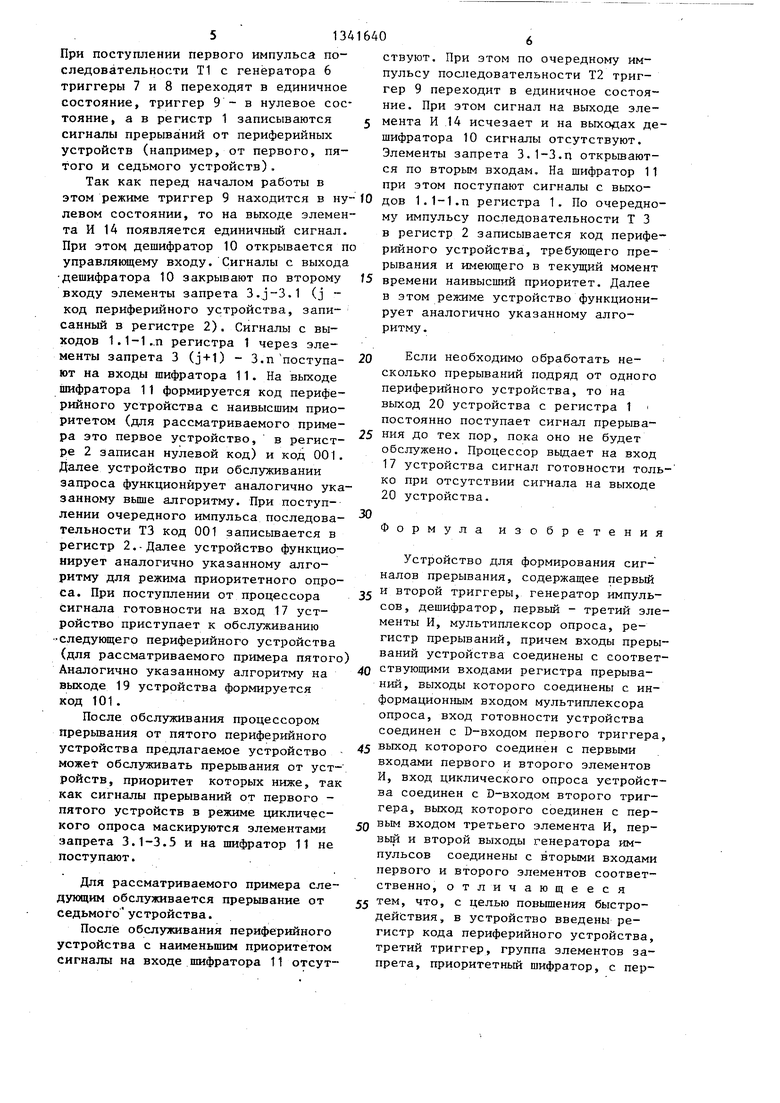

Продолжение таблицы

д q .

Входные сигналы Выходные сигналы

Устройство для обработки прерьшаний может работать в режимах: приоритетный опрос; циклический опрос. В режиме приоритетного опроса на

входе 16 сигнал отсутствует. Генератор 6 формирует на выходах 6.1-6.3 последовательности импульсов Т 1, Т 2 и Т 3. По первому импульсу последовательности Т1 подтверждается нулевое состояние триггера 8, а триггер 7 переходит в единичное состояние, так

как на D-вход последнего с входа 17 поступает сигнал. Кроме того, в регистр 1 с входов 18 записываются сигналы прерываний, которые поступают н информационные входы мультиплексора 5 и на первые входы элементов запрета 3.1-З.п (сигнал с выхода 1.1. регистра 1 поступает на первьш вход элемента запрета 3.1 и т.д.).

Так как после включения устройства все его элементы памяти (триггеры 7, 8 и 9 и регистры 1 и 2) находятся в нулевом состоянии, то после первого импульса последовательности Т1 (при наличии сигнала на входе 17) триггер 7 переходит в единичное состояние и в регистр 1 записываются запросы на прерывание. Сигналы с выходов регистра 1, соответствующих периферийным устройствам, требующим в текущий момент времени прерьша- ния процессора, через открытые по второму входу соответствующие элементы запрета 3.1-З.п поступают на приоритетный шифратор 11. Например, если требуют обслуживания третье и пятое периферийные устройства, то в 3 и 5 разрядах регистра 1 записаны единичные сигналы, которые через элементы

запрета 3.3 и 3.5 поступают на шифра-30 отсутствуют). Так как триггер 7 тор 11. Шифратор 11 на своих выходах формирует код периферийного устройства с наивысшим приоритетом, требующего в текущий момент прерьшания проВ процессе обработки прерывания устройство функционирует следующим образом. Прерывающее устройство, к обслз иванию которого приступает процессор, снимает сигнал прерывания с входов 18 устройства. При поступлении импульсов последовательности Т 1 в регистр 1 записываются сигналы прерываний от периферийных устройств и триггеры 7 и 8 переходят в нулевое состояние (сигналы на входах 16 и 17

находится в нулевом состоянии, то импульсы последовательностей Т 2, ТЗ на выходы элементов И 12 и 13 не поступают. На выходе 20 сигнал отцессора (для рассматриваемого приме- 35 выходе 19 информация

ра в соответствии с таблицей на выходе шифратора 11 формируется код 011). С выхода шифратора 11 код поступает на D-входы регистра 2 и на входы элемента ИЛИ-НЕ 15.40

При поступлении с выхода 6.2 генератора 6 первого импульса последовательности Т2 на выходе элемента И 12 появляется импульс. Этот им- 5 пульс поступает на вход синхронизации триггера 9 и подтверждает нулевое состояние последнего (на D-вход триггера 9 поступает нулевой сигнал).

При цоступлении с выхода 6.3 гене- о ратора 6 первого импульса последовательности ТЗ на выходе элемента И 13 появляется импульс, открьшающий по заднему фронту регистр 2. При этом в регистр 2 с выходов шифратора 11 за- письшается код периферийного устройства с наивысшим приоритетом, требующего прерьшания. С выходов регистра 2 код поступает на выход 19 устройст55

O

0 отсутствуют). Так как триггер 7

ва, на управляющий вход мультиплексора 5 и на дешифратор 10. При этом сигнал запроса прерывания от периферийного устройства с наивысшим приоритетом с соответствующего выхода 1.i регистра 1 через мультиплексор 5 поступает на выход 20 устройства.

Для рассмотренного вьш1е примера в регистр 2 записьгоается код 011, а сигнал с выхода 1.3 регистра 1 поступает через мультиплексор 5 на выход 20 устройства. Получив с выхода 20 устройства сигнал прерывания, а с выхода 19 код прерывающего пери- 5 ферийного устройства, процессор снимает сигнал готовности с входа 17 устройства и приступает к обработке прерьшания.

В процессе обработки прерывания устройство функционирует следующим образом. Прерывающее устройство, к обслз иванию которого приступает процессор, снимает сигнал прерывания с входов 18 устройства. При поступлении импульсов последовательности Т 1 в регистр 1 записываются сигналы прерываний от периферийных устройств и триггеры 7 и 8 переходят в нулевое состояние (сигналы на входах 16 и 17

находится в нулевом состоянии, то импульсы последовательностей Т 2, ТЗ на выходы элементов И 12 и 13 не поступают. На выходе 20 сигнал от0

5

0

5

о

5

не изменяется.

После обработки прерывания процессор выдает на вход 17 сигнал готовности к обработке очередных прерываний. При поступлении очередного импульса- последовательности Т1 триггер 7 переходит в единичное состояние и устройство приступает к обработке следующего прерывания от периферийного устройства, имеющего в текущий момент времени наивысший приоритет .

При отсутствии сигналов прерывания от периферийных устройств на выходе шифратора 11, а следовательно, и на выходах 19 и 20 устройства сигналы отсутствуют.

В режиме циклического опроса устройство функционирует следующим образом. При готовности процессора к обслуживанию прерьшаний на входы 16 и 17 поступают сигналы готовности процессора к обслуживанию прерываний.

При поступлении первого импульса последовательности Т1 с генератора 6 триггеры 7 и 8 переходят в единичное состояние, триггер 9 - в нулевое состояние, а в регистр 1 записываются сигналы прерываний от периферийных устройств (например, от первого, пятого и седьмого устройств).

Так как перед началом работы в этом режиме триггер 9 находится в нулевом состоянии, то на выходе элемента И 14 появляется единичный сигнал. При этом дешифратор 10 открывается п управлянмцему входу. Сигналы с выхода дешифратора 10 закрывают по второму входу элементы запрета 3.J-3.1 (j код периферийного устройства, записанный в регистре 2). Сигналы с выходов 1.1-1..П регистра 1 через элементы запрета 3 (j + 1) - З.п поступают на входы шифратора 11. На выходе шифратора 11 формируется код периферийного устройства с наивысшим приоритетом (для рассматриваемого примера это первое устройство, в регистре 2 записан нулевой код) и код 001. Далее устройство при обслуживании запроса функционирует аналогично указанному Bbmie алгоритму. При поступлении очередного импульса последовательности ТЗ код 001 записьшается в регистр 2.-Далее устройство функционирует аналогично указанному алгоритму для режима приоритетного опроса. При поступлении от процессора Сигнала готовности на вход 17 устройство приступает к обслуживанию -следующего периферийного устройства (для рассматриваемого примера пятого Аналогично указанному алгоритму на выходе 19 устройства формируется код 101.

После обслуживания процессором прерьшания от пятого периферийного устройства предлагаемое устройство может обслуживать прерьшания от устройств, приоритет которых ниже, так как сигналы прерываний от первого - пятого устройств в режиме циклического опроса маскируются элементами запрета 3.1-3.5 и на шифратор 11 не поступают.

Для рассматриваемого примера следующим обслуживается прерывание от седьмого устройства.

После обслуживания периферийного устройства с наименьшим приоритетом сигналы на входе шифратора 11 отсуттвуют. При этом по очередному имульсу последовательности Т2 триггер 9 переходит в единичное состояние. При этом сигнал на выходе элеента И 14 исчезает и на выходах деифратора 10 сигналы отсутствуют. Элементы запрета 3.1-З.п открьшают- ся по вторым входам. На шифратор 11 при этом поступают сигналы с выходов 1.1-1.П регистра 1. По очередному импульсу последовательности Т 3 в регистр 2 записывается код периферийного устройства, требующего прерывания и имеющего в текущий момент

времени наивысший приоритет. Далее в этом режиме устройство функционирует аналогично указанному алгоритму.

Если необходимо обработать несколько прерываний подряд от одного периферийного устройства, то на выход 20 устройства с регистра 1 постоянно поступает сигнал прерываНИН до тех пор, пока оно не будет обслужено. Процессор вьщает на вход 17 устройства сигнал готовности только при отсутствии сигнала на выходе 20 устройства.

Формула изобретения

Устройство для формирования сигналов прерывания, содержащее первый

и второй триггеры, генератор импульсов , дешифратор, первый - третий элементы И, мультиплексор опроса, регистр прерываний, причем входы прерываний устройства соединены с соответствующими входами регистра прерываний, выходы которого соединены с информационным входом мультиплексора опроса, вход готовности устройства соединен с D-входом первого триггера,

выход которого соединен с первыми входами первого и второго элементов И, вход циклического опроса устройства соединен с D-входом второго триггера, выход которого соединен с первым входом третьего элемента И, первый и второй выходы генератора импульсов соединены с вторыми входами первого и второго элементов соответственно, отличающееся

тем, что, с целью повьш1ения быстродействия, в устройство введены регистр кода периферийного устройства, третий триггер, группа элементов запрета, приоритетный шифратор, с первого по (п-1)-й элементы ИЛИ (п - число запросов прерьшания), элемент ИЛИ-НЕ, причем третий выход генератора импульсов соединен с входами синхронизации регистра прерываний, первого и второго триггеров, R-BXO- дом третьего триггера, i-й выход регистра прерьшаний (,п) соединен с информационным входом i-ro элемента запрета группы, группа выходов которого соединена с группой входов приоритетного шифратора, группа выходов которого соединена с группой входов элемента ИЛИ-НЕ и с группой информационных входов регистра кода периферийного устройства, группа выходов которого соединена с группой выходов кода периферийного устройства и с группой информационных входов дешифратора, j-й выход которого (,(n-1)20 регистра прерываний соединена с соединен с первым входом j-ro элемен- группой информационных входов мульти- та ИЖ, выход первого элемента ИЛИ плексора, группа кодовых входов ко- соединен с управляющим иродом первого торого соединена с группой выходов элемента запрета группы, выход К-го регистра кода периферийного устрой- элемента ИЛИ (,(п-1)) соединен с ства.

416408

вторым входом (К-1)-го элемента ИЛИ и с управляющим входом К-го элемента запрета группы, п-й выход дешифрато- - ра соединен с вторым входом (n-l)-ro

5 элемента ИЛИ и с управляющим входом п-го элемента запрета группы, выход первого элемента И соединен с входом синхронизации третьего триггера, выход второго элемента И соединен с вхо10 дом синхронизации регистра кода периферийного устройства,выход элемента ИЛИ-НЕ соединен с D-входом третьего триггера, инверсный выход которого соединен с вторым входом третьего

15 элемента И, выход третьего элемента И соединен с управляющим входом дешифратора, выход мультиплексора опроса является выходом сигнала прерьшания устройства, группа выходов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки прерываний | 1986 |

|

SU1606975A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для сопряжения группы процессоров с группой внешних устройств | 1988 |

|

SU1599865A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для программного управления | 1985 |

|

SU1267362A2 |

| Устройство прерывания | 1982 |

|

SU1084795A1 |

Изобретение относится к автома-, тике и вычислительной технике и может быть использовано при проектировании вычислительных систем. Цель изобретения - повьшение быстродействия путем уменьшения времени реакции на запрос более низкого приоритета после обслуживания прерьшания более -o20 с (Л 00 4 05 4

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Устройство для обработки прерываний | 1983 |

|

SU1142836A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-30—Публикация

1986-03-03—Подача