vj

о VJ VI о о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кода | 1988 |

|

SU1713105A1 |

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| Преобразователь кодов | 1986 |

|

SU1578813A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU922723A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1984 |

|

SU1203711A1 |

Изобретение относится к вычислительной технике, может найти применение в системах хранения и передачи информации и может быть использовано для преобразования двоичного кода в непозиционный (р,к)- код Фибоначчи. Оно позволяет расширить функциональные возможности за счет преобразования двоичного кода в непозиционный (р,к)-код Фибоначчи. Преобразователь содержит первый и второй сдвиговые регистры 1 и 2, первый и второй элементы ИЛИ 5 и 4, элемент ИЛИ-НЕ 3 и элемент 6 запрета. 2 ил. (Л С

Фиг.

Изобретение относится к вычислительной технике и может быть использовано для преобразования двоичного кода в непозиционный (р,к)-код Фибоначчи, а также может найти применение в системах хранения и передачи информации.

Цель изобретения - расширение функциональных возможностей за счет преобразования двоичного кода в непозиционный (р,к)-код Фибоначчи.

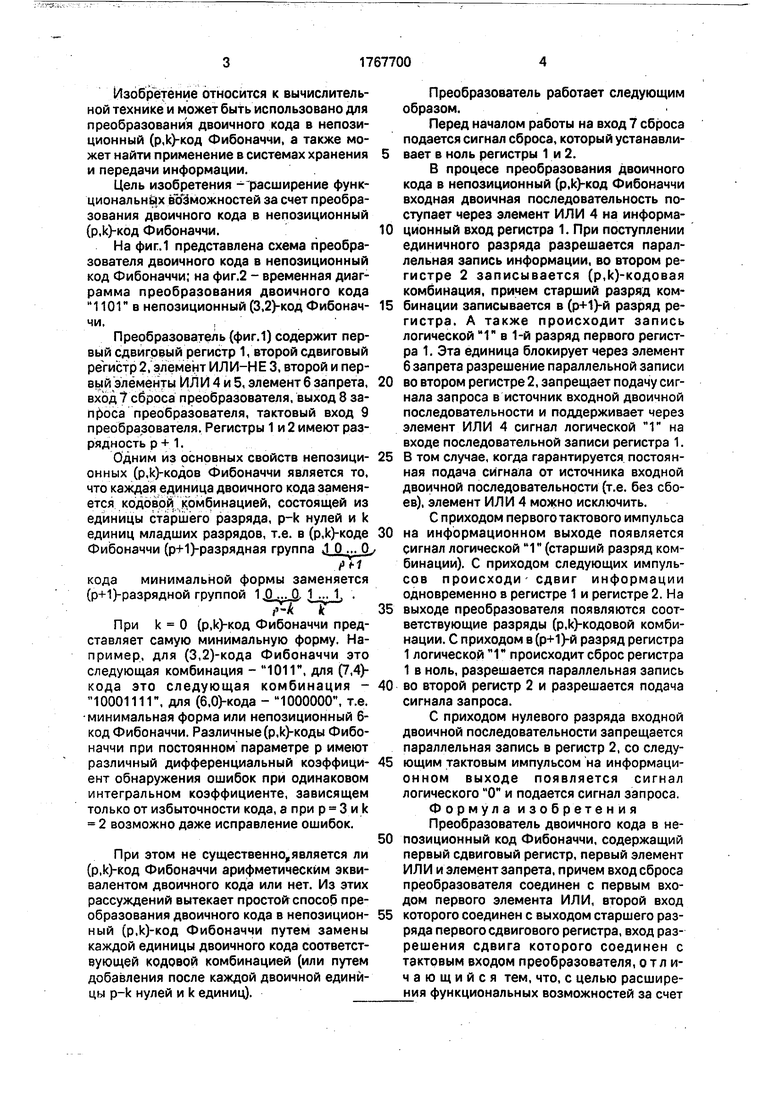

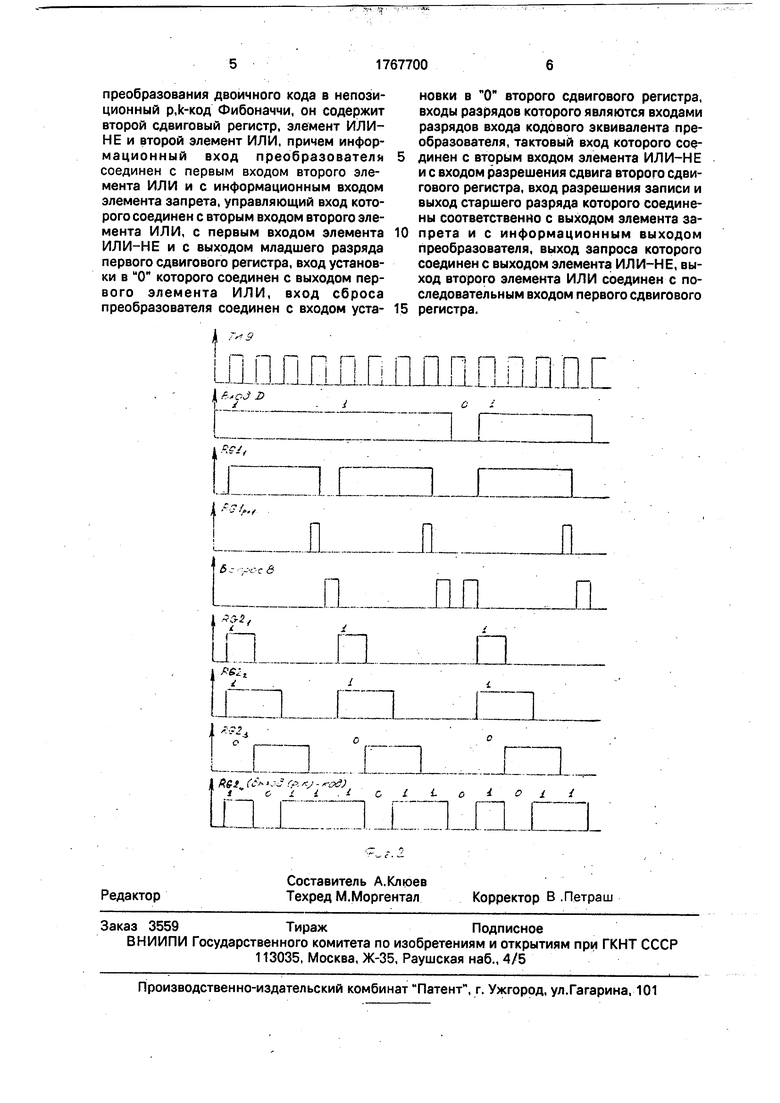

На фиг.1 представлена схема преобразователя двоичного кода в непозиционный код Фибоначчи; на фиг.2 - временная диаграмма преобразования двоичного кода 1 ЮГ в непозиционный (3,2)-код Фибонач- чи.

Преобразователь (фиг.1) содержит первый сдвиговый регистр 1, второй сдвиговый регистр 2, элемент ИЛИ-НЕ 3, второй и первый элементы ИЛ И 4 и 5, элемент 6 запрета, вход 7 сброса преобразователя, выход 8 запроса преобразователя, тактовый вход 9 преобразователя. Регистры 1 и 2 имеют разрядность р+ 1.

Одним из основных свойств непозици- онных (р,к)-кодов Фибоначчи является то, что каждая единица двоичного кода заменяется кодовой комбинацией, состоящей из единицы старшего разряда, p-k нулей и k единиц младших разрядов, т.е. в (р,к)-коде Фибоначчи (р+1)-разрядная группа J 0 ...Oj

ft-1

кода минимальной формы заменяется (р+1)-разрядной группой 1 ....Д Ј-.1,

лТ Jf

При k 0 (р,к)-код Фибоначчи представляет самую минимальную форму. Например, для (3,2)-кода Фибоначчи это следующая комбинация - 101 Г, для (7,4)- кода это следующая комбинация - 10001111, для (6, - 1000000, т.е. минимальная форма или непозиционный 6- код Фибоначчи. Различные (p.kj-коды Фибоначчи при постоянном параметре р имеют различный дифференциальный коэффици- ент обнаружения ошибок при одинаковом интегральном коэффициенте, зависящем только от избыточности кода, а при р 3 и k 2 возможно даже исправление ошибок.

При этом не существенно,является ли (р,к)-код Фибоначчи арифметическим эквивалентом двоичного кода или нет. Из этих рассуждений вытекает простой способ преобразования двоичного кода в непозицион- ный (р,к)-код Фибоначчи путем замены каждой единицы двоичного кода соответствующей кодовой комбинацией (или путем добавления после каждой двоичной единицы p-k нулей и k единиц).

Преобразователь работает следующим образом.

Перед началом работы на вход 7 сброса подается сигнал сброса, который устанавливает в ноль регистры 1 и 2.

В процесс преобразования двоичного кода в непозиционный (р,к)-код Фибоначчи входная двоичная последовательность поступает через элемент ИЛИ 4 на информационный вход регистра 1. При поступлении единичного разряда разрешается параллельная запись информации, во втором регистре 2 записывается (р,-кодовая комбинация, причем старший разряд комбинации записывается в (р+1)-й разряд регистра. А также происходит запись логической Г в 1-й разряд первого регистра 1. Эта единица блокирует через элемент 6 запрета разрешение параллельной записи во втором регистре 2, запрещает подачу сигнала запроса в источник входной двоичной последовательности и поддерживает через элемент ИЛИ 4 сигнал логической Г на входе последовательной записи регистра 1. В том случае, когда гарантируется постоянная подача сигнала от источника входной двоичной последовательности (т.е. без сбоев), элемент ИЛИ 4 можно исключить.

С приходом первого тактового импульса на информационном выходе появляется сигнал логической Г (старший разряд комбинации). С приходом следующих импульсов происходи- сдвиг информации одновременно в регистре 1 и регистре 2. На выходе преобразователя появляются соответствующие разряды (р,к)-кодовой комбинации. С приходом в (р+1)-й разряд регистра 1 логической Г происходит сброс регистра 1 в ноль, разрешается параллельная запись во второй регистр 2 и разрешается подача сигнала запроса.

С приходом нулевого разряда входной двоичной последовательности запрещается параллельная запись в регистр 2, со следующим тактовым импульсом на информаци- онном выходе появляется сигнал логического 0й и подается сигнал запроса.

Формула изобретения

Преобразователь двоичного кода в непозиционный код Фибоначчи, содержащий первый сдвиговый регистр, первый элемент ИЛИ и элемент запрета, причем вход сброса преобразователя соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом старшего разряда первого сдвигового регистра, вход разрешения сдвига которого соединен с тактовым входом преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей за счет

преобразования двоичного кода в непозиционный р,к-код Фибоначчи, он содержит второй сдвиговый регистр, элемент И ЛИНЕ и второй элемент ИЛИ, причем информационный вход преобразователя соединен с первым входом второго элемента ИЛИ и с информационным входом элемента запрета, управляющий вход которого соединен с вторым входом второго элемента ИЛИ, с первым входом элемента ИЛИ-НЕ и с выходом младшего разряда первого сдвигового регистра, вход установки в 0м которого соединен с выходом первого элемента ИЛИ, вход сброса преобразователя соединен с входом уста ш ШДШДГпЖПГ

, f OJ 2)

ZIIZL

izzmzzi

I ,.,

(iда

0

5

новки в О второго сдвигового регистра, входы разрядов которого являются входами разрядов входа кодового эквивалента преобразователя, тактовый вход которого соединен с вторым входом элемента ИЛИ-НЕ и с входом разрешения сдвига второго сдвигового регистра, вход разрешения записи и выход старшего разряда которого соединены соответственно с выходом элемента запрета и с информационным выходом преобразователя, выход запроса которого соединен с выходом элемента ИЛИ-НЕ, выход второго элемента ИЛИ соединен с последовательным входом первого сдвигового регистра.

л.

о.

| Устройство для обработки @ -кода | 1988 |

|

SU1649673A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования кода | 1988 |

|

SU1713105A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-10-07—Публикация

1988-12-20—Подача