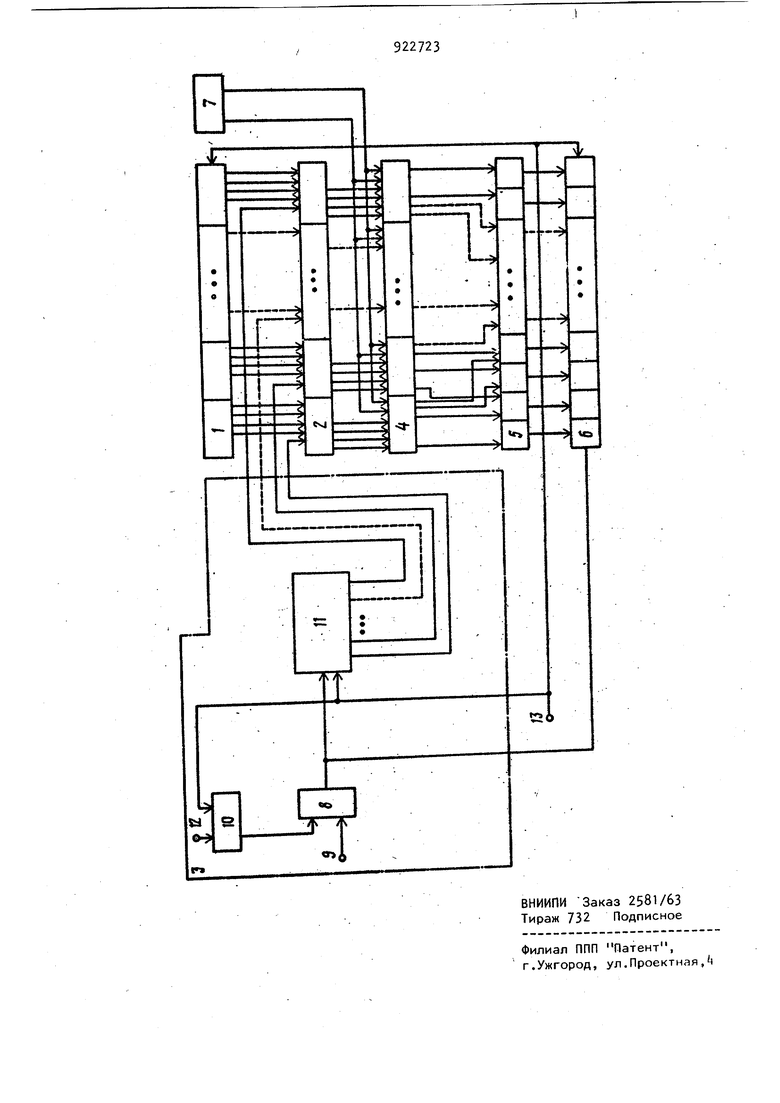

(5) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО Изобретение относится к автоматике и вычислительной технике и може:т. быть использовано при построении преобразователей кодов в арифметических устройствах. Известно устройство преобразования десятичного кода в двоичный, содержащее входной регистр с дешифратором десятичного кода, элементы И, элементы ИЛИ, запоминающее устройство, сумматор и генератор импульсов 12. Недостаток известного устройства состоит в низком быстродействии при получении дополнительного кода, что связано с использованием дополнительных блоков преобразования. Наиболее близким решением к изобретению по технической сущности и достигаемому результату является преобразователь кодов, содержащий входной регистр, группу элементов И, сумматор, сдвиговый регистр, триггер и элемент И, выполняющий преобразование КОДА- В ДВОИЧНЫЙ путем последовательного суммирования весов групп разрядов входного кода Г2. Недостатком данного преобразователя является ограниченность функциональных возможностей, что связано с отсутствием возможности получения дополнительного кода. Цель изобретения - расширение функциональных возможностей, заключающихся в обеспечении преобразования как прямых так и дополнительного кодов. Поставленная цель достигается тем, что в преобразователь двоично-десятичного кода в двоичный, содержащий входной регистр, группу элементов И, сумматор, сдвиговый регистр, триггер и элемент И, первый вход которого является тактовым.входом преобразователя, второй вход соединен с выходам три.ггера, а выход элемента И соединен с входой сдвигового регистра, выходы которого соединены с первыми входами элементов И группы, вторые входы которых соединены с выходами входного регистра, вход сброса которого соединен с входом сброса преобразователя .и входом сброса сумматора, входом начальной установки сдвигового регистра и нулевым входом триггера, единичный вход которого является входом пуска преобразователя, тактовый вхрд сумматора соединен с выходом элемента И, введены триггер знака, дешифраторы прямого и дополнительного кодов и группа элементов ИЛИ, первые и вторые входы ко торых соединены с сответствующими вы ходами дешифраторов прямого и дополнительного кодов, информаци-онные вхо ды которых соединены с выходами элементов И группы, а первый и второй управляющие входы соединены соответс венно с единичным и нулевым выходами триггера знака, выходы элементов ИЛИ группы соединены с входами сумматора На чертеже приведена блок-схема предлагаемого преобразователя. Преобразователь состоит из входного регистра 1, выходы которого соединены с первыми входами группы элементов И 2, блока 3 управления, дешифраторов k прямого и дополнитель ного кодов, группы элементов ИЛИ 5, сумматора 6, триггера 7 знака. . Один из возможных вариантов блока 3 управления содержит элемент И 8, первый вход которого соединен с тактовым входом 9 преобразователя, а второй - с выходом триггера 10, сдви говый регистр 11. Входы триггера 10 соединены: единичный - с входом 12 пуска преобразователя, а нулевой с входом 13 сброса преобразователя. Выход элемента И 8 соединен с входами синхронизации сдвигового регистра 11 и сумматора 6, Дешифраторы прямого и дополнительного кодов построены из элементо И, ИЛИ и НЕ и включают в себя деши(|)раторы, преобразующие десятичный код в прямой двоичный код для положительных чисел, или иначе называемые дешифраторами прямого кода, и дешифраторы, преобразующие десятичный код в дополнительный, или иначе называемые дешифраторами квазиобратного кода, для .отрицательных чисел. Преобразователь работает следую-. щим образом. Квазиобратным кодом является синтезированный код отдельных разрядов двоичногдесятичного числа, дающий 9 при суммировании обратный или дополнительный двоичный код. Если используют в преобразователе п двоичных разрядов, то максимально записываемое число Н 2°+2+.. .2. Обозначим: Р - прямой двоичный код; К - обратный двоичный код; тогда , , где Д - дополнительный двоичный код. прямой, двоичный L разрядов десятичнокод каждого из ,К.Н-Р-нЛх,, (Н-Хц) - обратный код каждого из L разрядов десятичного числа. Если суммируют обратные коды дво- ично-десятичных разрядов, тО получают следующий результат i, (H-X,)+{H-Xj+... + (H-Xi)LH-5: Х, . LH-P, что превышает значение обратного двоичного кода десятичного числа на (L-1 )Н, т.е. для Получения квазиобратного кода уменьшают обратный код каждого из разрядов двоично-десятичного числа в общейсумме на (L-1 );Н. Причем для упрощения преобразоват.еля квазиобратный код единиц (X/,) берут равным обратному четырехразрядному коду единиц, что позволяет получить его простым инвертированием прямого кода единиц; квазиобратный код разрядов Х(-Хц строят из тех же кодовых комбинаций, что и прямой код соответствующих разрядов, вследствие чего Дешифраторы квазиобратного кода по сложности и числу элементов эквивалентны дешифраторам прямого кода; квазиобратный код разряда Xj, равен Ккьи ,K(j-S, где К - обратный код разряда Хц, .H).H-ri|u, де йК-К- -КквЙ -Ки . ; 4i азница между обратным и квазиобратТо есть Ккй, K,-(L-1 )-Н+ ым кодами рдК;, И-15 как исользуются всего Ц разряда К,2. Аес. 90) 90 - мах.записыаемое число ё десятках; Кз дКерт(н-900)н-9-10 ; К- Н-9--10 KL,.,H-9-10--i; .е. лК Т5+9-10%,,..,+910-Ч эта ормула справедлива для , для Ки 15+910 для .

5.92

В данном случае S определено для получения обратного двоичного кода десятичного числа.

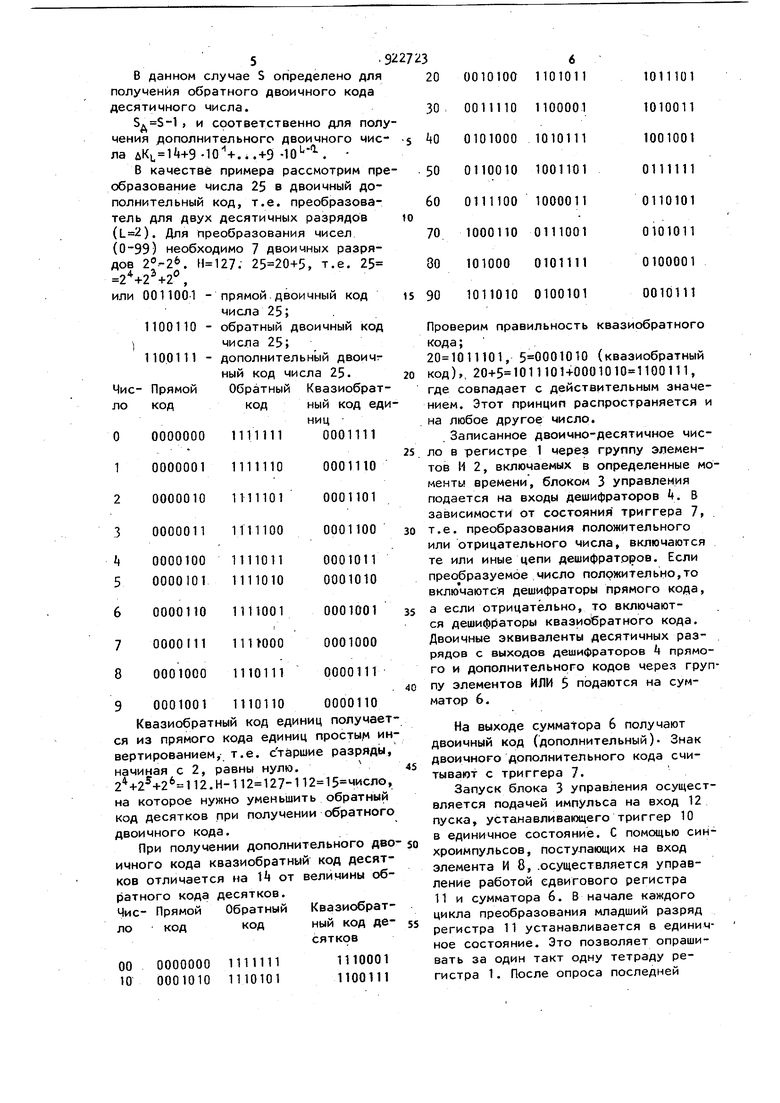

, и соответственно для получения дополнительного двоичного числа uKt, 1it+9.10+...+9 . В качестве примера рассмотрим преобразование числа 25 в двоичный дополнительный код, т.е. преобразователь для двух десятичных разрядов (). Для преобразования чисел (0-99) необходимо 7 двоичных разрядов 2°--2. . , т.е. 25 2 +2Ч2, или 0011001 прямой.двоичный код числа 25; 1100110обратный двоичный код числа 25; 1100111дополнительнь1й двоичг ный код числа 25. Квазиобратный код единиц получае ся из прямого кода единиц просты и вертированием, т.е. старшие разряды начиная с 2, равны нулю. .Н-112 127-112 15 число на которое нужно уменьшить обратный код десятков при получении обратног двоичного кода. При получении дополнительного дв ичного кода квазиобратный код десят ков отличается на И от величины об ратного кода десятков 20 1011101, 5 0001010 (квазиобратный код),, 20+5 1011101+0001010 1100111, где совпадает с действительным значением. Этот принцип распространяется и на любое другое число. Записанное двоично-десятичное число в регистре 1 через группу элементов И 2, включаемых в определенные моменты времени, блоком 3 управления подается на входы дешифраторов Ц. В зависимости от состояния триггера 7, т.е. преобразования положительного или отрицательного числа, включаются те или иные цепи дешифраторов. Если преобразуемое число положительно,то включаются дешифраторы прямого кода, а если отрицательно, то включаются дешифраторы квазиобратного кода. Двоичные эквиваленты десятичных разрядов с выходов дешифраторов k прямого и дополнительного кодов через группу элементов ИЛИ 5 подаются на сумматор 6. На выходе сумматора 6 получают двоичный код (дополнительный)- Знак двоичного дополнительного кода считывают с триггера 7. Запуск блока 3 управления осуществляется подачей импульса на вход 12 пуска, устанавливающего триггер 10 в единичное состояние. С помощью синхроимпульсов, поступающих на вход элемента И 8, .осуществляется управление работой сдвигового регистра 11 и сумматора 6. В начале каждого цикла преобразования младший разряд регистра 11 устанавливается в единичное состояние. Это позволяет опрашивать за один такт одну тетраду регистра 1. После опроса последней 7.9 тетрады регистра 1 сдвиговый регистр 11 переводится в нулевое состояние. Эффективность предлагаемого устройства заключается в повышений быст родействия преобразования. Формула изобретения Преобразователь двоично-десятично го кода в двоичный, содержащий входной регистр, группу элементов И, сумматор, сдвиговый регистр, триггер и элемент И, первый вход которого является тактовым входом преобразователя второй вход соединен с выходом триггера, а выход элемента И соединен с входом сдвигового регистра , выходы которого соединены с первыми входами элементов И группы, вторые входы которых соединены с выходами входного регистра, вход сброса которого соединен с входом сброса преобразователя и входом сброса сумматора, входом начальной установки сдвигового регистра и нулевым входом триггера, единичный вход кото рого является входом пуска преобразо 3 вателя, тактовый вход сумматора сое-, динен с выходом элемента И, отличающий ся тем, что, с целью расширения функциональных возможностей, заключающихся в обеспечении преобразования как прямых, так и дополнительного кодов, в него введены триггер знака, дешифраторы прямого и дополнительного кодов и группа элементов ИЛИ, первые и вторые входы, которых соединены с соответствующими выходами дешифраторов прямого и дополнительного кодов, информационные входы которых соединены с выходами элементов И группы, а первый и второй управляющие входы соединены соответственно с единичным и нулевым выходами триггера знака, выходы элементов ИЛИ группы соединены с входами сумматора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 226260, кл. G Об F 5/02, 1968. 2. Авторское свидетельство СССР W 637808, кл. G Об F 5/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

Авторы

Даты

1982-04-23—Публикация

1980-04-07—Подача