(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1987 |

|

SU1450112A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь кодов | 1986 |

|

SU1578813A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в непозиционный код Фибоначчи | 1988 |

|

SU1767700A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| "Преобразователь кода Фибоначчи-1 в код "золотой"-1 пропорции" | 1988 |

|

SU1649671A1 |

Изобретение относится к вычислительной технике и технике передачи информации и может быть использовано при преобразовании кода Фибоначчи с иррациональным отрицательньм основаг нием в двоичный код с контролем в процессе преобразования. Целью изобретения является повьшение достоверности преобразования. Преобразователь содержит сдвиговый регистр 1, блок 2 постоянной памяти, накапливающий сум матор 3, элемент 4 ИЛИ, дешифратор 5 запрещенных комбинаций, счетчик 6, информационные, разрешающий, установочный и тактовый входы 7-10, информационные и контрольный выходы 11, 12, 2 ил., 2 табл.

25

О9

tsd М

00

со

Й/г./

Изобретение относится к вычислительной технике и технике передачи информации и .может быть использовано при преобразовании 1-кода Фибоначчи с иррациональным отрицательным основанием в двоичный код с контролем в процессе преобразования.

Цель изобретения - повышение достоверности преобразования.

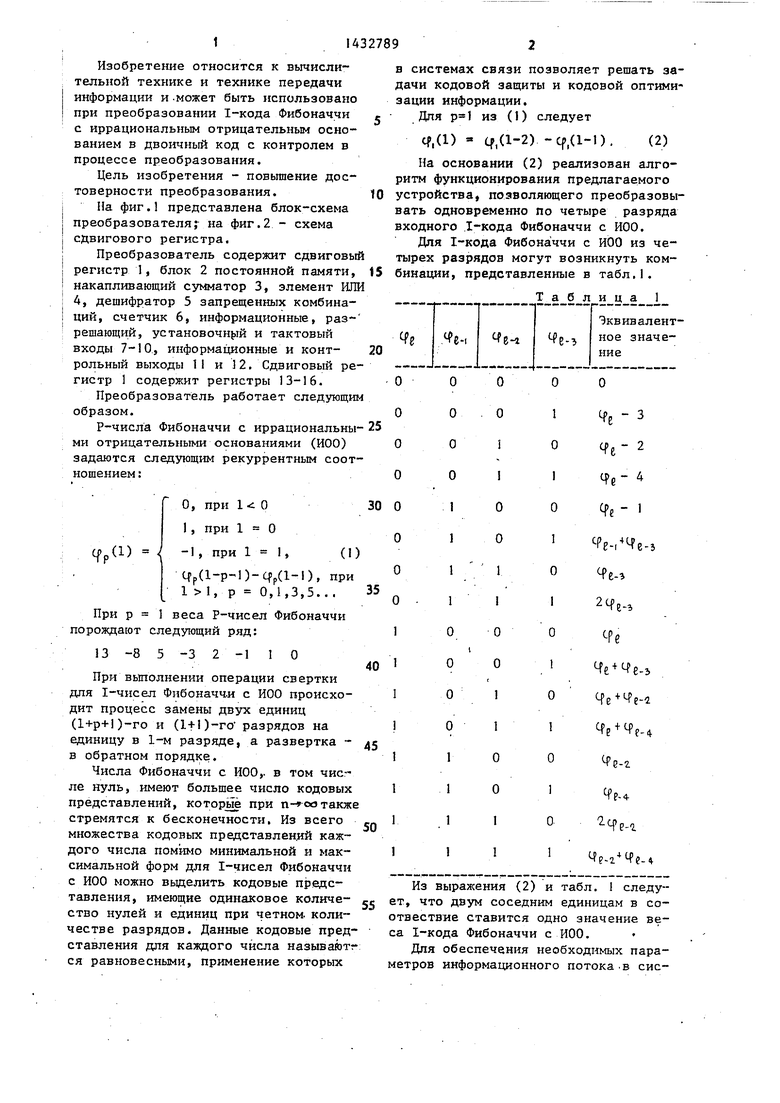

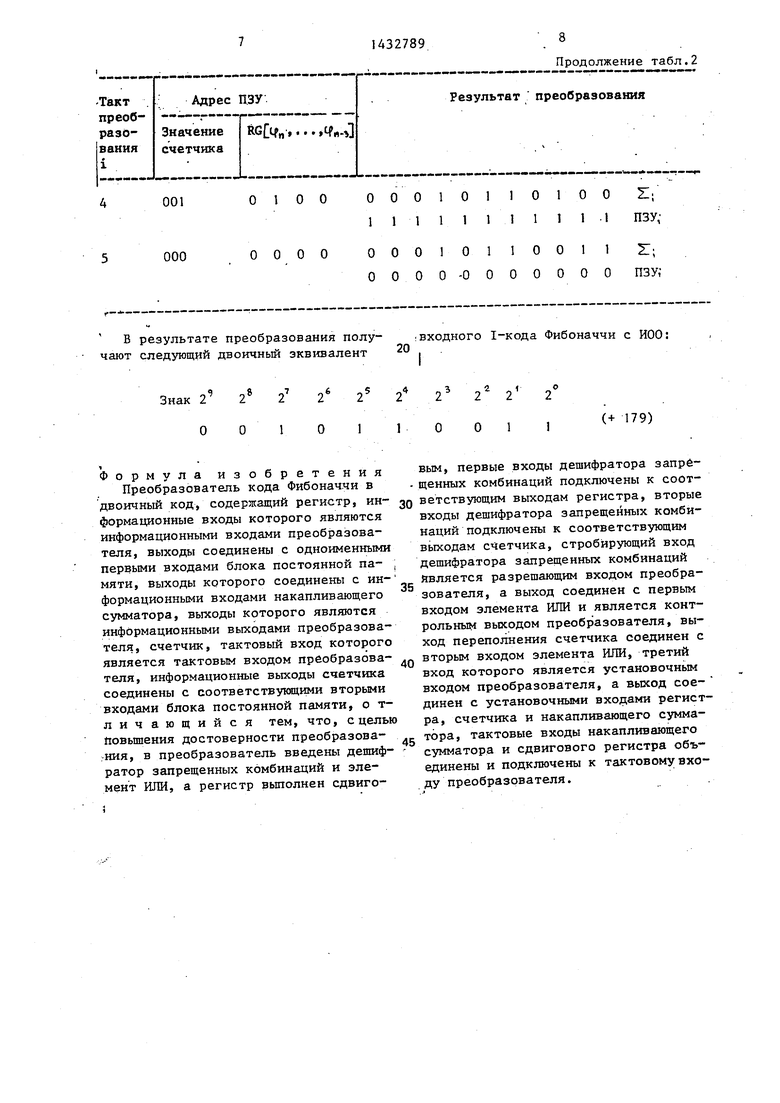

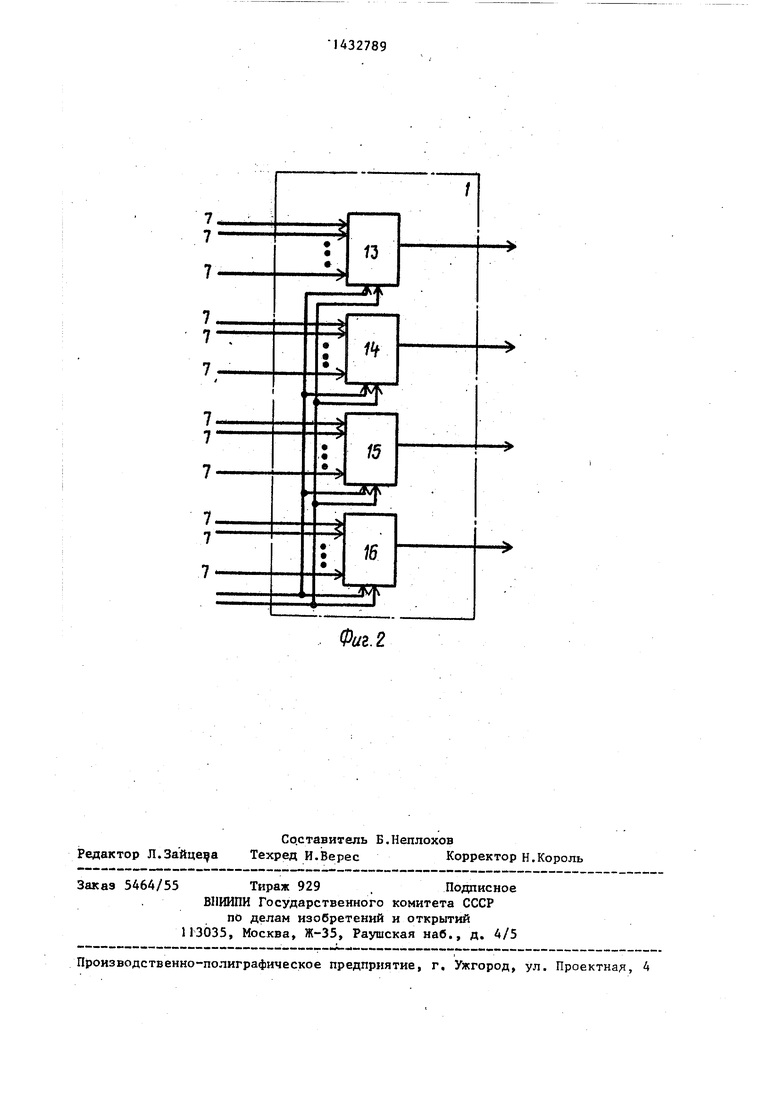

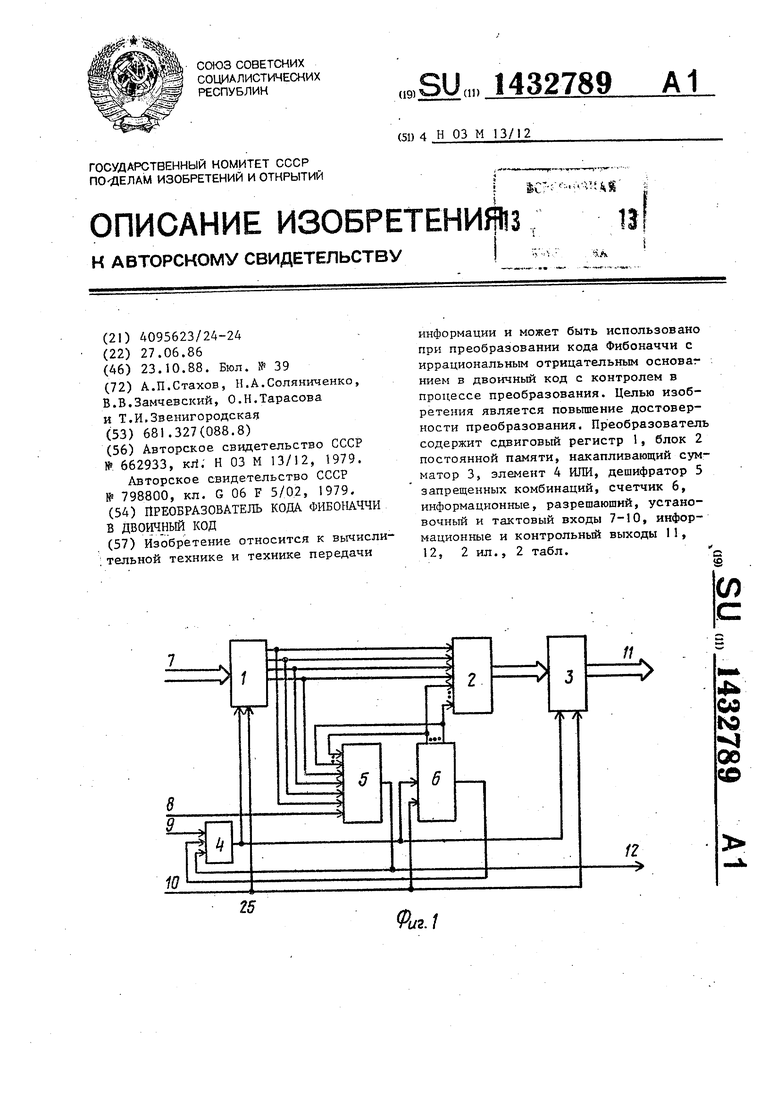

Па фиг.1 представлена блок-схема преобразователя; на фиг.2 - схема сдвигового регистра.

Преобразователь содержит сдвиговый регистр 1, блок 2 постоянной памяти, накапливающий сумматор 3, элемент ИЛИ 4, дешифратор 5 запрещенных комбинаций, счетчик 6, информационные, раз- решающий, установочн{ 1й и тактовый входы 7-10, информационные и конт- рольный выходы 11 и 12, Сдвиговый регистр 1 содержит регистры 13-16.

Преобразователь работает следующим образом.

Р-числа Фибоначчи с иррациональны- ми отрицательными основаниями (ИОО) задаются следующим рекуррентным соотношением :

О, при

Р

(1)

(I)

1, при

-1, при , .CfpCl-p-D-cfpCl-i), при 1 1, р 0,1,3,5...

При р 1 веса Р-чисел Фибоначчи порождают след5пощий ряд:

13 -8 5 -3 2-1 1 О

При выполнении операции свертки для 1-чисел Фибоначчи с ИОО происходит процесс замены двух единиц (1+р+|)-го и (Itl)-ro разрядов на единицу в 1-м разряде, а развертка в обратном порядке.

Числа Фибоначчи с ИОО,. в том числе нуль, имеют большее число кодовых представлений, KOTopjue при п- также стремятся к бесконечности. Из всего множества кодовых представлений каждого числа помимо минимальной и максимальной форм для 1-чисел Фибоначчи с ИОО можно выделить кодовые п зедс- тавления, имеющие одинаковое количество нулей и единиц при четном, количестве разрядов. Данные кодовые представления для кавдого числа называйте ся равновесными, применение которых

в системах связи позволяет решать задачи кодовой защиты и кодовой оптимизации информации.

Для из (1) следует

cf.d) Cf,(l-2) -Cf,(l-l). (2)

На основании (2) реализован алгоритм функционирования предлагае;мого устройства, позволяющего преобразовывать одновременно по четыре разряда входного 1-кода Фибоначчи с ИОО.

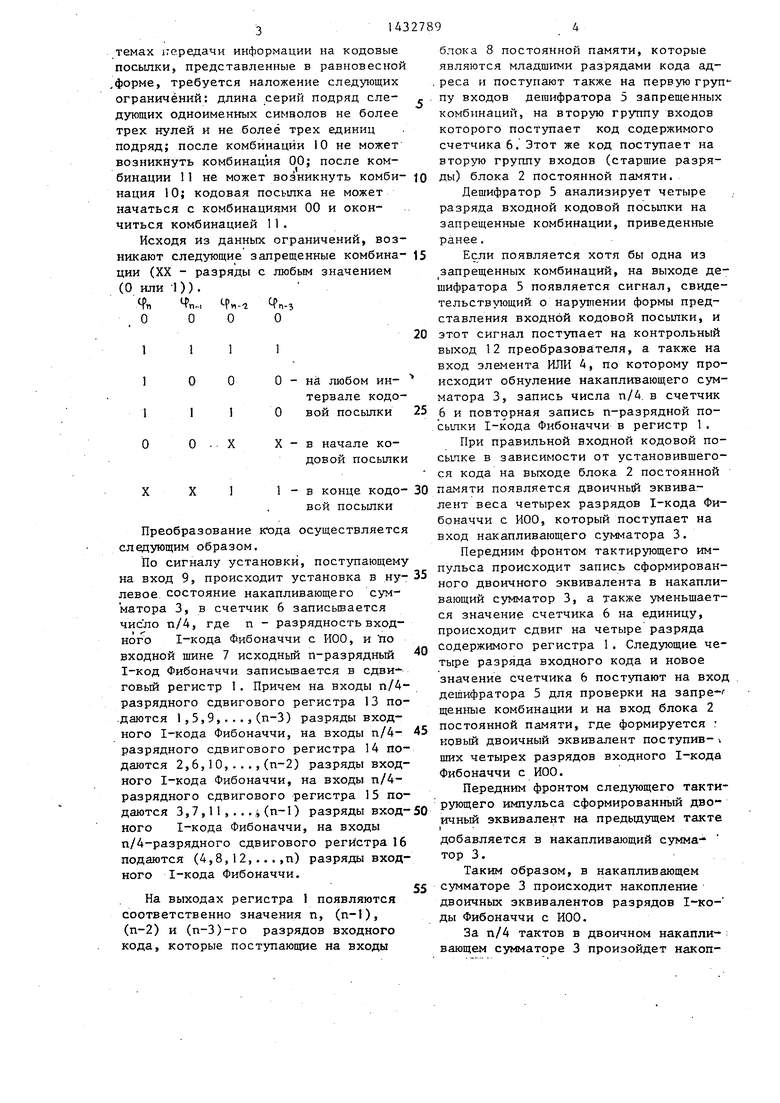

Для 1-кода Фибона ччи с ИОО из четырех разрядов могут возникнуть комбинации, представленные в табл,1.

Таблица 1

Из выражения (2) и табл. 1 следует, что двум соседним единицам в со- отвествие ставится одно значение веса 1-кода Фибоначчи с ИОО.

Для обеспечения необходимых параметров информационного потока.в сиетемах передачи информации на кодовые посылки, представленные в равновесной .форме, требуется наложение следующих ограничений: длина серий подряд следующих одноименных символов не более трех нулей и не более трех единиц подряд; после комбинации 10 не может возникнуть комбинация 00; после комбинации 11 не может возникнуть комбинация 10; кодовая посылка не может начаться с комбинациями 00 и окончиться комбинацией 11.

Исходя из данных ограничений, возникают следующие запрещенные комбина- 15 ции (XX - разряды с любым значением (О или )). я, %.., tp«-

0000

10

1

1

1

X

о X 1 блока 8 постоянной памяти, которые являются младш1гми разрядами кода адреса и поступают также на первую пу входов дешифратора 5 запрещенных комбинаций, на вторую группу входов которого поступает код содержимого счетчика 6. Этот же код поступает на вторую группу входов (старшие разряды) блока 2 постоянной памяти.

Дешифратор 5 анализирует четыре разряда входной кодовой посьтки на запрещенные комбинации, приведенные ранее.

Если появляется хотя бы одна из запрещенных комбинаций, на выходе дешифратора 5 появляется сигнал, свидетельствующий о нарушении формы представления входной кодовой посылки, и 20 этот сигнал поступает на контрольный выход 12 преобразователя, а также на вход элемента ИЛИ 4, по которому происходит обнуление накапливающего сумматора 3, запись числа п/4. в счетчик 25 6 и повт9рная запись п-разрядной посылки 1-кода Фибоначчи в регистр 1.

При правильной входной кодовой посыпке в зависимости от установившего- ся кода на выходе блока 2 постоянной в конце кодо- 30 памяти появляется двоичный эквивалент веса четырех разрядов 1-кода Фибоначчи с ИОО, который поступает на вход накапливающего сумматора 3.

Передним фронтом тактирующего импульса происходит запись сформированного двоичного эквивалента в накапливающий сумматор 3, а также уменьшается значение счетчика 6 на единицу, происходит сдвиг на четыре разряда содержимого регистра 1. Следующие четыре разряда входного кода и новое значение счетчика 6 поступают на вход дешифратора 5 для проверки на запре-с щенные комбинации и на вход блока 2

на любом ин- тервале кодовой посьтки

в начале кодовой посылки

вой посьтки

Преобразование осуществляется следующим образом.

По сигналу установки, поступаюп1ему на вход 9, происходит установка в ну- 35 левое состояние накапливающего сумматора 3, в счетчик 6 записьшается число п/4, где п - разрядность вход- ногЪ 1-кода Фибоначчи с ИОО, и по входной шине 7 исходный п-разрядный 1-код Фибоначчи записывается в сдви- говый регистр 1. Причем на входы п/4- разрядного сдвигового регистра 13 по.даются 1,5,9,...,(п-3) разряды вход,. I I, Ач постоянной памяти, где формируется

ного 1-кода Фибоначчи, на входы п/4- 45 м к н

новый двоичный эквивалент поступив- ших четырех разрядов входного 1-кода Фибоначчи с ИОО.

разрядного сдвигового регистра 14 подаются 2,6,10,.,.,(п-2) разряды входного 1-кода Фибоначчи, на входы п/4- разрядного сдвигового регистра 15 подаются 3,7,11,,..i(п-1) разряды входного 1-кода Фибоначчи, на входы n/4-разрядного сдвигового регистра 16 подаются (4,8,12,...,п) разряды входного 1-кода Фибоначчи.

.

На выходах регистра 1 появляются

соответственно значения п, (п-1), (п-2) и (п-3)-го разрядов входного кода, которые поступающие на входы

10

м к н

новый двоичный эквивалент поступив- ших четырех разрядов входного 1-кода Фибоначчи с ИОО.

Передним фронтом следующего тактирующего импульса сформированный двоичный эквивалент на предьщущем такте 1

добавляется в накапливающий сумма- тор 3.

Таким образом, в накапливающем сумматоре 3 происходит накопление двоичных эквивалентов разрядов 1-ко- ды Фибоначчи с ИОО.

За п/4 тактов в двоичном накапли- вающем сумматоре 3 произойдет накопление двоичных эквивалентов

(f -1)

групп (по четыре разряда в каждой группе) входного 1-кода Фибоначчи, а также будет сформирован двоичный эквивалент последней группы разрядов входного 1-кода Фибоначчи, запись Которого в накапливающий сумматор 3 осуществится передним фронтом последнего тактового импульса, с приходом которого содержимое регистра 1 и I счетчика 6 станет равным нулю. В этот I момент дешифратор 5 не должен вырабо- :тать сигнал ошибки, хотя и появятся четыре нуля на п (п-1), (п-2), (п-3) выходах регистра 1, так как все ин- формационные группы входного кода уже I проанализированы и сформированы их I двоичные эквивалентыч I Таким образом, результат преобразования будет записан и храниться в накапливающем сумматоре 3 до оконча- |ния тактирующего импульса. I По окончании тактирующего импуль- са на выходе счетчика 6 возникает г I .

15

14

13

12

11

610 -377 233 -144 89 -55

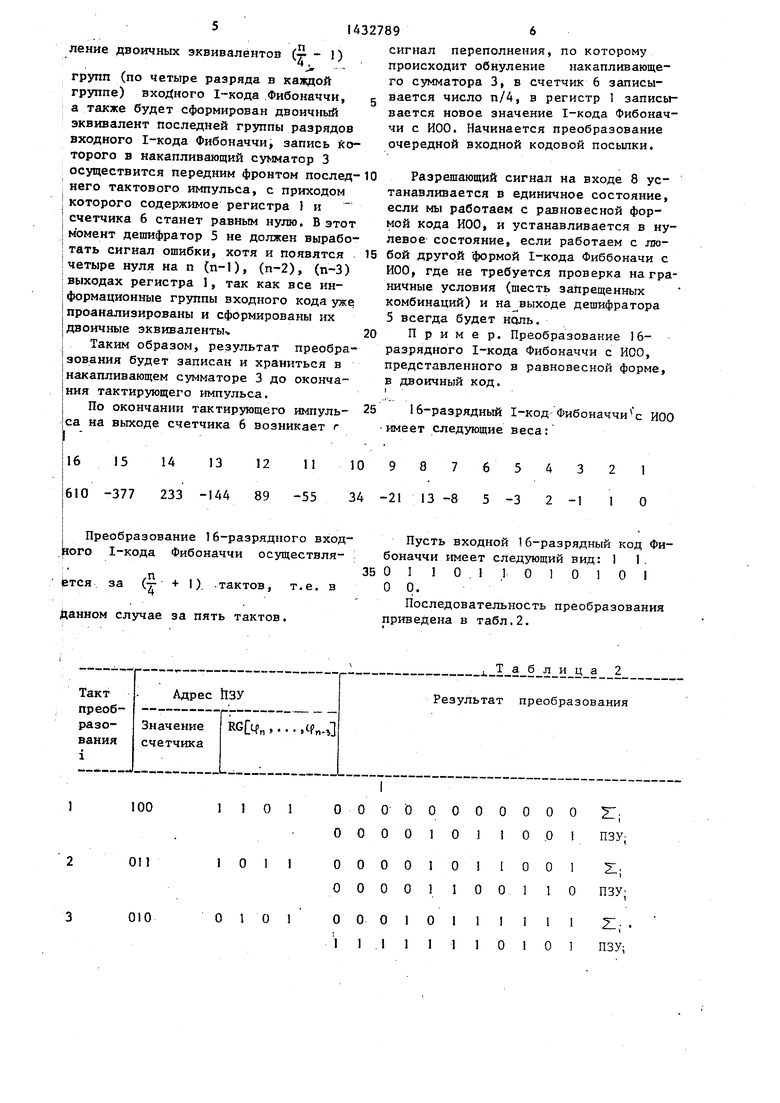

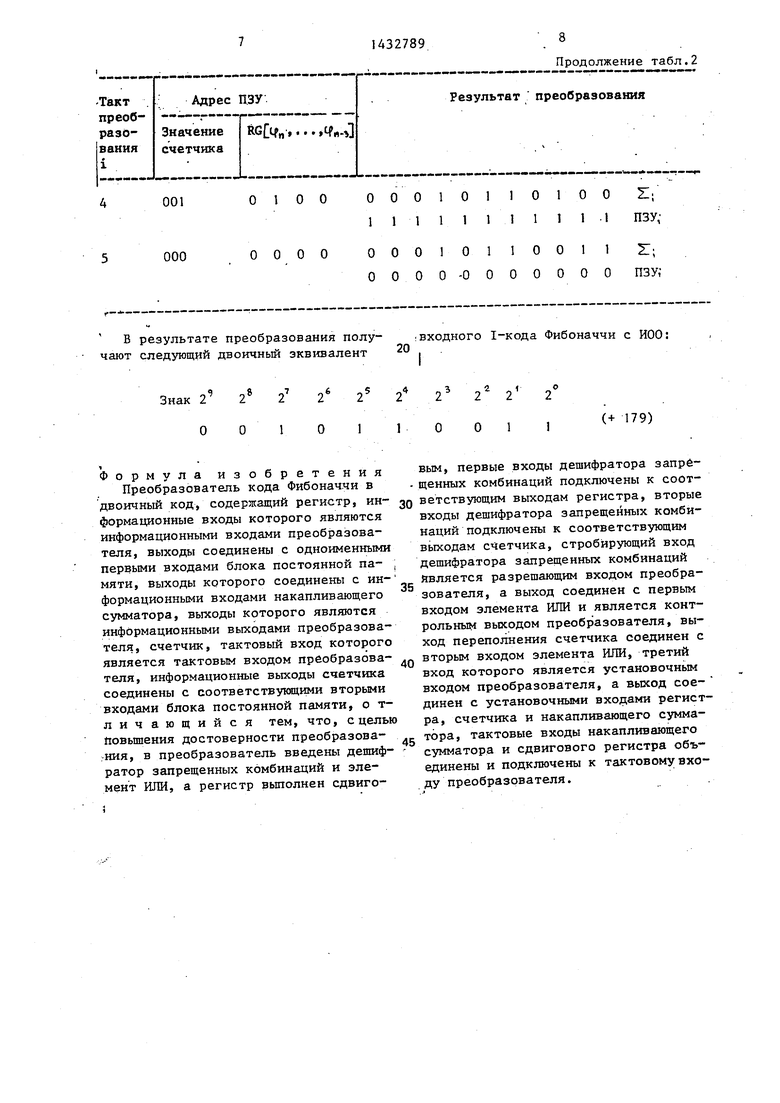

I Преобразование 16-разрядного вход- Пусть входной 6-разрядный код Фи- JHoro 1-кода Фибоначчи осуществля- боначчи имеет следующий вид: 1 1. .35 О J 1 О . 1 1 О 1 О 1 О 1

00.

Последовательность преобразования данном случае за пять тактов.приведена в табл.2.

Втся за (т ). тактов, т.е. в

100

1101 00 00 О 000000 ZT; о о о о 1 о i 1001 ПЗУ:

011

1011

010

0101

g 10

27896

сигнал переполнения, по которому происходит обнуление накапливающего сумматора 3, в счетчик 6 записывается число П/А в регистр 1 записывается новое значение 1-кода Фибоначчи с ИОО. Начинается преобразование очередной входной кодовой посылки.

Разрешающий сигнал на входе 8 устанавливается в единичное состояние, если мы работаем с равновесной формой кода ИОО, и устанавливается в нулевое состояние, если работаем с лю- бой другой формой 1-кода Фиббоначи с ИОО, где не требуется проверка на граничные условия (шесть запрещенных комбинаций) и на выходе дешифратора 5 всегда будет ноль.

Пример. Преобразование 16- разрядного 1-кода Фибоначчи с ИОО, представленного в равновесной форме, в двоичный код.

16-разрядный 1-код Фибоначчи с ИОО имеет следующие веса:

10

а

34 -21 13-8 5-3 2-1 1 О

В результате преобразования полу- : входного 1-кода Фибоначчи с ИОО; чают следующий двоичный эквивалент i

Знак 2 2« 2 2 2 2 2 2 2 2°

О О

Формула изобретения

Преобразователь кода Фибоначчи в двоичный код, содержащий регистр, информационные входы которого являются информационными входами преобразователя, выходы соединены с одноименными первыми входами блока постоянной па- мяти, выходы которого соединены с информационньми входами накапливающего сумматора, выходы которого являются информационными выходами преобразователя, счетчик, тактовый вход которого является тактовым входом преобразователя, информационные выходы счетчика соединены с соответствукяцими вторыми входами блока постоянной памяти, о т- личающийся тем, что, с целью йовьшения достоверности преобразова- ;ния, в преобразователь введены дешифратор запрещенных комбинаций и элемент ИЛИ, а регистр выполнен сдвигоО о 1

(+ 179)

0

5

0

5

вым, первые входы дешифратора запрещенных комбинаций подключены к соответствующим выходам регистра, вторые входы дешифратора запрещенных комбинаций подключены к соответствующим выходам счетчика, стробнрующий вход дешифратора запрещенных комбинаций Является разрешающим входом преобразователя, а выход соединен с первым входом элемента ИЛИ и является конт- рольньад выходом преобразователя, выход переполнения счетчика соединен с вторым входом элемента ИЛИ, третий вход которого является установочным входом преобразователя, а выход сое- динен с установочными входами регистра, счетчика и накапливающего сумматора, тактовые входы накапливающего сумматора и сдвигового регистра объединены и подключены к тактовому входу преобразователя.

Фиг.2

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-06-27—Подача