Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ в системах для выполнения умножения и вычисления суммы парных произведений чисел, представленных в любой позиционной системе счисления .

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения умножения чисел разрядностью и вычисления суммы парных произведений.

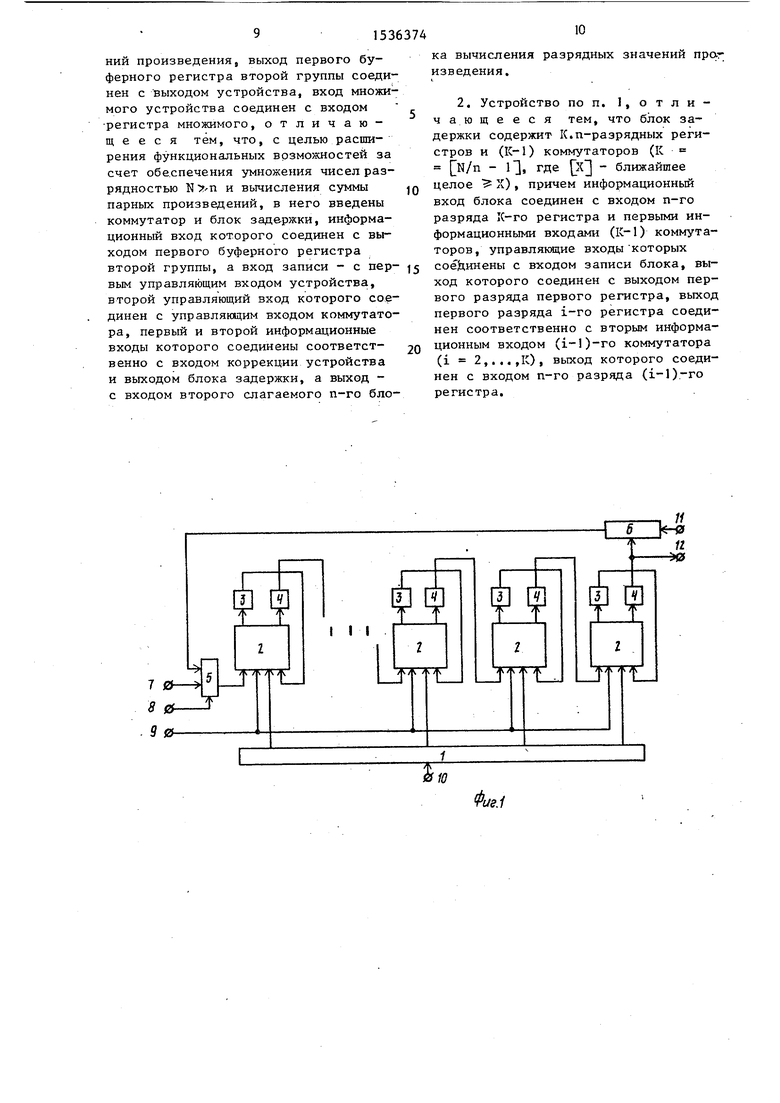

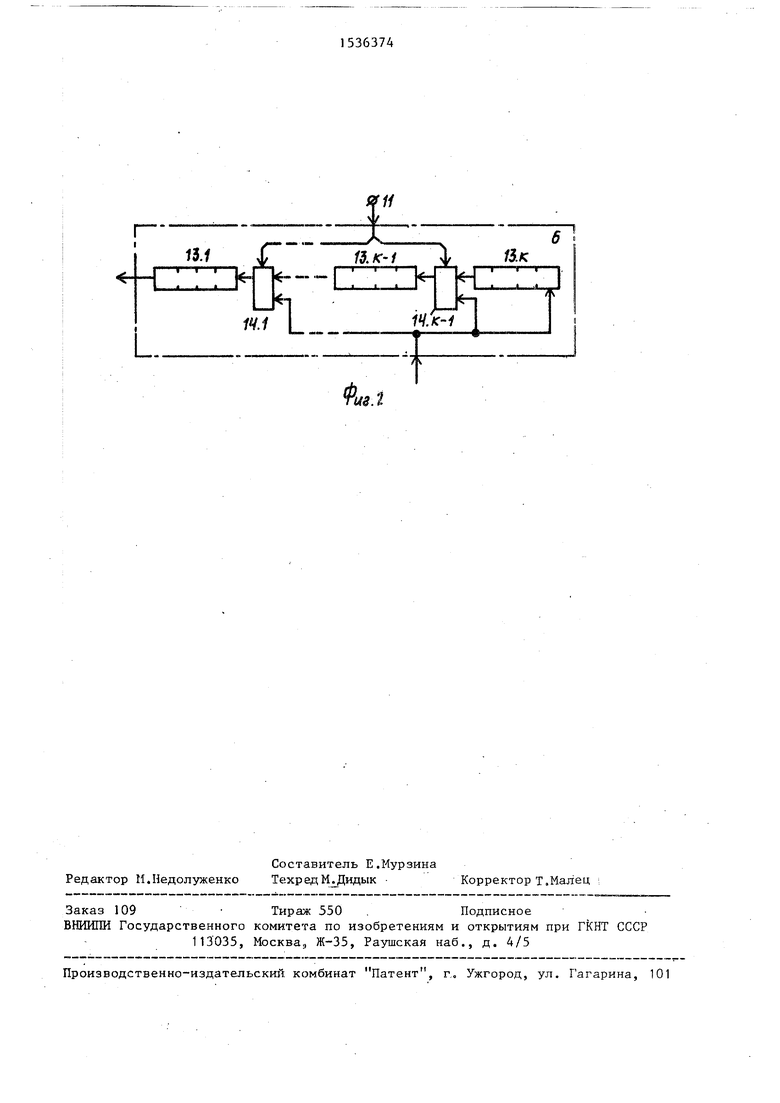

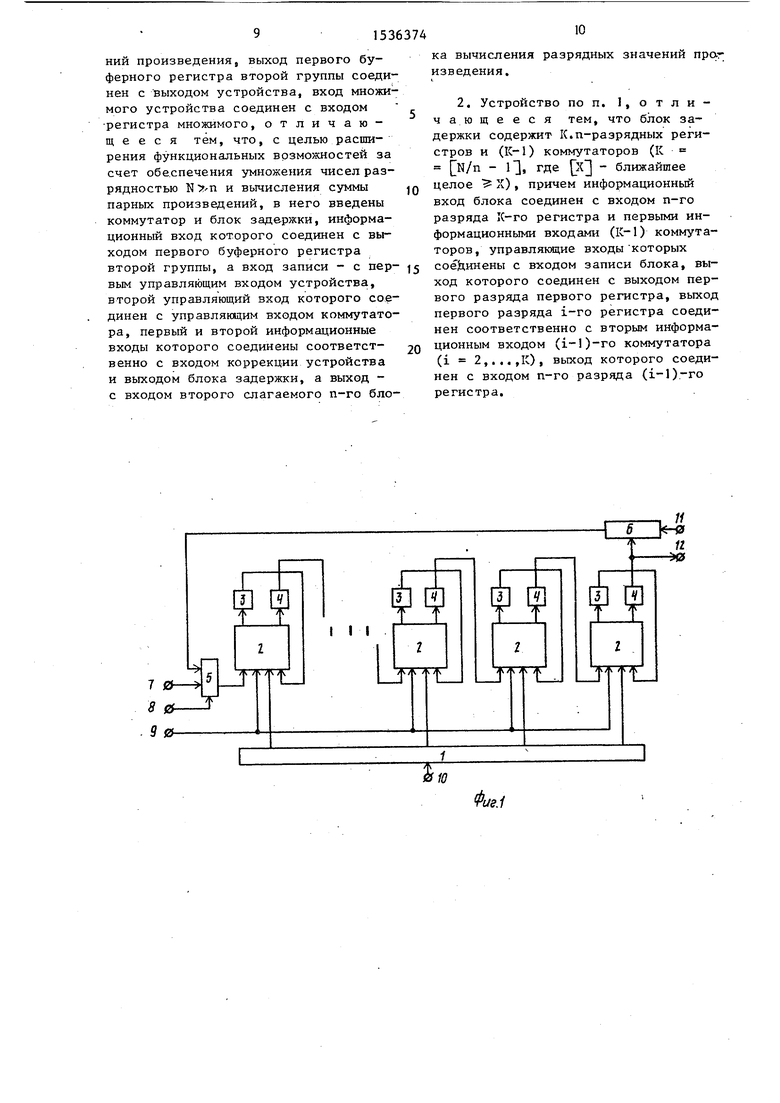

На фиг. 1 приведена функциональная схема устройства для умножения чисел; на фиг. 2 - функциональная схема блока задержки.

Устройство (фиг. 1) содержит п- разрядный регистр 1 множимого, п блоков 2 вычисления разрядных значений произведения, п буферных регистров 3 первой группы, и буферных регистров., 4 второй группы, коммутатор 5 и блок 6 задержки,, вход 7 коррекции устройства, первый 8 управляющий вход устройства, входы 9 и 10 множителя и множимого устройства, второй управляющий вход 11 устройства, выход 12 устройства.

Блок 6 задержки (Лиг. 2) содержит K.n-разрядных регистров 13 и (К-1) коммутаторов 14.

Рассмотрим функциональное назначение и реализацию узлов и блоков устройства.

СП

ОЭ

сг

GO

Јь

Регистр 1 множимого предназначен для хранения значения п разрядов множимого. Регистры 3 и 4 предназначены для хранения значения соответственно старшего и младшего разрядов разрядных произведений, формируемых блоками 2.

Блоки 2 предназначены для вычисления значений разрядных произведений по формуле

F + А + В,

где X, Y А, В

соответствующие разряды сомножителей; разрядные слагаемые, поступающие на входы первого и второго слагаемых блока 2.

Блоки 2 могут быть реализованы самыми различными методами и средствами в зависимости от требований к быстродействию, регулярности структуры и т.д., в частности возможно вы- полнение в виде постоянного запоминающего, устройства (ПЗУ) или в виде комбинационных схем, синтез которых может быть произведен любым из известных методов по таблице истинного функционирования блока.

Коммутатор 5 предназначен для подачи на вход второго слагаемого п-го блока 2 информации либо с входа 7 коррекции устройства, либо с выхода блока 6 задержки в зависимости от сигнала на его управляющем входе.

Блок 6 задержки предназначен для хранения разрядов суммы частичных произведений, используемых при умножении сомножителей разрядностью N n т.е. разрядностью до (К+1)-п, а также для хранения разрядов суммы .парных произведений n-разрядных сомножителей при вычислении суммы парных произведений. 3 зависимости от разрядности сомножителей на вход записи блока 6 подается сигнал, устанавливающий необходимую задержку информации перед ее выдачей для подсуммиро-- вания в блоках 2 при выполнении данной функции. Возможна различная реализация блока 6 задержки.

Регистры 13 блока 6 предназначены для хранения значения разрядов суммы частичных произведений при умножении чисел разрядностью N n и для хранени значения разрядов суммы парных произведений при выполнении устройством

0

5

0

0

5

5

0

5

0

5

соответствующей функции. На фиг. 2 в целях упрощения не показаны цепи синхронизации, разрешения записи и установки в нулевое состояние, однако одинаковые по функциональному назначению цепи являются общими для всех регистров 13, а также для регистров 3 и 4.

Коммутаторы 14 предназначены для подачи на вход соответствующего регистра 13 информации со своих первых либо вторых информационных входов в зависимости от сигнала на их управляющих входах.

Рассмотрим работу устройства для следующих случаев: умножение п-раз- рядных сомножителей; умножение сомножителей разрядностью вычисление, суммы парных произведений п-раз- рядных сомножителей.

Устройство работает следующим образом.

В исходном состоянии регистры 3 и 4 и регистры блока 6 обнулены.

В регистре 1 хранится без знака n-разрядное значение множимого.

На первый управляющий вход 8 устройства подан потенциал, настраивающий коммутатор- 5 на передачу информации с входа 7 коррекции устройства. Умножение осуществляется за 2п тактов.

В каждом из п первых тактов работы устройства на его вход 9 поступает по одному разряду значение множителя, начиная с младшего разряда. При этом в i-м блоке 2 производится умножение разряда множителя, поступающего на его вход множителя с входа 9 множителя устройства, на 1-й разряд множимого , поступающего на его вход множимого с выхода 1-го разряда регистра 1 множимого, и прибавление к младшему разряду получившегося при этом произведения через входы первого и второго слагаемых блока 2 старшего разряда произведения 1-го блока 2, сформированного в предыдущем такте и хранимого в i-м регистре 3, и младшего разряда произведения (i+l)-ro блока 2, сформированного в предыдущем такте и хранимого в (Ј+1)-м регистре 4, Сформированные i-м блоком 2 старший и младший разряды произведения с его выходов записываются соответственно в i-e регистры 3 и 4.

После выполнения п первых тактов на вход 9 множителя устройства поступает нулевая информация и далее осу- ществляется еще дополнительно п тактов, в течение которых из устройства выводится с соответствующим преобразованием информация, хранимая в регистрах 3 и 4. Вывод 2.п-разрядного произведения сомножителей в устройстве осуществляется через его выход 12 по одному разряду в каждом такте. В рассмотренном случае на вход 7 коррекции устройства во всех тактах подается нулевая информация. В тех же случаях, когда требуется получить округленное произведение, необходимо в первом такте работы устройства на его вход 7 подать корректирующую информацию (для округления 2.п-разрядного произведения n-разрядных сомножителей, представленных в двоично- кодированной щестнадцатиричной системе счисления, необходимо подать в первом такте работы на вход 7 двоичный код 1000). Это позволяет осуществить округление результата без дополнительных временных затрат. Кроме того, вход 7 может быть использован также для введения результирующей коррекции по знакам множимого и множителя в случае умножения чисел в дополнительном коде.

Умножение т.поразрядных чисел (т 2,...,К+1) в устройстве производится за га циклов, каждый из которых реализуется за (га.п + п) таютов. Для получения правильного результата блок 6 настраивается на задержку (m-l),n тактов (это достигается подачей соответствующего потенциала на вход 11 устройства). В каждом цикле работы осуществляется вычисление частичного произведения т.п-разрядного множителя на п разрядов множимого и подсуммирование к нему суммы частичных произведений, сформированной в предыдущем цикле и хранимой в блоке 6 (старшие разряды) и в регистрах 4 (младшие разряды). В итоге получается новая сумма частичных произведений.

При этом запись в блок 6 первого разряда суммы частичных произведений, формируемой блоками 2, начинается во втором такте каждого цикла, так как в первом такте этот разряд записывается в первЕлй регистр 4. Кроме того, младшие п разрядов этой суммы, хотя и подаются в этом цикле в блок б, однако в дальнейшем не используются в вычислениях (это достигается соответ0

5

0

5

ствующей настройкой коммутатора 5), остальные m.n разрядов этой суммы в соответствующие моменты времени поступают на вход второго слагаемого n-го блока 2 (ввод младших п разрядов осуществляется одновременно с выводим старших п разрядов этой же суммы из регистров 3 и 4 в блок б в течение данного цикла, а ввод оставшихся n(m-l) разрядов - по одному разряду, в каждом такте следующего цикла),

Рассмотрим работу устройства в одном цикле.

Ъ регистре 1 множимого хранятся п соответствующих разрядов т.п-разрядного множимого, в регистрах 3 - нулевая информация, а в регистрах 4 - соответствующие разряды суммы частичных произведений, сформированной в предыдущем цикле. На первый управляющий вход 8 устройства подан потенциал, настраивающий коммутатор 5 на передачу информации с выхода блока 6. Задержка в (m-l).n тактов в блоке 6 достигается тем, что коммутатор 14,(и-1) настроен на передачу информации с информационного входа блока 6 на вход n-го разряда регистра 13.(тп-1), а остальные коммутаторы 14 организуют цепь последовательно соединенных регистров 13.

В каждом такте из m.n первых тактов рассматриваемого цикла на вход 9 множителя устройства поступает по одному разряду значения множителя, начиная с младших разрядов, при этом в блоках 2 выполняются те же операции, что и в первых п тактах в случае д вычисления произведения п-разрядных сомножителей. Отличие состоит только в том, что в первом такте цикла на входах второго слагаемого всех блоков 2 присутствуют п соответствующих раз- с рядов суммы частичных произведений, сформированной в предыдущем цикле и хранимой в регистрах 4, остальные n(m-l) разрядов этой суммы поступают по одному разряду в каждом такте с выхода блока 6 через коммутатор 5 на вход второго слагаемого n-го блока 2 (за исключением (п-1) последних из m.n первых тактов, когда под управлением сигнала на входе 8 устройства коммутатор 5 не разрешает прохождение информации из блока 6, так как в это время на выходе блока 6 появляются младшие (п-1) разрядов сформированной в этом цикле суммы частичных

0

5

0

5

произведений). После окончания rn,n-ro такта на вход 9 множителя устройства подается нулевая информация, а на выходе 8 устройства все еще присутствует потенциал, запрещающий прохожде- «ие информации из блока 6 в блоки 2, т.е. на вход второго слагаемого п-го блока 2 подаются нули.

В (т,п+1)-м такте начинается вы- в|од старших п разрядов суммы частич- н|ых произведений, сформированной в Зтим цикле и хранимой в регистрах 3 И 4. После окончания (m,n+J)-ro так- Т/а на вход 8 устройства подается по- енциал, настраивающий коммутатор 5 tm передачу информации с выхода блока 6

В течение последующих (п-1) так- foB на вход 9 множителя устройства Продолжает поступать нулевая информа- Ция и с выхода первого регистра 4 в 6 выводится с соответствующим гфеобразованием информация, хранимая и регистрах 3 и 4, т.е. выводятся Старшие разряды суммы частичных про- Изведений, сформированной в рассматриваемом цикле, а с выхода блока 6 И это время в регистры 4 загружаются Через вход второго слагаемого п-го блока 2 младшие разряды этой же сум- мы частичных произведений, используемые в следующем цикле вычислений.

Одновременно с выполнением n-ti+nj-ro Такта на вход 10 множимого устройства Подаются следующие п разрядов множимог И производится их запись в регистр I.

Вывод через выход 12 устройства Окончательного значения произведения й.п-разрядных сомножителей осуществляется по одному разряду в каждом из первых п тактов каждого цикла (младшие m.n разрядов произведения) и по одному разряду в каждом такте последнего т-го цикла (старшие m.n разрядов произведения ),

Вычисление суммы парных произведеРчий в виде , Y, (где X;, Y- 1 1

n-разрядные сомножители) производится за Ј циклов, каждый из которых реализуется за 2п тактов.

В каждом цикле осуществляется вычисление произведения X;-Y, (i в ,...,Ј) и прибавление к нему уже сформированной суммы парных произве- е

дений

X Y1, хранящийся в блоке

О задержки и поступающей на вход второго слагаемого п-го блока 2 через

коммутатор 5. На второй управляющий вход И устройства при этом подается потенциал, настраивающий блок 6 на задержку в п тактов, а на первом управляющем входе 8 устройства во всех тактах всех циклов работы присутствует потенциал, настраивающий коммутатор 5 на прохождение информации с выхода блока 6, Запись суммы произведений - Xj-Y; в блок 6 начинается

j

со второго такта 1-го цикла, как и в предыдущем случае, а начиная с (n+J)-ro такта этого цикла эта сумма по разряду в каждом такте с выхода блока б поступает на вход второго слагаемого п-го блока 2. В результате этого одновременно с выводом из регистров 3 и 4 старших разрядов суммы произведений осуществляется запись п его младших разрядов в регистры 4 для выполнения следующего цикла.

Прием очередных значений множимого и множителя осуществляется одновременно с выполнением последнего такта цикла.

Результат вычисления суммы парных произведений выводится по одному разряду в каждом такте последнего iL-ro цикла.

Формула изобретения

1. Устройство для умножения чисел содержащее регистр множимого, п блоков вычисления разрядных значений произведения и две группы по п буферных регистров, причем вход множителя устройства соединен с входами множителя п блоков вычисления разрядных значений произведения, входы множимого которых соединены с выходами соответствующих разрядов регистра множимого, вход первого олагаеього 1-го блока вычисления разрядных значений произведения соединен соответственно с выходом 1-го буферного регистра первой группы (i l,.,,,n), вход второго слагаемого j-ro блока вычисления разрядных значений произведения соединен соответственно с выходом (j+l)-ro буферного регистра второй группы, входы п буферных регистров первой и второй групп соединены соответственно с выходами старшего и младших разрядов соответствующих п блоков вычисления разрядных значений произведения, выход первого буферного регистра второй группы соединен с выходом устройства, вход множимого устройства соединен с входом регистра множимого, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения умножения чисел разрядностью N п и вычисления суммы парных произведений, в него введены коммутатор и блок задержки, информационный вход которого соединен с выходом первого буферного регистра второй группы, а вход записи - с первым управляющим входом устройства, второй управляющий вход которого соединен с управляющим входом коммутатора, первый и второй информационные входы которого соединены соответственно с входом коррекции устройства и выходом блока задержки, а выход - с входом второго слагаемого n-го бло10

374ю

ка вычисления разрядных значений про.- изведения.

2. Устройство по п. отличающееся тем, что блок задержки содержит K.n-раэрядных регистров и (К-1) коммутаторов (К « N/n - , где |Y - ближайшее целое X), причем информационный вход блока соединен с входом п-го разряда К-го регистра и первыми информационными входами (К-1) коммутаторов, управляющие входы которых

15 соединены с входом записи блока, выход которого соединен с выходом первого разряда первого регистра, выход первого разряда 1-го регистра соединен соответственно с вторым информа2Q ционным входом (i-l)-ro коммутатора (i 2,..,,К), выход которого соединен с входом n-го разряда (i-l)-ro регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1988 |

|

SU1529215A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для быстрого выполнения операций умножения и вычисления суммы парных произведений чисел, представленных в любой позиционной системе счисления. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения умножения чисел разрядностью N*98N и вычисления суммы парных произведений. Введение в устройство, содержащее регистр 1 множимого, блоки 2 вычисления разрядных значений произведения, буферные регистры первой 3 и второй 4 групп, блока 6 задержки и коммутатора 5 с соответствующими связями позволило вычислять произведение чисел переменной длины и сумму парных произведений N-разрядных чисел с незначительными аппаратурными затратами. Кроме того, устройство имеет однородную структуру, что дает возможность эффективно его использовать при применении БИС и СБИС. 1 з.п. ф-лы, 2 ил.

| Карцев М.А., Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| М.: Радио и связь, 1981, с | |||

| Способ прикрепления барашков к рогулькам мокрых ватеров | 1922 |

|

SU174A1 |

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-08—Подача