Изобретение относится к электро- .технике и может быть использовано в системах микропроцессорного управле- ния тиристорными преобразователями для электроприводов постоянного тока с целью линеаризации характеристик звена тиристорный преобразователь- двигатель в электроприводе.

Известно устройство для линеаризации характеристики ТП 1 , содержащее блок синхронизации, RS-триггер, генератор тактовой частоты, блок кольцевых регистров, блок сравнения и два счетчика, обеспечивающее кусочно-линейную аппроксимацию нелинейной зависимости характеристики ТП-нагрузка.

Недостаток устройства - быстрый рост числа элементов схемы и ее чрезмерное усложнение и уменьшение надежности при увеличении числа участков аппроксимации.

Этот недостаток преодолен в устройстве-прототипе Ј2, которое по технической сущности наиболее близко к предлагаемому устройству. Устройство-прототип содержит простейший вы числитель, включающий блок совпадения, выходы которого соединены с входами блока памяти. Характеристика, записанная в блоке памяти вычислителя, компенсирует нелинейность звена ТП-Н в области непрерывных токов (РНТ). В этом смысле устройство-прототип является частным случаем устройств управления тиристорным преобразователем и двигателем также содержащими вычислители с блоками памяти, но использующими микропро. цессоры для реализации более сложVI VI VJ

ю v)

31

ных арифметических функций. Информационные входы блока совпадения в устройстве-прототипе служат для за дания кода управления, а управляю- щий вход блока совпадения и вход элемента задержки соединены и являются входом синхронизации, выход элемента задержки соединен с S-входом RS-триг гера, R-вход которого подключен к ВЫ ходу дешифратора, а прямой выход соединен с одним входом элемента И, другой вход которого предназначен для подачи импульсов тактовой частоты, выход элемента И соединен со сче ным входом счетчика, к входам записи которого подключены выходы блока памяти, к стробирующему входу счетчика подключен выход элемента задержки, выходы счетчика связаны с входом де- шифратора.

Недостаток устройства-прототипа в том, что оно не обеспечивает линеаризацию характеристики ТП в области прерывистых токов, что снижает точ- ность управления преобразователем, и не обеспечивает управления реверсивным ТП, это ограничивает функциональЛ ные возможности устройства.

Целью изобретения является повы- шение точности и линейности характеристик устройства.

Эта цель достигается тем, что в устройство введены вычислитель, сумматор, управляемый инвертор кода, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и двунаправленный коммутатор, выходы которого являются выходами устройства, управляющий вход коммутатора соединен со знаковым входом кода задания устрой- ства, а информационный вход - с выходом дешифратора, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно со знаковыми входами кода задания и кода ЭДС уст- ройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом i инвертора кода и входом переноса сумматора, информационные входы инвертора кода подключены к информационным входам кода ЭДС устройства, а выходы инвертора кода соединены с информационными входами сумматора, выходы которого подключены к первой группе I, информационных входов вычислителя, вторая группа 1 информационных входов вычислителя подключена к информационным входам кода задания устройства, вход прерывания

Q g О

5

0

,- п 5

0

5

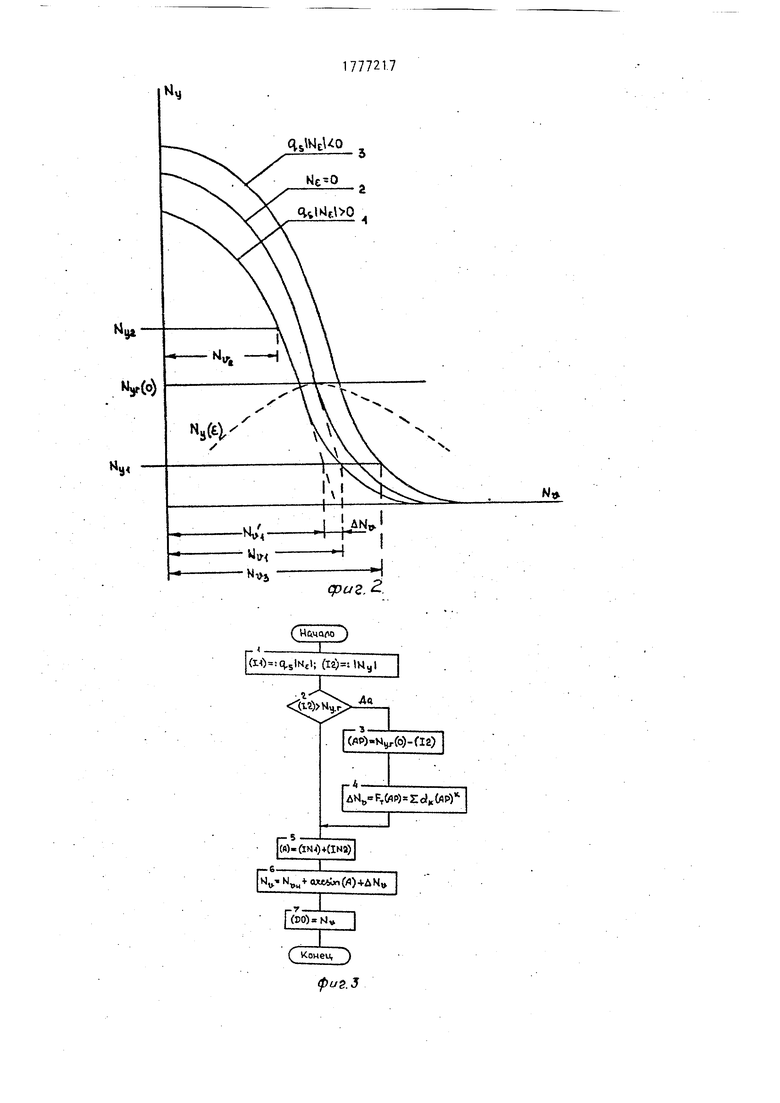

INT вычислителя соединен с входами синхронизации устройства, магистраль адреса данных вычислителя соединена с входами-выходами элемента памяти и входами записи счетчика, причем вычислитель обеспечивает функциональную зависимость между сигналами на информационных входах I,, 1 и сигналом ДО на входах записи счетчика, работая по алгоритму фиг.З.

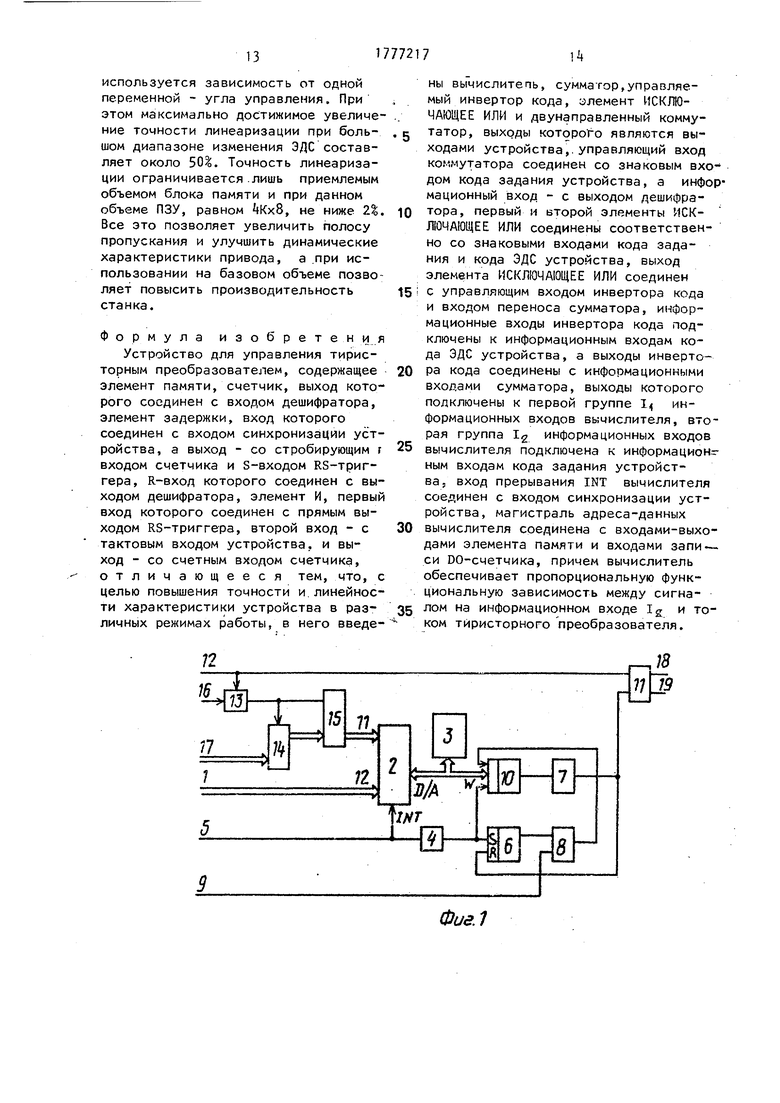

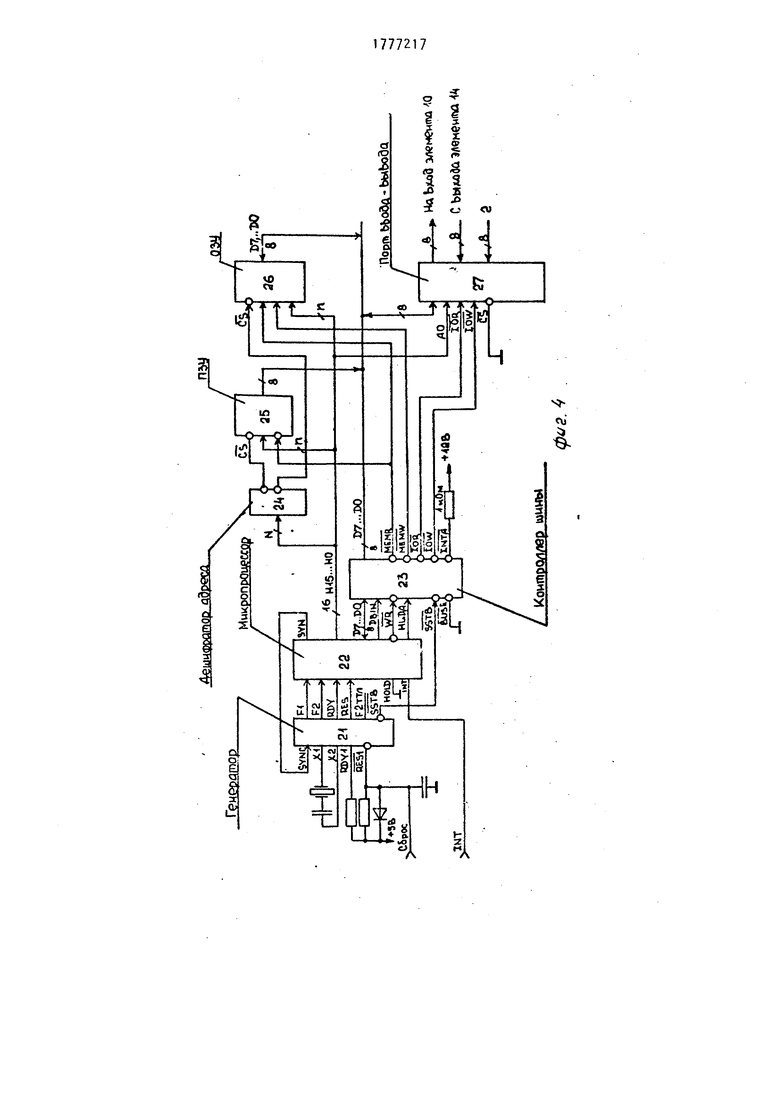

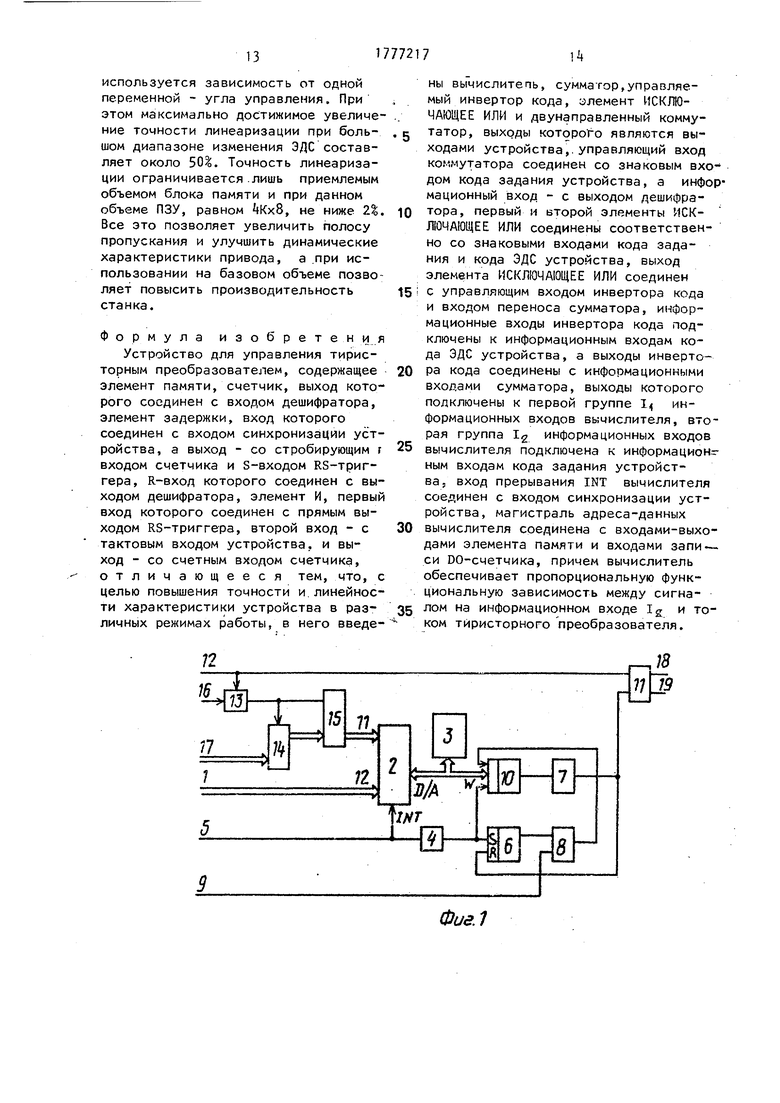

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - нелинейные характеристики звена ТП-Н на фиг.З - блок-схема алгоритма, реализуемого вычислителем; на фиг.k - структурная схема вычислителя с элементом памяти; на фиг.5 - временная диаграмма работы устройства; на фиг.6 - приниципиальная инвертора кода и сумматора; на фиг.7 - принципиальная схема двухканального коммутатора.

Предлагаемое устройство содержит вычислитель 2, в состав которого входит однокристальная ЭВМ, элемент памяти 3, счетчик 10, дешифратор 7, элемент задержки k, RS-триггер 6, элемент И 8, двухканальный коммутатор 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, управляемый инвертор кода И, сумматор 15, вход 5 синхронизации устройства, вход 9 тактовой частоты, вход 12 знака кода управления, вход 16 знака кода ЭДС, информационные входы 17 абсолютной величины кода ЭДС, информационные входы 1 абсолютной величины кода управления, выходы 18 и 19 устройства, на которых появляются импульсы зажигания тиристоров.

В статическом состоянии первая группа информационных входов If однокристальной ЭВМ 2 соединена с выходами сумматора 15, вторая группа информационных входов 12 - с информационными входами 1 абсолютной величины кода управления устройства, вход прерываний вычислителя 2 соединен с входом элемента задержки k и входом 5 синхронизации устройства, магистраль адреса данных вычислителя через порты ввода-вывода соединена с входами-выходами элемента памяти 3 и входами ДО записи счетчика 10, строби- рующий вход которого соединен с S-входом RS-триггера 6 и выходом элемента задержки 4, выход счетчика 10 соединен с входом дешифратора 7, выход которого соединен с информацией5Г/

ным входом двунаправленного коммутатора 11 и R-входом триггера 6, вы- ход триггера 6 соединен с первым входом элемента И 8, второй вход которого предназначен для подачи импульсов тактовой частоты с входа 9 устройства, вход знака кода управления 12 устройства соединен с управляющим входом двунаправленного комму- татора 11, вход знака кода ЭДС 16 соединен с входом элемента 13 ИСКЛЮЧАЮЩЕЕ ИЛИ, выхол которого соединен с управляющим входом управляемого инвертора кода 1 и входом переноса сумматора 15. Входы 17 абсолютной величины кода ЭДС соединены с информационными входами управляемого инвертора кода 1, выходы которого соединены с информационными входами сум- матора 15.

Устройство компенсирует нелинейность звена ТП-Д, которая в режине непрерывного тока (PUT) определяется зависимостью VI.

JB sin JL- sinCU+JL-J-e

(1)

IT

m

m

а в режиме прерывистого тока

зависимостью

(РПТ)

-- sin(lT +

2 }

(2)

де

V

/Е

гп

е -Ј,,/Ј

И 1 по

относительное среднее значение тока звена ТП-Н; относительное значение ЭДС нагрузки;

- угловая ллитель- . ность импульса тока.

Если принять естественное допущеие, что максимальное значение тока

может иметь место при 6 0, то

Г

га

ти ния

Длл получения линейной зависимос- icp K;N, где N - код управле- в устройстве, необходимо реализовать обратную нелинейность

N

К

V

Г V . N +N61 ц- arcsin

LmN.,4

iV

NM01CC NeMOItc

N

г.

Kvtf

NF KC e код угла управления ТП;

код ЭДС нагрузки; масштабные коэффициенты.

Нелинейная зависимость (3) являетфункцией суммы двух аргументов

К

ги

ти ния j. Q 5 0

и Np. Вид этой зависимости при5

0

5

0

45

Nlj

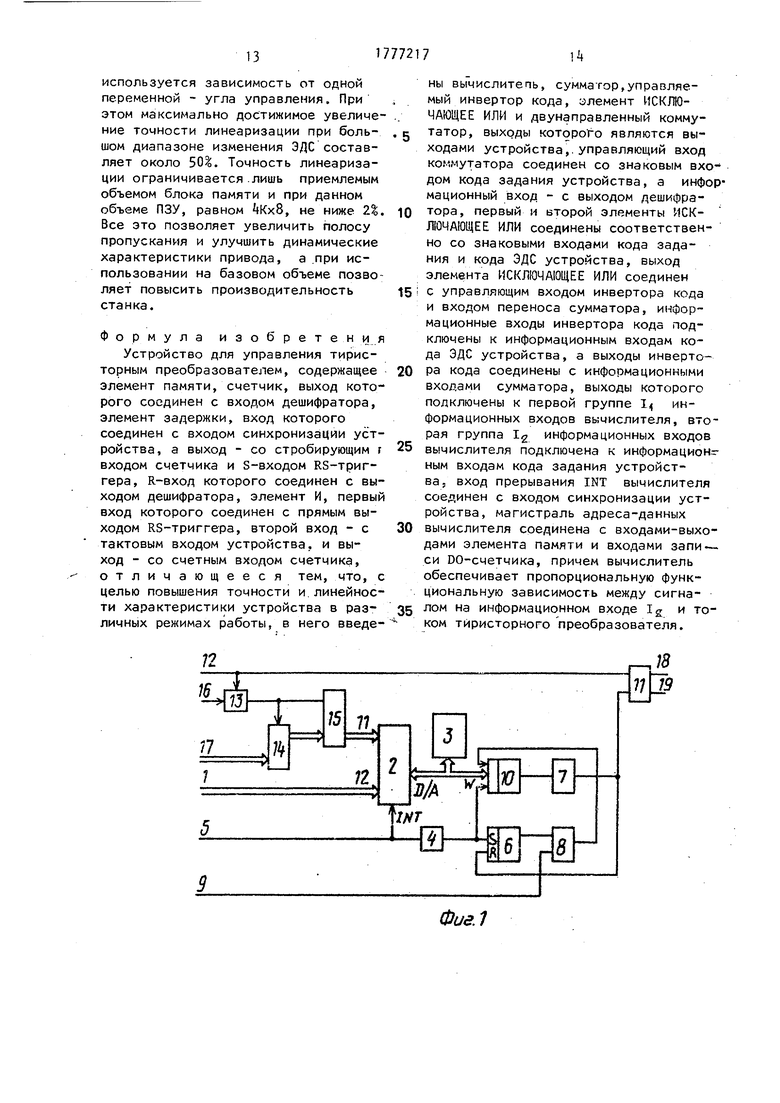

веден на фиг.2. Точная граница между РНТ и РПТ определяется пунктирной линией на фиг.2. При компенсации статической нелинейности за границу режимов РНТ и РПТ можно принять горизонтальную прямую Nyi(- (о) (фиг.2), ордината которой соответствует точной границе при 6 0. Из фиг.2 видно, что в РПТ при N,.)rcNu,r (°) значение кода угла N, отличается от значения определенного для РНТ при том же значении аргумента, на величину поправки UN..

Поправка UN вычисляется по таблично-заданной кривой, как и само значение N, вычисляемое по таблично- заданной зависимости (3). Однако, если зависимость (3) кода угла N-p от кодов Ny и Ng выражается явно . формулой (3), то , вычисление поправки UNV более сложно.

Зависимость между током хср ТП, ЭДС Е нагрузки и углом управления РПТ задается системой трансцендентных уравнений

m Г . /„. Ъ

чр т- sin т (1Г т0

50

--Vе cos0 sio T + X -9 ) - D sinOT-б)} + 5(0-1) 0;

(За)

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ управления вентильным преобразователем | 1990 |

|

SU1739457A1 |

| Способ управления вентильным преобразователем | 1985 |

|

SU1319200A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| БЕСКОНТАКТНЫЙ ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА | 2006 |

|

RU2331963C1 |

| БЕСКОНТАКТНЫЙ ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА | 2017 |

|

RU2658678C1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

Сущность изобретения: устрой- ,ство содержит вычислитель (2), счетчик (10), элемент задержки (4), RS-триггер (6), элемент И (8), дешифратор (7), двухканальный коммутатор (11), управляемый инвертор кода (14) и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

m Т

-ж- sin

-- К гаК««

N fr/waKc

где D ехр(- ctg9);

0 - arctg Ј00ТЯ - тангенс угла нагрузки;

Тй - электромагнитная постоянная звена ТП-Д; Ц, - угловая частота

сети.

Система уравнений (За) не имеет аналитического решения, поэтому нельзя в явной форме получить зависимость ty f (icp , 6 ) или подобную ей в масштабе зависимость N # f (N,N&)

Эта зависимость в табличной форме получается с помощью вычислительной программы, которая вычисляет значение Д из второго уравнения (За) по заданным о и Ј:

-вычисляет значение i c. по значениям tf , 6 , fl ;

-строит таблицу зависимости f (i Cp, Ј) и подобную ей таблицу NV f (N«j, NЈ);

-вычисляют поправку

ANU NV- N f ,(N, NЈ),

где% i - arcsin - значение ко- К-m J -

Значению q5 1 соответствует логический О на выходе элемента 13, а qs -1 - логическая 1 на этом вы- холе. Такое формирование адреса повышает точность реализации функции арксинуса при неизменном объеме памяти устройства.

30

Константы N

VH

К

V

Nur (0) записаны в ячейки элемента памяти 3, Nyn 2Уь1 - нормирующий

да угла,соответствующее РНТ памяти 3, UK - нормирующий Программа, производящая указанные множитель; ъ - число разрядов машин- вычисления, написана на Фортране и Ного слова оез знака. Табличные за- выполняется на машине СМ. В предлага-35 , m и ппрокси- емом устройстве используется только зависимость &NV f, (Ny,NЈ).

Вообще говоря UN-ц, зависит от

мированной полиномом зависимости поправки f CNy.r (O)-NuJ хранятся в элементе памяти 3.Адреса обращения к этим зависимостям формируются выN

и и NЈ , однако на практике влиямированной полиномом зависимости поправки f CNy.r (O)-NuJ хранятся в элементе памяти 3.Адреса обращения к этим зависимостям формируются вынием Ne можно пренебречь и опреде --40 числителем 2 в соответствии с прог- лять UNV из однопараметрической раммои работы Устройства, хранящейся

ь% в элементе памяти 3.

Устройство работает следующим образом.

нелинейности в РНТ и РПТ, что дает выигрыш в точности, значительно превышающий уменьшение точности, вызванное неучетом зависимости u N-y, от Ng

табличной зависимости v

f NV (о) - Ny , при NЈ 0.

При задании аргумента в виде N,.r(o)- Выпрямительный или инверторный ре- -Nu. обеспечивается гладкая стыковка 4 . тп

э .. .. работы ТП определяется с помощью

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 на входы 12 и 16 которого поданы знак кода задания Ny и знак кода NЈ ЭДС --------v - & нагрузки. Элементы 13 - 15 формируТаким образом в памяти вычислите- 50 ют слагаемое N -, кода Jeca

ля 3 заносятся две зависимости машинном формате. Если знаки кодов

Ny и Ne на входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 совпадают (q l), то на выходе элемента 13 устанавливает-, ся уровень логического нуля и код абсолютной величины ЭДС JNЈj, поступающий с входов 17 устройства, проходит без изменений через управляе V

1 v

fr -«... га

arcsin

. Nft I ,S1n---.-J ;

О)

55

UN

V

f NK (0)-N3

г

(6)L N0

для РПТ

где Nfl Ny + Ng.; коэффициенты полинома Чебышева, которыми аппроксимируется табличная зависимость функции поправки. Первая зависимость используется как в РНТ,так и в РПТ. Адрес формируется с использованием элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, управляемого инвертора 14 и сумматора 15.

Алгоритм формирования адреса можно представить выражением

20

25

NA llNy| + qg iNell ,

Г 1 При sgn N sgn NЈ,

ГДе qS -1 при sgn N sgn Ng.

Значению q5 1 соответствует логический О на выходе элемента 13, а qs -1 - логическая 1 на этом вы- холе. Такое формирование адреса повышает точность реализации функции арксинуса при неизменном объеме памяти устройства.

Константы N

VH

К

V

Nur (0) записаны в ячейки элемента памяти 3, Nyn 2Уь1 - нормирующий

памяти 3, UK - нормирующий множитель; ъ - число разрядов маши Ного слова оез знака. Табличные за- , m и ппрокси

памяти 3, UK - нормирующий множитель; ъ - число разрядов машин- Ного слова оез знака. Табличные за- , m и ппрокси-

мированной полиномом зависимости поправки f CNy.r (O)-NuJ хранятся в элементе памяти 3.Адреса обращения к этим зависимостям формируются вычислителем 2 в соответствии с прог- раммои работы Устройства, хранящейся

в элементе памяти 3.

Устройство работает следующим образом.

Выпрямительный или инверторный ре- . тп

177721

мый инвертор кода 1 на вход сумматора 15 и далее без изменений - на выход сумматора 15, так как на вход переноса сумматора поступает логи- ,. ческий 0 с выхода элемента 13.

Сказанное соответствует формированию кода адреса в ОЭВМ 2

NA l|Ny| - qs |NЈ|| -|)Ng| + 10

+ | y| при q6 1.

Если знаки кодов Nq и Ng на входах элемента 13 не совпадают (q5 15 -1), то на выходе элемента 13 устанавливается уровень лог.1 и код I Ne| преобразуется инвертором кода 1 в обратный код. Пусть, например, на входах 17 имеет место код )NЈ| 20 00100110, на выходах элемента И будет обратный код |Ne|0 11011001, на выходах сумматора 15 - дополнительный код |Ne|,Ј |Ne|0+ t 11011010, так как к входу перено- 25 а сумматора 15 поступает лог.1 с выода 13. Теперь ОЭВМ 2 сформирует код адреса

A II + q9|Ne|| l|Ngl +|Ne,| 30 1Ы - |Ne| при qs -1,

ак как сложение с дополнительным коом и вычитание - эквивалентные one- ,- рации в машинном формате.

На фиг.6 приведена схема, реализующая это преобразование и состояая из инвертора кода 1k на микрохеме К155 ЛП5 и сумматора 15 на мик- 0 росхеме К155 ИМЗ. Если на выходе лемента 13 имеет место логическая 1, что соответствует несовпадению знаков N и Ng, то код | NeJ преобразуется инвертором кода 1 в обрат- 5 ный код и поступает на сумматор 15 где по входу переноса к нему добавляется 1 и с выходов 20 на входы Ij вычислителя поступает значение Ng в дополнительном коде.CJQ

Алгоритм работы вычислителя приведен на фиг.З. В блоке 1 алгоритма опрашиваются группы I и lЈ входов вычислителя и формируются коды (lt

Ч& lNeh ( lNyl в блоке 2 gg определяется режим тока и для РПТ формируется адрес АР таблицы полиномиальной функции поправки в блоке 3, а в Злоке kt из таблицы поправки, раз,777217

10

,.

10

15 20 , 25 30

- ,-

к- 0 - 5 CJQ

в

gg , з,мещенной в элементе памяти 3 извлекается значение поправки. Следует подчеркнуть, что поправку можно как вычислять из формулы С), так и определять по таблице, хотя на практике принят последний способ для экономии процессорного времени. Далее определяется в блоке 5 адрес таблицы арксинуса для РНТ в блоке 6 вычисляется значение кода угла N с использованием таблицы арксинуса, размещенной в элементе памяти 3, а в блоке 7 оно передается на входы ДО записи счетчика 10. Таким образом вычислитель 2 обеспечивает требуемую функциональную зависимость между кодом угла Nv и кодом задания Nu. Из-за ограниченного быстродействия вычислителя код угла , формируется с некоторой задержкой относительно начала программы вычислителя, определяемого импульсами синхронизации с входа 5, формирующимися при переходе напряжения сети через ноль и поступающими на вход прерывания вычислителя. Для исключения возможного дополнительного запаздывания на период прерывания в устройстве предусмотрен элемент задержки, который задерживает импульсы с входа 5 на время С (см.фиг.), превышающее время выполнения программы вычислителя. Благодаря этому в каждом цикле рабо-о ты устройства используется значение, вычисленное в этом же цикле. Код N., связанный пропорциональной зависимостью с углом управления, является сигналом управления преобразователем.

Этот сигнал подается на преобразователь код-временной интервал, реализованный на счетчике 10, дешифраторе 7, триггере 6 и элементе И 8.

Преобразователь код-временной интервал осуществляет преобразование кода N-y, управления преобразователем в фазовый сдвиг импульсов управления ВП следующим образом.

Импульсами с выхода элемента задержки код NTJ/C выхода блока 3 вычислителя записывается в счетчик 10, и одновременно устанавливается триггер 6. Тем самым разрешается поступление импульсов тактовой частоты с входа Э (см.фиг.5,д) через элемент И 8 на вычитающий вход счетчика 10. Содержимое последнего начинает ступенчато-линейно уменьшаться (см.

фиг.5,з), т.к. код N-у, записанный в счетчик 10, через разные промежутки времени, определяемые периодом так- тоаой частоты, уменьшается на едини- цу и сравнивается с состоянием ноль. При достижении счетчиком-этого состояния, т.е. состояния, при котором на всех его выходах присутствует уровень лог.О, на выходе дешифратора 7 в момент времени t (см.фиг.5,з) появляется выходной импульс, который сбрасывает триггер 6, запрещая тем самым поступление импульсов тактовой частоты на сметчик 10. Состояние пос леднего фиксируется на уровне 0. Чем больше будет значение кода Nv, тем больше будет в результате фазовы сдвиг импульсов управления ВП. Максимальное значение кода N на выходе блока 3 вычислителя 2П , где п - разрядность кода N/y, и счетчика 10. Выходной импульс дешифратора 7 через двухканальный коммутатор 11, в зависимости от знака кода задания Nu, подается либо на выпрямительную группу ВП через выход 16 (см.фиг.5,е), либо на инверторную группу ВП через вых од 17 (см.фиг.5,ж).

На фиг.5 проиллюстрирована также работа устройства при различных значениях кода задания в выпрямительном и инверторном режимах.

Для наглядности допустим, что ЭДС нагрузки Ј О имеет постоянное значение (см.фиг.5,а). Предположим, что в период времени t$ код задания Ny 0, Так как знак кода задания и ЭДС нагрузки совпадают, то импульсы зажигания подаются на труп- пу тиристоров, работающую при данном знаке ЭДС в выпрямительном режиме. Допустим, что принятому значению ЭДС нагрузкиf Ј. О соответствует кривая 1 фиг.5 и значение кода управления Ny,. Этому значению кода управления соответствует код угла NV(t который определит угол управления ty и, следовательно, ток ТП i-cp, (см.фиг.5,б).

При изменении знака кода задания Nu на обратный (период времени ц- t5, см.фиг.5) знак ЭДС нагрузки и кода задания не будут совпадать.. Импульсы зажигания при этом будут по даваться на другую группу тиристо- ров, которая при принятом значении ЭДС нагрузки будет работать в инверторном режиме. В этом случае получим новые значения кода угла упрг-в ления N V3 и Угла управления 1}$ . Так как п блоке памяти вычислителя занесена зависимость (N,,Ng обратная зависимости тока ТП от угла управления и ЭДС нагрузки iс„ FdJ-.E), то среднее значение тока в этом случае будет сохранено. Ибо после линеаризации нелинейной двух- параметрической зависимости i cp FClJ .E.) при любом значении ЭДС нагрузки сохраняется соотношение i ср

K;NIJ. °

На фиг.4 показан пример реализации вычислителя, в состав которого входят однокристальная ЭВМ 2 серии КР1816 ВЕ51 и элемент памяти на запоминающем устройстве КР537 РУ8. Двухканальный коммутатор (см.фиг.7) состоит из логических элементов И- НЕ, общий вход которых является входом двунаправленного коммутатора, стробирующий вход одного из элементов И-НЕ подключен прямо к входу управления 12 двухканального коммутатора, а стробирующий вход второго логического элемента подключен к нему через инвертор. Двухканальный коммутатор 11 пропускает импульсы управления ТП, поступающие на его вход с выхода дешифратора 7, на один из выходов 18 или 19 в зависимости от сигнала на входе 12.

Остальные блоки предлагаемого устройства реализованы на следующих элементах: суммирующий счетчик 10 и дешифратор 7 на микросхемах К155 ИЕ7, причем выходом дешифратора является выход переноса счетчика, находящегося в старшей позиции; RS-три rep K155 ТМ2; элемент 8 И - К155 ЛАЗ элемент задержки k - К155 АГЗ.

Технический эффект от внедрения предлагаемого изобретения состоит в том, что заявляемое устройство

.обеспечивает получение линейной ста- тической характеристики ТП как в области непрерывных, так и в области прерывистых токов, в отличие от прототипа, обеспечивающего линеаризацию только в области непрерывного тока. К тому же точность линеаризации характеристик ТП у заявляемого устройства выше, чем у прототипа, поскольку в заявляемом устройстве учитывается зависимость тока преобразователя от двух переменных - угла управления и ЭДС нагрузки, у прототипа

используется зависимость от одной переменной - угла управления. При этом максимально достижимое увеличение точности линеаризации при боль- шом диапазоне изменения ЭДС составляет около 50%. Точность линеаризации ограничивается лишь приемлемым объемом блока памяти и при данном объеме ПЗУ, равном Кх8, не ниже 2%. Все это позволяет увеличить полосу пропускания и улучшить динамические характеристики привода, а при использовании на базовом объеме позволяет повысить производительность станка.

Формула изобретения

Устройство для управления тирис- торным преобразователем, содержащее элемент памяти, счетчик, выход которого соединен с входом дешифратора, элемент задержки, вход которого соединен с входом синхронизации устройства, а выход - со стробирующим г входом счетчика и S-входом RS-три - гера, R-вход которого соединен с выходом дешифратора, элемент И, первый вход которого соединен с прямым выходом RS-триггера, второй вход - с тактовым входом устройства, и выход - со счетным входом счетчика, отличающееся тем, что, с целью повышения точности и линейности характеристики устройства в раз- личных режимах работы, в него введе-

ны вычислитепь, сумматор управляемы и инвертор кода, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и двунаправленный коммутатор, выходы которого являются выходами устройства, управляющий вход коммутатора соединен со знаковым входом кода задания устройства, а информационный вход - с выходом дешифратора, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно со знаковыми входами кода задания и кода ЭДС устройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющим входом инвертора кода и входом переноса сумматора, информационные входы инвертора кода подключены к информационным входам кода ЭДС устройства, а выходы инвертора кода соединены с информационными входами сумматора, выходы которого подключены к первой группе 1 информационных входов вычислителя, вторая группа 12 информационных входов вычислителя подключена к информацией ным входам кода задания устройства, вход прерывания TNT вычислителя соединен с входом синхронизации устройства, магистраль адреса-данных вычислителя соединена с входами-выходами элемента памяти и входами запи-- си DO-счетчика, причем вычислитель обеспечивает пропорциональную функциональную зависимость между сигналом на информационном входе 12 и током тиристорного преобразователя.

Фие.1

--J -J

Ni

Генератор

HHQ

sML

/ шифратор аЭрбСй

fcVW

Порт bbo5g- ЬыЬоЭа

ft йа ЬхлЗ элемента .О С ЬымЗй цемент

a

.

twnssvM

SUV/SS M

З ЗгзсЬ

К455/1ДЗ

Г

..

teuwq t on opalI1

фи2.7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для линеаризации регулировочной характеристики тиристорного преобразователя | 1980 |

|

SU909791A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-11-23—Публикация

1990-03-04—Подача