(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1991 |

|

RU2030831C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Устройство для передачи информации | 1990 |

|

SU1753615A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| УПРАВЛЯЮЩИЙ АВТОМАТ | 2011 |

|

RU2475816C1 |

| Преобразователь кода во временной интервал | 1990 |

|

SU1753512A1 |

| Устройство для передачи и приема данных | 1987 |

|

SU1510105A1 |

Сущность изобретения: устройство содержит п кодирующих блоков 2, делитель 4 частоты, формирователь 5 импульсов, счетчик 6, дешифратор 8, две группы элементов НЕ 9 и 12, две группы триггеров 10 и 13, элемент ИЛИ 11. 3 ил.

00

о

тшЛ

4D Ю

Изобретение касается передачи цифровой информации и может быть использовано, например, в телеграфной и телефонной связи.

Известно устройство для передачи коротких сообщений, содержащее сумматоры по модулю два, информационные регистры сдвига, хронизирующие регистры сдвига, счетчики, триггеры, дешифраторы, клапаны, устройство выделения сигнала окончания ввода информации, схему ввода исходного состояния (авт,св. СССР чl 431638, кл. Н 04 L3/00).

Недостаток данного устройства в том, что оно не может обеспечить передачу непрерывных потоков цифровой информации от нескольких источников,

Наиболее близким техническим решением к предлагаемому является устройство для передачи дискретных сообщений, содержащее два клапана, информационный регистр сдвига, пять сумматоров по модулю два, два хронизирующих регистра сдвига, два блока ввода исходной комбинации, дешифратор, блок управления, реализованный на задающем генераторе, пяти клапанах, трех элементах ИЛИ, пяти триггерах, трех счетчиках, коммутаторе, дешифраторе, и формирователи псевдослучайной последовательности, каждый из которых реализован на двух сумматорах по модулю два, клапане и регистре сдвига (авт.св. СССР № 1195471, кл. Н 04 L 17/02),

Недостатки данного устройства - обязательное разделение в рабочем цикле ввода информации и считывания ее в канал связи и громоздкая структура построения.

Целью изобретения является -повышение помехозащищенности за счет организации передачи непрерывных потоков цифровой информации от нескольких-источников и упрощения структуры построения.

Поставленная цель достигается тем, что в устройство для передачи цифровой информации, содержащее первую группу триггеров, элемент ИЛИ, счетчик и дешифратор, введены дополнительно вторьге группы триггеров, первая и вторая группы элементов НЕ, первые и вторые кодирующие блоки, делитель частоты и формирователь импульсов, выход которого соединен с Rвходом счетчика, выходы которого подключены соответственно к входам дешифратора, выходы которого соединены с входами соответствующих первых и вторых групп элементов НЕ, выходы которых подключены к R- и С-входам соответственно первых и вторых групп триггеров, D-входы которых подключены к выходам соответственно первых и вторых кодирующих блоков.

первые управляющие входы которых обьединены и подключены к входу формирователя импульсов и к выходу делителя частоты, вход которого подключен к С-входу счетчика; выходы первых и вторых триггеров соединены с входами элемента ИЛИ; вторые управляющие входы первых и вторых кодирующих блоков объединены и являются управляющим входом устройства,

0 информационными входами которого являются информационные входы первых и вторь х кодирующих блоков; вход делителя частоты является Тактовым входом устройства, выходом которого является выход эле5 мента ИЛИ,

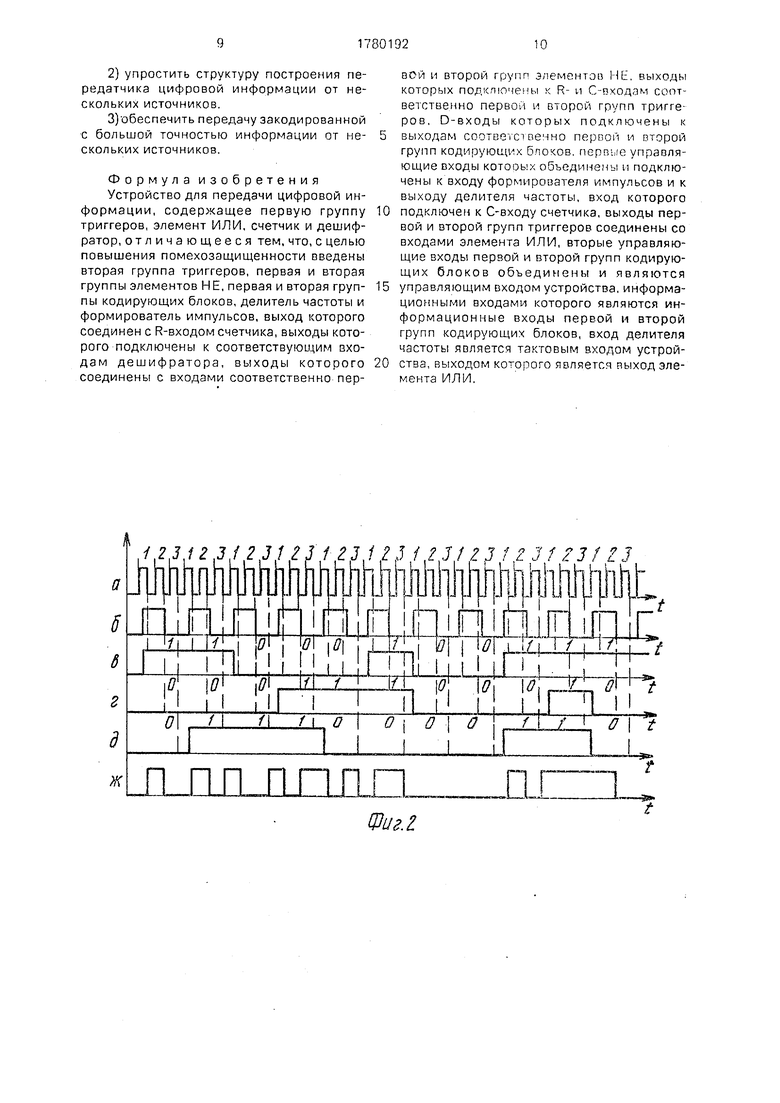

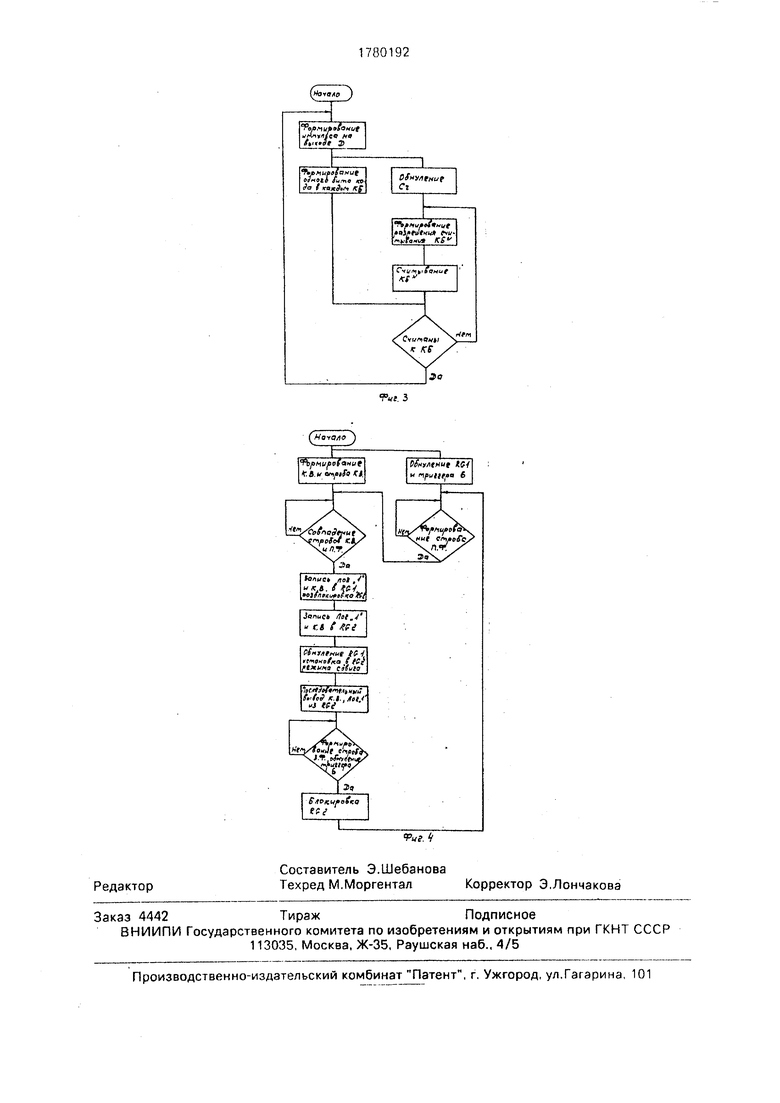

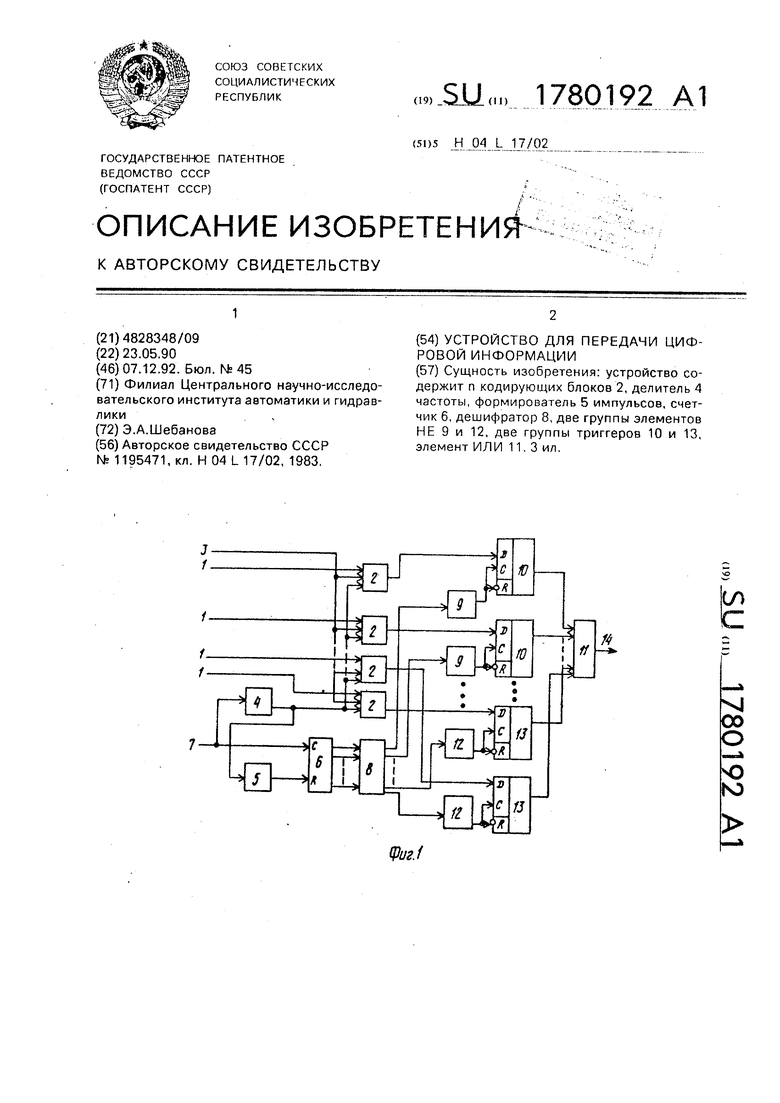

На фиг.1 представлена функциональная схема устройства для передачи цифровой информации; на фиг.2 - временные диаграммы; на фиг.З - алгоритм работы устрой0 ства для передачи цифровой информации,

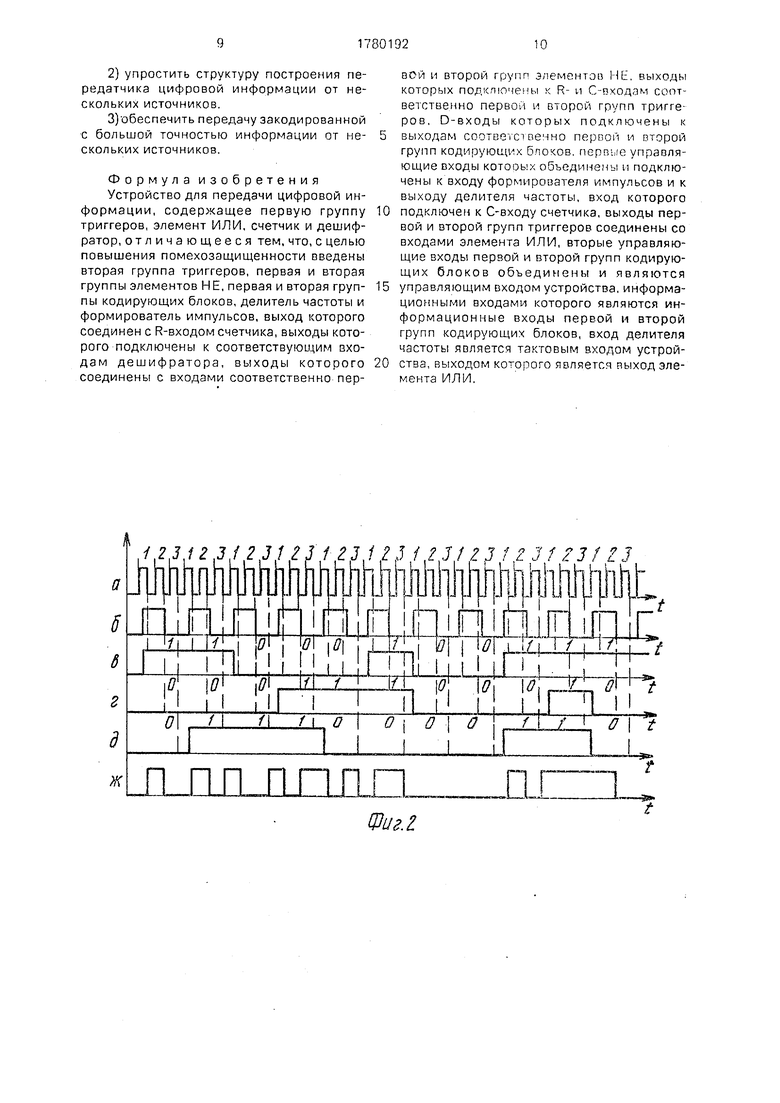

поясняющий его работу; на фиг,4 -алгоритм

работы кодирующего устройства по авт.св.

N51530060, поясняющий организацию кода,

.получаемого на выходе кодирующего уст5 ройства,

Устройство для передачи цифровой информации содержит кодируюш,ие блоки 2, делитель 4 частоты, формирователь 5 импульсов, счетчик 6, дешифратор 8, первые и

0 вторые группы элементов НЕ 9 и 10, первые и вторые группы триггеры 10 и 13 элемент ИЛИ 11,

На фиг.1 обозначены также информационные входы 1 устройства, управляющий 3

5 и тактовый 7 входы, выход 14 устройства.

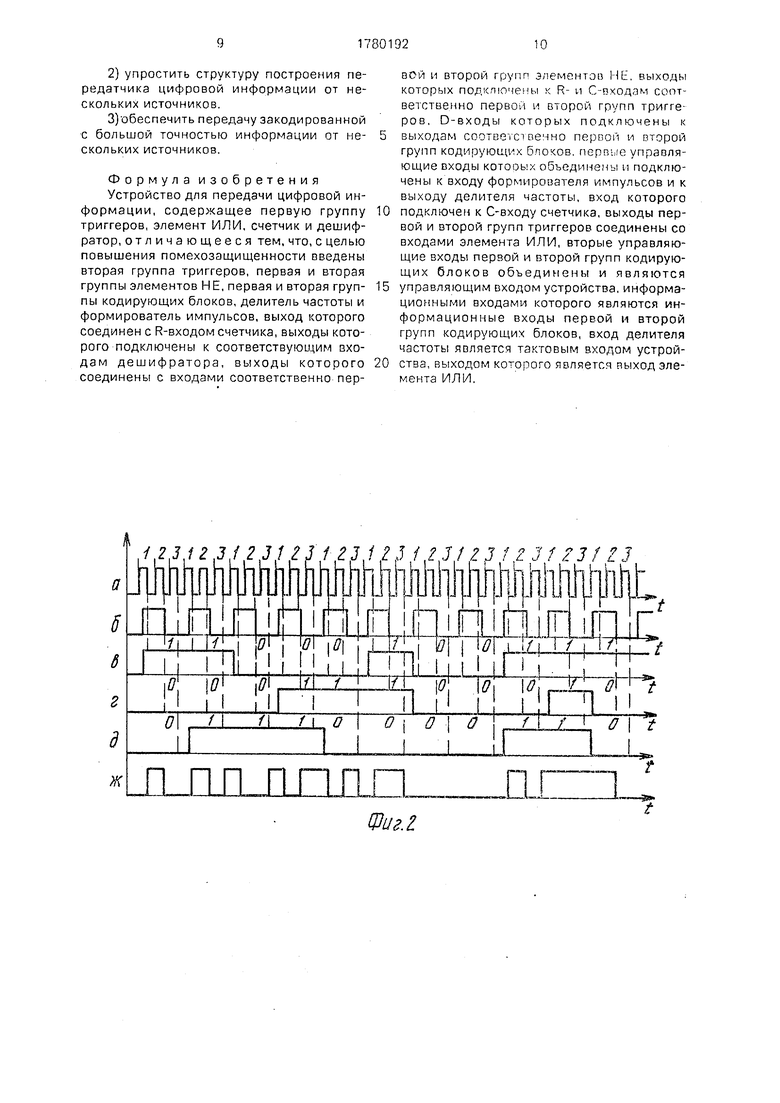

На фиг,2 соответствующими индексами обозначены следующие сигналы: а - сигнал на тактовом входе 7, б - сигнал на выходе делителя 4 частоты, в - сигнал на выходе

0 первого кодирующего блока 2, г - сигнал на

выходе второго кодирующего блока 2, д сигнал на выходе третьего кодирующего

блока 2, ж-сигнал на выходе 14 устройства.

Информационные входы устройства 1

5 подключены соответственно к информационным входам первых и вторых кодирующих блоков 2. Первые управляющие входы первых и вторых кодирующих блоков 2 объединены с управляющим входом 3 устройства.

0 Вторые управляющие входы первых и вторых кодирующих блоков 2 объединены с выходом делителя 4 частоты и входом формирователя 5 импульсов. Выход формирователя 5 импульсов соединен с R-входом

5 счетчика 6, С-вход счетчика 6 соединен с входом делителя 4 частоты и тактовым входом 7. Выходы счетчика 6 соединены соответственно с входами дешифратора 8. Выходы дешифратора 8 соединены соответственно с входами первых и вторых групп

элементов НЕ 9 и 12. Выходы первых и вторых групп элементов НЕ 9 и 12 соединены соответственно с С- и R-входами первых и вторых групп триггеров 10 и 13. D-входы первых и вторых групп триггеров 10 и 13 соединены соответственно с выходами первых и вторых кодирующих блоков 2. Выходы первых и вторых групп триггеров 10 и 13 соединены соответственно с входами элемента ИЛИ 11. Выход элемента ИЛИ 11 соединен с выходом 14 устройства.

На тактовый вход 7 подана стабилизированная частота K fraxT, где К - число каналов, с которых организуется передача цифровой информации.

В делителе 4 частоты организовано деление тактовой частоты с тактового входа 7 на число каналов К.

Счетчик 6 - двоичный счетчик, срабатывает по задним фронтам импульсов частоты KfiaKT.

В качестве формирователя 5 импульсов - формирователя по переднему фронту использованы два инвертора и микросхема 134 ХЛЗ.

В качестве кодирующих блоков 2 использованы устройства по авт.св. СССР № 1530060, кл. Н 03 М 7/00.

Все кодирующие блоки 2 построены на счетчиках кода времени одинаковой разрядности.

На управляющий вход 3 подана частота заполнения счетчиков кода времени кодирующих блоков 2 (см. авт.св, INh 1530060). Первый управляющий вход в каждом кодирующем блоке 2 (авт.св. № 1530060) обозначен как третий вход управления 14.

Второй управляющий вход в каждом кодирующем блоке 2 (авт.св. Мг 1530060) обозначен как второй вход управления 13. Там же еще указан первый вход управления 14, но на фиг.1 данного описания он не показан, так как в названном описании оговорено, что на первый вход управления 14 приводится уровень логической единицы.

Работа устройства осуществляется следующим образом.

При включении питания в начальный момент времени обнуляются первые и вторые кодирующие блоки 2 (первые регистры сдвига и вторые триггеры в кодирующих блоках 2 - см, описание изобретения к авт.св. № 1530060), счетчик 6, первые и вторые группы триггеров 10 и 13 (обнуление первых и вторых кодирующих блоков 2, счетчика 6, первых и вторых групп триггеров 10 и 13 на фиг.1 не показано). На информационные входы первых и вторых кодирующих блоков 2 подаются непрерывные

потоки цифровой мифоргиации от К источников. В первых и вторых кадирую Ц11х блоках 2 потоки цифропой и,чформги.;|;:1 м::,трерыпио преобразуете.) з з-зкодпрозаипые зквмваленты информации. По переднему фронту импульса с выхода делителя 4 частоты на выход каждого кодирующего блока 2 поступает один бит закодированного эквивалента информации. По переднему фронту того

же импульса на выходе формирователя 5 импульсов организуется короткий импульс, обнуляющий счетчик 6. Послэ этого по заднему фронту первого тактового импульса с тактобого входа 7 на первом выходе дешифратора 8 организуется логический нуль сигнал разрешения считывания первого кодирующего блока 2, по которому бит информации с первого кодирующего блока 2, записывается в первую группу триггеров 10

и появляется на первом аходе элемента ИЛИ 11 и выходе 14 устройства. По заднему фронту второго тактового импульса на втором выходе дешифратора 8 формируется сигнал разрешения считывания второго кодирующего блока 2, первый триггер 10 из первой группы сбрасывается в нуль, бит информации с выхода второго кодирующего блока 2 считывается на выход 14 устройства. Аналогично по задним фронтам третьего,

четвертого, ...К-ого тактовых импульсов на выход 14 устройства считываются биты закодированных эквизалентов информации соответственно с третьего, четвертого, ,,.Кого кодируюш,их блоков 2. По переднему

фронту следующего импульса с выхода делителя 4 частоты весь цикл работы повторяется сначала м на выход 14 устройства последовательно считываются вторые биты закодированных эквивалентов информации

К источников. По передним фронтам всех последующих импульсов с выхода делмтеля 4 частоты на выход 14 устройства последовательно считываются третьи, четвертые и т.д. биты закодированных эквивалентов информации К источников.

На фиг.2 на временной диаграмме показан пример организации передачи информации от трех источников, когда

информация от первого источника в первом кодирующем блоке преобразуется в код 11000100111 (см, фиг.2в), от второго источника во втором кодирующем блоке - в код 00011100010 (см. фиг.2г), от третьего источника S третьем ,одирующем блоке - в код 01110000110 (см. фиг.2д).

На фиг.З в алгоритме работы устройства для передачи цифровой информации приняты следующие условные обозначения: Д делитель 4 частоты; КБ - кодирующий блок 2: Сч - счетчик 6; N-1...K.

По алгоритму работы устройства для передачи цифровой информации по переднему фронту первого импульса на выходе D обнуляется Сч, а на выходе первого КБ появляется логическая единица (см, фиг,2в), на выходе второго КБ - логический нуль (см. фиг.2г), на выходе третьего КБ - логический нуль (см.фиг.2д). Полученная на выходах трех КБкомбинация 100 будет держаться до переднего фронта второго импульса на выходе D (см. фиг.26). После обнуления Сч по заднему фронту первого тактового импульса (см. фиг.2а) на первом выходе дешифратора 8 организуете разрс иение считывания первого КБ, в первый триггер 10 из первой группы и далее на выход устройства считывается бит единицы, по заднему фронту второго тактового импульса (см. фиг.2а) на выходе устройства считывается бит нуля при появлении разрешения считывания на втором выходе дешифратора 8, по заднему фронту третьего тактового импульса (см. фиг.2а) на выход устройства считывается бит нуля при появлении разрешения считывания на третьем выходе дешифратора 8. Далее весь цикл повторяется сначала - по переднему фронту второго импульса на выходе D на выходах трех КБ появляется комбинация 101 и по заднему фронту четвертого тактового импульса на выход устройства считывается бит единицы, по заднему фронту пятого тактового импульса - бит нуля, по заднему фронту шестого тактового импульса - бит единицы. Цикл работы повторяется и на третий, четвертый и все последующие импульсы на выходе D.

На фиг.4 в алгоритме работы кодирующего блока приняты следующие условные обозначения:

К.В. - код времена на выходе счетчика 11,

RG1 - первый регистр 1 сдвига,

RG2 - второй регистр 2 сдвига,

П.Ф,- передний фронт импульса на входе 15,

З.Ф. задний фронт импульса на входе 15.

Для примерз хсдлруй.ся поступаюш,ая на вход кодирующего блока последовательность - 1011 (см. временные диаграммы на фиг.2 в описании Кодирующего устройства по авт.св. № 1530060) - или два импульса, причем передний фронт первого импульса приходит, когда на выходах счетчика кода времени готова комбинация 01011, а передний фронт второго импульса приходит, когда на выходах счетчика кода времени готова комбинация 00101. По переднему фронту первого импульса в регистр RG1 записывается комбинация 101011 (логическая единица в шестом разряде добавляется к коду времени в регистре RG1),

далее по переднему фронту первого тактового импульса комбинация 101011 переписывается в регистр RG2. Появившаяся на выходе шестого разряда регистра RG2 логическая единица обнуляет регистр RG1, а регистр RG2 переводит в режим сдвига с занесением логической единицы. Далее по переднему фронту второго тактового импульса на выходе шестого разряда регистра RG2 - выходе кодирующего блока - появляется логический нуль, по третьему тактовому импульсу - логическая единица, по четвертому - логический нуль, по пятому логическая единица, по шестому - логическая единица остается, по седьмому - логическая единица остается, Между седьмым и восьмым тактовыми импульсами первый входной импульс сбрасывается в нуль - формируется строб заднего фронта, из-за которого с приходом восьмого тактового

импульса регистра RG2 обнуляется и на выходе кодирующего блока появляется логический нуль, который держится на нем до прихода шестнадцатого тактового импульса, так как между пятнадцатым и шестнадцатым импульсами появляется передний фронт второго входного импульса и в регистр RG1 записывается новая комбинация 100101. По приходу шестнадцатого тактового импульса комбинация 100101 записывается в регистр RG2. На выходе кодирующего блока появляется логическая единица, регистр RG2 переводится в режим сдвига и на семнадцатый тактовый импульс на выходе кодирующего блока появляется логический

нуль, на восемнадцатый тактовый импульс остается логический нуль, на девятнадцатый тактовый импульс появляется логическая единица, на двадцатый тактовый импульс она сбрасывается в нуль, на двадцать первый тактовый импульс опять появляется логическая единица и держится на выходе кодирующего блока до прихода тридцатого импульса, так как между двадцать девятым и тридцатым тактовыми импульсами приходит задний фронт второго входного импульса, регистр RG2 обнуляется и, начиная стридцатого тактового импульса, на выходе кодирующего блока сохраняется логический нуль.

Предлагаемое устройство для передачи

цифровой информации позволяет:

1) обеспечить передачу непрерывных потоков цифровой информации от нескольких источников:

2) упростить структуру построения передатчика цифровой информации от нескольких источников.

3)обеспечить передачу закодированной с большой точностью информации от нескольких источников.

Формула изобретения Устройство для передачи цифровой информации, содержащее первую группу триггеров, элемент ИЛИ, счетчик и дешифратор, отличающееся тем, что, с цел ью повышения помехозащищенности введены вторая группа триггеров, первая и вторая группы элементов НЕ, первая и вторая группы кодирующих блоков, делитель частоты и формирователь импульсов, выход которого соединен с R-входом счетчика, выходы которого подключены к соответствующим входам дешифратора, выходы которого соединены с входами соответственно пер

вой и второй групп элементов 14Е. выходы которых подключены к R- и С-входам соответственно первой и второй групп триггеров. D-входы которых подключены к выходам соответственно пероой и второй групп кодирующих блоков, первые управляющие входы КОТОРЫХ объединены и подключены к входу формирователя импульсов и к выходу делителя частоты, вход которого подключен к С-входу счетчика, выходы первой и второй групп триггеров соединены со входами элемента ИЛИ, вторые управляющие входы первой и второй групп кодирующих блоков объединены и являются управляющим входом устройства, информационными входами которого являются информационные входы первой и второй групп кодирующих блоков, вход делителя частоты является тактовым входам устройства, выходом которого является выход элемента ИЛИ. /,Z,J,f,J,/.r J.//J /..J,//,J /.f,J/.J//J//J//J Itpllltfltltli r-yrn o, n 1. 0 0 0 и П ПП ППП1 HiF fiHv 0 I t .01 Фиг2

| Устройство для передачи дискретных сообщений | 1983 |

|

SU1195471A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-12-07—Публикация

1990-05-23—Подача