от со ел

к

Изобретение относится к импульсной технике и может быть использовано в системах приемопёредачи цифровой информации.

Известно устройство, содержащее счетчик импульсов, элементы И, блок сравнения кодов, регистры, триггеры.

Известен преобразователь код - временной интервал, содержащий регистры, триггеры, два элемента И, счетчик импульсов, блок сравне ния кодов, сумматор, группу элементов И, формирователь импульсов, блок коррекции, шины кода числа периодов, элемент ИЛИ, шину сброса.

Недостаток данных устройств в том, что они не могут декодировать организуемый по передним фронтам импульсов цифровой эквивалент информации с выхода кодирующего устройства.

Наиболее близким к предлагаемому является преобразователь кода во временной интервал, содержащий первый и второй регистры, блок элементов 2И-ИЛИ, блок сравнения кодов, первый и второй счетчики импульсов, генератор импульсов, триггер, блок начальной установки, коммутатор, первый, второй и третий элементы И-НЕ, элемент 2И-ИЛИ, элемент И, элемент НЕ, элемент ИЛИ, шины входного кода, кода задержки, управления и выходные.

Недостаток данного устройства в том, что оно не может преобразовывать последовательность кода, организуемую в кодирующем устройстве(а вт. св. N21530060, кл. Н 03 М 7/00).

Целью изобретения является расширение области применения за счет возможности декодирования последовательности кода.

Поставленная цель достигается тем, что в преобразователь кода во временной интервал, содержащий первый и второй регистры, элемент НЕ, счетчик импульсов, выходы которого соединены с соответствующими первыми входами блока сравнения, первый элемент ИЛИ, выход которого соединен с первым входом триггера, выход которого является выходом устройства, введены дополнительно второй и третий элементы ИЛИ, второй элемент НЕ, первый, второй и третий формирователи коротких импульсов, причем первый вход первого регистра является информационным входом устройства, второй вход первого регистра объединен с первым входом второго регистра, входом первого формирователя коротких импульсов и является первым управляющим входом устройства, первый вход счетчика импульсов соединен с входом второго формирователя коротких импульсов и является вторым управляющим входом устройства, с первого по N-й выходы первого регистра соединены соответственно с вторыми входами блока сравнения и

одноименными входами второго элемента ИЛИ, (N+1}-u выход первого регистра подключен через первый элемент НЕ к первому входу третьего элемента ИЛИ, (N+2H2N+1)- е выходы первого регистра соединены с соответствующими вторыми входами третьего элемента ИЛИ, выход которого соединен с первым входом первого элемента ИЛИ. выход блока сравнения подключен к второму входу первого элемента ИЛИ, выход второго

формирователя коротких импульсов соединен с третьим входом первого элемента ИЛИ, выход первого формирователя коротких импульсов соединен с вторым входом счетчика импульсов, второй и третий входы

второго регистра подключены соответственно к выходу первого э лемента ИЛИ и к шине логической единицы, выход второго регистра соединен через второй элемент НЕ с (М-И)-м входом второго элемента ИЛИ, выход которого подключен через третий формирователь коротких импульсов к второму входу триггера.

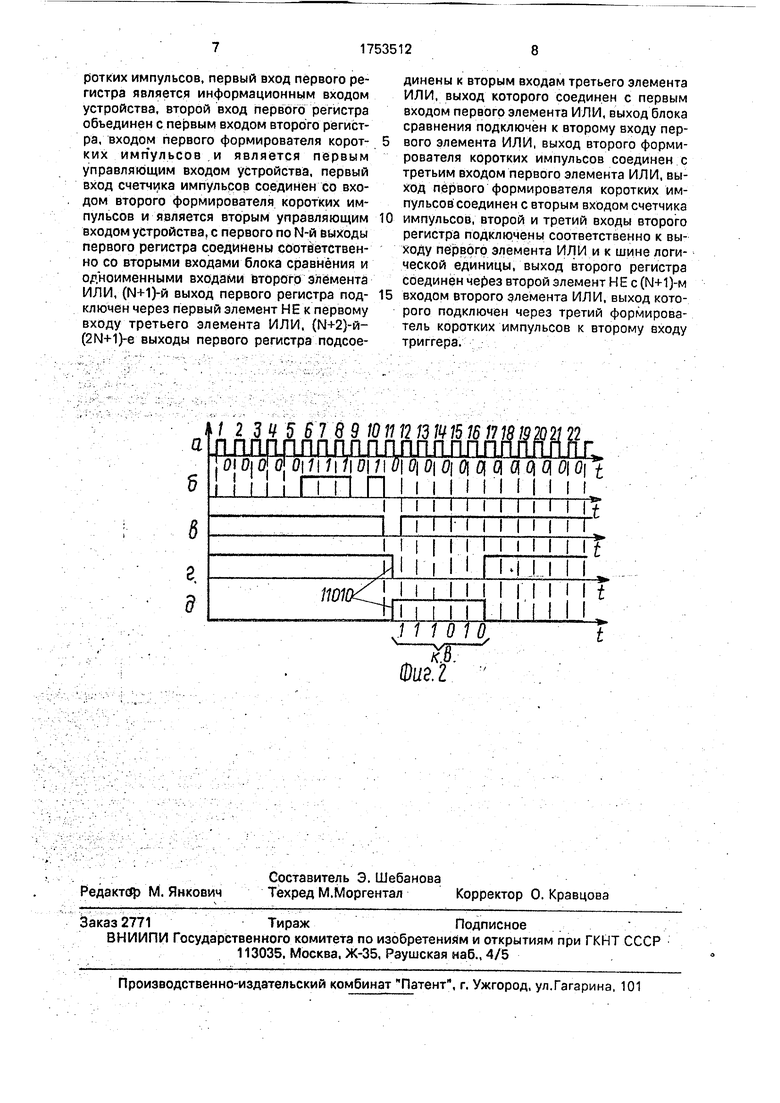

На фиг. 1 представлена функциональная схема преобразователя кода во временной

интервал; на фиг.2 - временные диаграммы его работы.

Преобразователь кода во временной интервал содержит первый и второй регистры 1 и 2, счетчик 3, блок 4 сравнения кодов,

первый, второй и третий элементы ИЛИ 5-7. первый и второй элементы НЕ 8 и 9, триггер 10, первый, второй и третий формирователи 11-13 коротких импульсов.

На фиг.2 соответствующими индексами обозначены следующие сигналы: а - сигнал на первом управляющем входе; б - сигнал на информационном входе устройства; в - сигнал на выходе третьего элемента ИЛИ 7; г-сигнал на выходе второго

регистра 2; д - сигнал на выходе устройства.

На первый управляющий вход подается тактовая частота fiaxi. на информационный вход устройства поступает последовательность кода.

Счетчик 3 - двоичный счетчик. Частота заполнения его Ттакт М подается на второй управляющий вход (. N - разрядность счетчика). Счетчик 3 срабатывает по задним

фронтам импульсов частоты Ттакт М и вырабатывает между двумя импульсами синхронизирующей тактовой частоты fraxr. M кодовых комбинаций - коды времени.

Тактовая частота fiaxr и частота запой- i нения счетчика 3 должны быть от одного источника в целях синхронизации.

Счетчик 3 должен быть той же разрядности, что и счетчик кода времени в кодиру- ющем устройстве, организовавшем последовательность кода.

Первый и второй регистры 1 и 2 должны быть подключены к режиму последовательного занесения со сдвигом.

В первом формирователе 5 коротких импульсов по переднему фронту каждого тактового импульса и во втором формирователе 12 коротких импульсов по переднему фронту каждого импульса заполнения счетчика 3 организуется соответственно строб обнуления счетчика 3 и строб готовности кода времени.

В третьем формирователе 13 коротких импульсов по заднему фронту импульса на выходе второго элемента ИЛИ 6 организуется разрешение формирования заднего фронта на выходе преобразователя.

В качестве третьего формирователя 13 использована микросхема 134ХЛЗ, а в качестве первого и второго формирователей 11 и 12 - инвертор и микросхема 134ХЛЗ.

Работа преобразователя кода во временной интервал осуществляется следующим образом.

При включении питания в начальный момент времени обнуляются первый регистр 1 и триггер 10. В счетчике 3 начинают формироваться коды времени, дифференцирующие М отрезков времени между каждыми двумя тактовыми импульсами. При поступлении последовательности кода на информационный вход по передним фронтам тактовых импульсов в первом регистре 1 начинают сдвигаться биты последовательности кода. В каждый из М отрезков текущего времени между двумя тактовыми импульсами в блоке 4 сравнения кодов осуществляется поразрядное сравнение кодов времени с комбинацией на выходах N младших разрядов первого регистра 1. В момент сравнения на выходе блока 4 сравнения кодов формируется логический нуль.

Когда на выходах (N+1H2N+1) разрядов первого регистра 1 появляется маркер I (комбинация из N нулей, затем одной единицы) на выходе третьего элемента ИЛИ 7 и первом входе первого элемента ИЛИ 5 появляется логический нуль - сигнал разрешения формирования переднего фронта.

Наличие этого сигнала при сравнении кода времени с комбинацией на выходах N младших разрядов первого регистра 1 организует в момент появления короткого отрицательного импульса на выходе второго

формирователя 12 коротких импульсов логический нуль на выходе первого элемента ИЛИ 5, первом входе триггера 10 и втором входе второго регистра 2. В результате триггер 10 перебрасывается в единичное состояние - формируется передний фронт асинхронного сигнала на выходе преобразователя, а второй регистр 2 обнуляется и на его выходе появляется нуль- запрет формирования заднего фронта асинхронного сигнала на выходе преобразователя.

На каждый следующий тактовый импульс во втором регистре 2 начинает сдвигаться логическая единица. Через (N+1) тактовых импульсов она появляется на выходе второго регистра 2 - снимается запрет формирования заднего фронта асинхронного сигнала на выходе преобразователя. (После формирования переднего фронта асинхронного сигнала (N+1) сдвигов в первом регистре 1 обеспечивают очищение выходов (N+1) младших разрядов его от бит кода времени). Если в этот момент на N младших разрядах первого регистра 1 и соответственно N первых входах второго элемента ИЛИ б обнаружится комбинация из N нулей - маркер 2, то на второй вход триггера 10 поступит короткий отрицательный импульс, который обнулит его - на выходе преобразователя организуется задний фронт

асинхронного сигнала.

Если в момент снятия сигнала запрета на выходах N младших разрядов первого регистра 1 не обнаружится комбинация из N нулей, то короткий отрицательный импульс на втором входе триггера 10 и соответственно задний фронт асинхронного сигнала на выходе преобразователя сформируется позже, когда такая комбинация появится.

В последующем с появлением маркера I на (N+1)-(2N+1) выходах первого регистра 1 весь цикл работы преобразователя повторится сначала.

Формула изобретения

Преобразователь кода во временной интервал, содержащий первый и второй регистры, первый элемент НЕ, счетчик импульсов, выходы которого соединены с

соответствующими первыми входами блока сравнения, первый элемент ИЛИ, выход которого соединен с первым входом триггера, выход которого является выходом устройства, отличающийся тем, что, с целью

расширения области применения за счет возможности декодирования последовательного кода, в него введены второй и третий элементы ИЛИ, второй элемент НЕ, первый, второй и третий формирователи коротких импульсов, первый вход первого регистра является информационным входом устройства, второй вход первого регистра объединен с первым входом второго регистра, входом первого формирователя коротких импульсов и является первым управляющим входом устройства, первый вход счетчика импульсов соединен со входом второго формирователя коротких импульсов и является вторым управляющим входом устройства, с первого по N-й выходы первого регистра соединены соответственно со вторыми входами блока сравнения и одноименными входами второго элемента ИЛИ, (N+IJ-й выход первого регистра подключен через первый элемент НЕ к первому входу третьего элемента ИЛИ, (1М+2)-й- (2N+1)-e выходы первого регистра подсоединены к вторым входам третьего элемента ИЛИ, выход которого соединен с первым входом первого элемента ИЛИ, выход блока сравнения подключен к второму входу первого элемента ИЛИ, выход второго формирователя коротких импульсов соединен с третьим входом первого элемента ИЛИ, выход первого формирователя коротких импульсов соединен с вторым входом счетчика

импульсов, второй и третий входы второго регистра подключены соответственно к выходу первого элемента ИЛИ и к шине логической единицы, выход второго регистра соединен через второй элемент НЕ с (М+1)-м

входом второго элемента ИЛИ, выход которого подключен через третий формирователь коротких импульсов к второму входу триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Преобразователь кода во временной интервал | 1990 |

|

SU1774498A1 |

| Преобразователь двоичного кода во временной интервал | 1990 |

|

SU1714811A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

Изобретение относится к области импульсной техники и может быть использовано в системах приемопередачи цифровой информации. Целью изобретения является расширение области применения за счет возможности декодирования последовательного кода. Устройство содержит первый и второй регистры 1,2, счетчик 3, блок 4 сравнения кодов, первый, второй, и третий элементы 5,6,7 ИЛИ, первый и второй элементы 8,9 НЕ, триггер 10, первый,второй и третий формирователи коротких импульсов. 2 ил.

| Преобразователь код-временной интервал | 1985 |

|

SU1305865A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1275776A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-08-07—Публикация

1990-02-28—Подача