(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1721836A2 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для приема и передачи цифровой двоичной информации | 1989 |

|

SU1693734A1 |

| Устройство для передачи и приема данных | 1990 |

|

SU1786678A1 |

Изобретение относится к радиотехнике, а именно к области последовательной передачи данных методом широтно-импульсной манипуляции. Целью изобретения является повышение достоверности передаваемой информации. Для достижения, цели & устройство, содержащее тактовый генератор 1, регистр 3 сдвига, делитель 4 частоты, мультиплексор 5, формирователь 6 коротких импульсов, элемент И 7, счетчик 8, D-триггер 10, RS-триггер 12, дешифратор 9, блок 11 задержки, источник 2 информации, введены формирователь 15 коротких импульсов, счетчик 14 и элемент ИЛИ 13, что обеспечи- вает формирование импульсов синхронизации через заданное число переданных полей данных. 2 ил.

xj

сл со о

СП

Изобретение относится к области последовательной передачи цифровых данных методом широтно-импульсной манипуляции.

Известно устройство для передачи цифровой информации, основанное на передаче разделенных паузами группы информационных импульсов, модулированных по длительности значения бит информации и группы импульсов синхронизации. Для передачи используют три типа импульсов с длительностью Т1 Т2 ТЗ. Импульсы длительностью Т1 и Т2 кодируют значения передаваемых бит информации. Импульсы длительностью ТЗ служат для синхронизации приемника с передатчиком и разделения отдельных полей информации. При отсутствии информации передают непрерывно импульсы синхронизации. Устройство содержит тактовый Генератор, регистр сдвига, мультиплексор, элемент И, D-триг- гер, блок задержки, делитель частоты, источник информации,

Недостатком известного устройства является то, что между полями информации оно передает обязательно импульсы синхронизации, даже если очередные данные готовы к передаче и приемник и передатчик синхронизированы между собой, что снижает пропускную способность устройства при передаче байтами на 30%.

Наиболее близким по технической сущности к предлагаемому является устройство для передачи данных, содержащее последовательно соединенные тактовый генератор, делитель частоты, мультиплексор и первый формирователь короткого импульса, последовательно соединенные источник информации и регистр сдвига, последовательно соединенные элемент И, первый счетчик, дешифратор, D-триггер и блок задержки, RS-триггер, выход формирователя короткого импульса соединен с первым выходом делителя частоты, выход RS-триггер соединен с вторым входом D-триггера, третий вход которого соединен с общей шиной, выход регистра сдвига соединен с первым управляющим входом мультиплексора, выход мультиплексора является выходом устройства и соединен с первым входом элемента И, второй вход которого соединен с вторым управляющим входом мультиплексора, а выход - с третьим входом регистра сдвига. Недостатком известного устройства является низкая достоверность сообщения передаваемой информации из-за возможного сбоя в работе счетчиков бит передатчика при наличии помех в питании. В известном устройстве, если темп поступления данных от источника выше темпа передачи, то импульсы синхронизации формируются лишь в моменты отсутствия информации, например в начале каждого файла. Потеря одного бита в середине файла при- водит к потере большей части информации.

Целью изобретения является повышение достоверности сообщения передаваемой информации.

Поставленная цель дос1 И ается тем, что в устройство для передачи информации, содержащее источник информации, первый и второй выходы которого соединены соответственно с первым и вторым входами регистра сдвига, третий вход которого соединен с выходом элемента М и первым входом первого счетчика, второй вход которого соединен с вторым выходом источника информации, выход первого счетчика череь

дешифратор соединен с входом источника информации и первым входом D-триггера, выход которого соединен с входом блока задержки, выход тактового генератора соединен с первым входом делителя частоты,

второй вход которого и первый вход RS- триггера соединены с выходом первого фор- мирователя коротких импульсов, вход которого и первый вход элемента И соединены с выходом мультиплексора, который

является выходом устройства, первый, второй и третий выходы делителя частоты соединены соответственно с первым, вторым и третьим входами мультиплексора, первый выход делителя частоты соединен с вторым

входом RS-триггера, выход которого соединен с вторым входом D-триггера, третий выход делителя частоты соединен с четвертым входом мультиплексора, пятый вход которого соединен с выходом регистра сдвига, введены последовательно соединенные второй формирователь коротких импульсов, второй счетчик и элемент ИЛИ, причем третий выход делителя частоты соединен с входом второго формирователя, выход дешифраторз соединен с вторым входом второго счетчика, выход блока задержки соединен с вторым входом элемента ИЛИ,1 выход которого соединен с шестым входом мультиплексора и вторым входом элемента И.

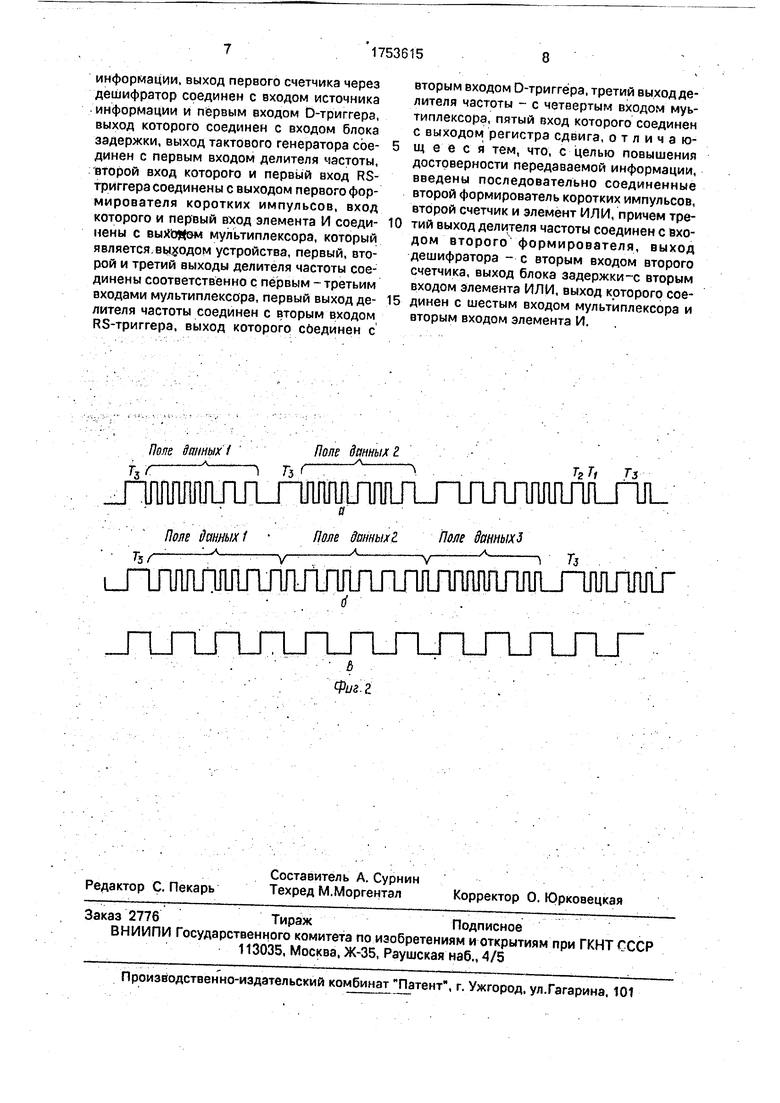

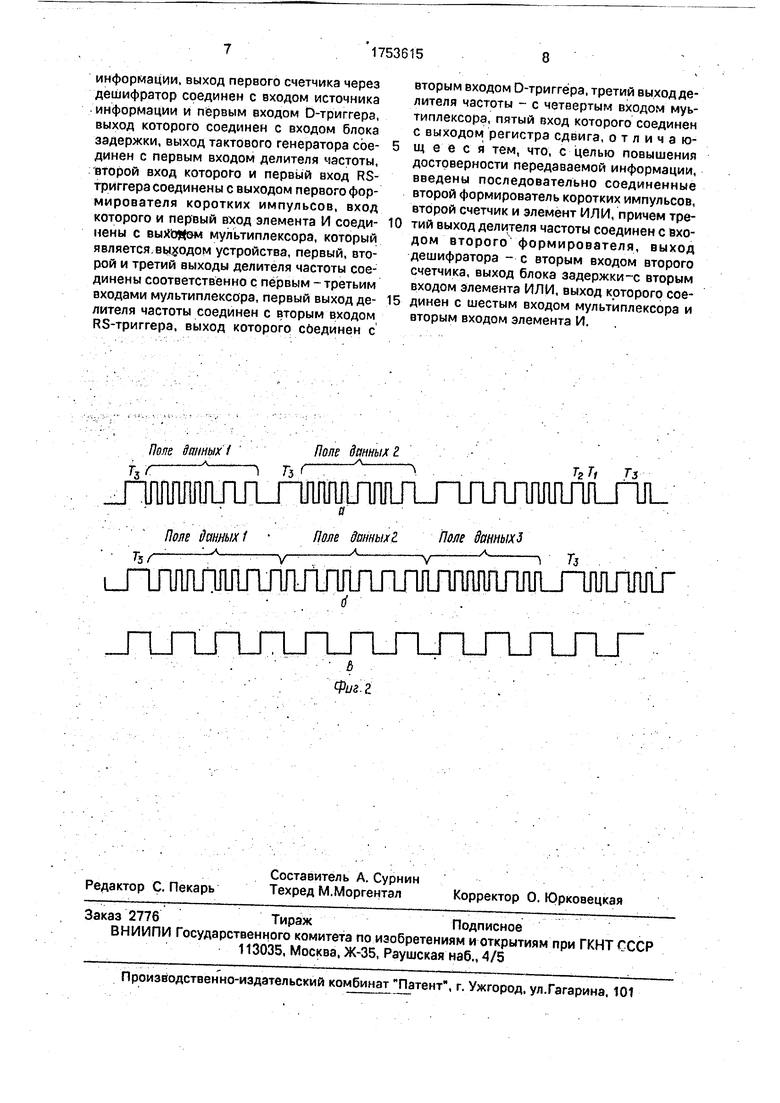

0 На фиг.1 приведена структурная электрическая схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу,

5 Устройство содержит тактовый генератор 1, источник 2 информации, регистр 3 сдвига, делитель 4 частоты, мультиплексор 5, первый формирователь 6 коротких импульсов, элемент И 7, первый счетчик 8, де- шифратор 9, D-триггер 10, блок 11

задержки, RS-триггер 12, а также элемент ИЛИ 13, второй счетчик 14, второй формирователь 15 коротких импульсов.

Устройство работает следующим образом.

Делитель 4 частоты делит входную частоту от тактопого генератора 1 и Формирует нз своих грех выходах три серии импульсов Т1.Т2.ТЗ ресничной длительности, поступающие на входы мультиплексора 5. Выбор серии импульсов и их длительность на выходе мультиплексора 5 зависят от значения сигнале), г- зго управляющих входах. С помощью формирователя б коротких импульсов по заднему фронту каждого импульса происходит сброс RS-триггера 12 и синхронизация счетчиков делителя 4 частоты для получения импульсов со скважностью 1/2. Данные от источника 2 информации записываются в виде параллельного кода в регистр 3. Строб сопровождения данных устанавливает в О первый счетчик 8. Передним фронтом очередного импульса серии Т1 с первого выхода делителя 4 частоты триггер 12 устанавливается в 1. Очередным передним фронтом импупьса с выхода RS-триггера 12, который задержан на время паузы импульсов серии Т1 относительно конца цикла формирования последнего импульса на выходе мультиплексора 5, D-триг-- rep 10 устанавливается в состояние, разрешающее через элемент И 7 выполнение сдвига в регистре 3 и счет числа переданных бит первым счетчиком 8. Кроме того, на управляющем входе мультилексора устанавливается значение сигнала, обеспечива- ющее формирование импульсов длительностью Т1 и Т2 в зависимости от значения сигнала на выходе сдвигового регистра 3. После того, как будут переданы все биты данных, в счетчике 8 установится код, равный числу передаваемых бит, и на выходе дешифратора 9 появится сигнал готовности к передаче очередного поля данных, поступающий на вход источника 2 информации и счетный вход второго счетчика 14, Этим сигналом D-триггер 10 уста на вливается в состояние, обеспечивающее формирование мультиплексором 5 импульсов синхронизации длительностью ТЗ.

Благодаря RS-триггеру 12 импульс сии хронизации вустройстве формируется лишь в том случае, когда очередные данные из источника 2 информации не успели поступить в регистр 3 за время формирования паузы первого импульса серии Т1. Прерывание формирования импульса синхронизации возможно лишь первым импульсом, серии Т1, что обеспечивает правильность формирования информационного импульt ca, Отсутствие импульса синхронизации между полями данных увеличивает пропускную способность устройства.

Наличие второго счетчика 14 обеспечи- 5 вает формирование импульса синхронизации длительностью ТЗ через заданное число передних полей данных, если темпы поступления данных выше темпа передачи. Это обеспечивает повышение достоверности Ю передаваемого сообщения при сборе из-за помехи счетчика бит передатчика, так как искажается не вся информация, а только ее часть , заключенная между двумя импульсами синхронизации.

15 Счет числа переданных полей осуществляется счетчиком 14, на тактовый вход которого поступают импульсы готовности с выхода дешифратора 9. После того, как чис- ло переданных полей становится равным 0 заданному, сигнал на выходе счетчика 14 меняет свое значение и через элемент ИЛИ 13 устанавливает на управляющем входе мультиплексора 5 значение сигнала, обес- печивающее формирование на его выходе 5 импульса длительностью ТЗ. Задним фронтом этого импульса ТЗ с третьего выхода делителя 4 частоты через второй формирователь 5 происходит сброс в О второго счечтика 14. При формировании импульса 0 синхронизации ТЗ в случае задержки поступления новых данных из источника 2 информации также происходит сброс в О счетчика 14, что предотвращает дублирование формирования импульса синхрониза- 5 ции ТЗ счетчиком 14.

На фиг.2 показана форма с гчалов в линии связи при передаче информации байт за байтом. На фиг.2а показана форма сигналов при задержке поступления информации 0 от источника на время t Т1, нафиг.2б- при отсутствии задержки поступления информации после передачи очередного поля и при заданном числе полей между импульсами синхронизации, равном 3, на фиг.2в - 5 ПРИ отсутствии информации.

Таким образом предлагаемое устройство для передачи информации обеспечивает повышение достоверности сообщения передаваемой информации за счет введения 0 второго формирователя короткого импульса, элемента ИЛИ и второго счетчика. Формула изобретения Устройство для передачи информации, содержащее источник информации, первый 5 и второй выходы которо о соединены соответственно с первым и вторым входами регистра сдвига, третий вход которого соединен с выходом элемента И и первым входом первого счетчика, второй вход кото- рого соединен с вторым выходом источника

информации, выход первого счетчика через дешифратор соединен с входом источника информации и первым входом D-триггера, выход которого соединен с входом блока задержки, выход тактового генератора соединен с первым входом делителя частоты, второй вход которого и первый вход RS- триггера соединены с выходом первого фор- мирователя коротких импульсов, вход которого и первый вход элемента И соединены с выходом мультиплексора, который является выходом устройства, первый, второй и третий выходы делителя частоты соединены соответственно с первым - третьим входами мультиплексора, первый выход делителя частоты соединен с вторым входом RS-триггера, выход которого соединен с

Пеле ffm/ныхfПтданнш ,, ГзГ

Тг Т, Т3

J%lJllJlJinjnM

Поле данных 1 - Поле домых1 Поле данныхЗ

1 Тз

1 Тз

1ЛЛГ1ЛЩЛЛ1ЛЛ11Г1Л

0

5

вторым входом D-триггера, третий выход делителя частоты - с четвертым входом муь- типлексора, пятый вход которого соединен с выходом регистра сдвига, отличающееся тем, что, с целью повышения достоверности передаваемой информации, введены последовательно соединенные второй формирователь коротких импульсов, второй счетчик и элемент ИЛИ, причем третий выход делителя частоты соединен с входом второго формирователя, выход дешифратора - с вторым входом второго счетчика, выход блока задержки с вторым входом элемента ИЛИ, выход которого соединен с шестым входом мультиплексора и вторым входом элемента И.

Тг Т, Т3

1 Тз

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-08-07—Публикация

1990-02-16—Подача