Изобретение относится к гибридной вычислительной технике и может быть использовано для машинного моделирования объектов с переменным запаздыванием в энергетике (ядерные реакторы и т.п.), в радиотехнике (системы пространственно-временной обработки сигналов и т.п.-). в биологии (биологические популяции и т.п.), в медицине (сердечно-сосудистые системы и т.п.) и в других отраслях.

Известно устройство для моделирова.- ния регулируемого запаздывания сигнала на элементах и узлах цифровой техники, в котором запаздывание реализуется путем последовательной перезаписи задерживаемого сигнала из регистра в регистр.

Наиболее близким к предлагаемому является устройство для моделирования переменного запаздывания, реализующее способ формирования запаздывания сигнала.

Устройство содержит аналого-цифровые преобразователи записи и сдвига, преобразователь времени запаздывания в напряжение, таймер, двоичный счетчик адресного кода ячеек записи, вычислитель адреса ячеек воспроизведения, шину данных, шину адресов, массив ячеек цифровой памяти, цифроаналоговый преобразователь воспроизведения, формирователи строби- рующих импульсов и схемы разрешения записи (воспроизведения).

Общим недостатком этих устройств является ограниченность их функциональных возможностей, связанная с невозможностью получения на одном устройстве группы задержанных -сигналов от одного входного Применение для таких целей нескольких устройств загромождает процесс моделирования и приводит к падению эффективности использования цифровой памяти.

Цель изобретения - расширение функциональных возможностей за счет одновреXI

оэ

00

ел ся о

менного моделирования п запаздываний входного сигнала.

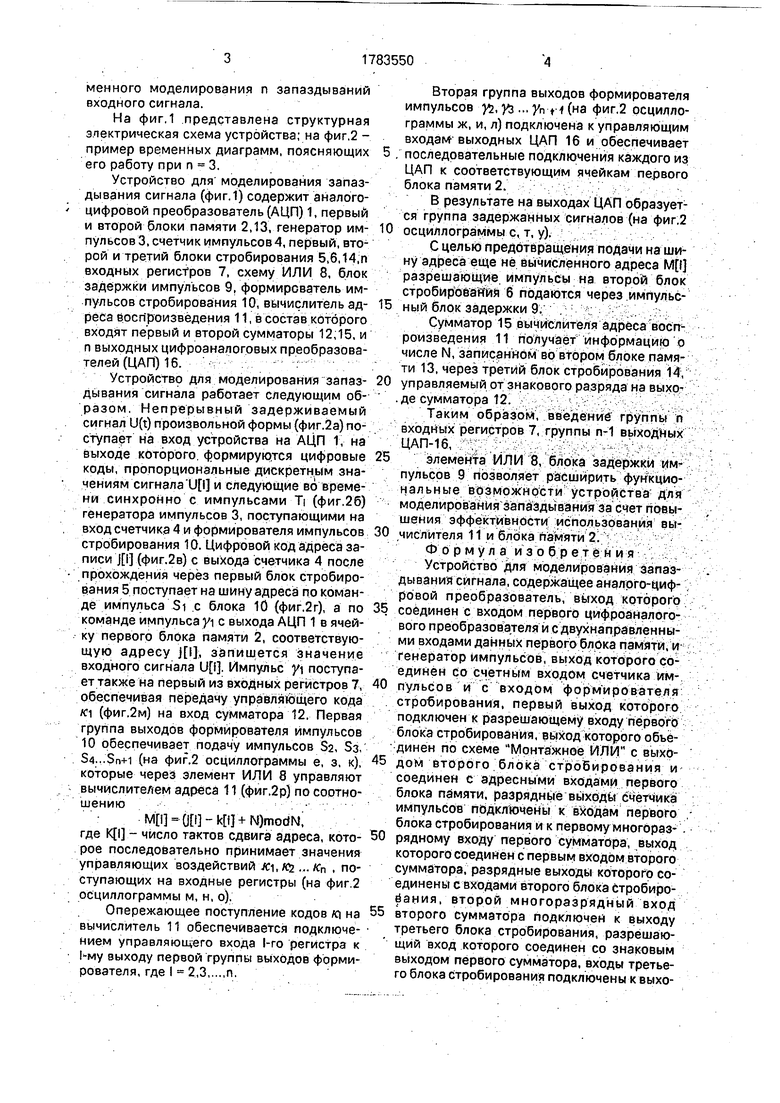

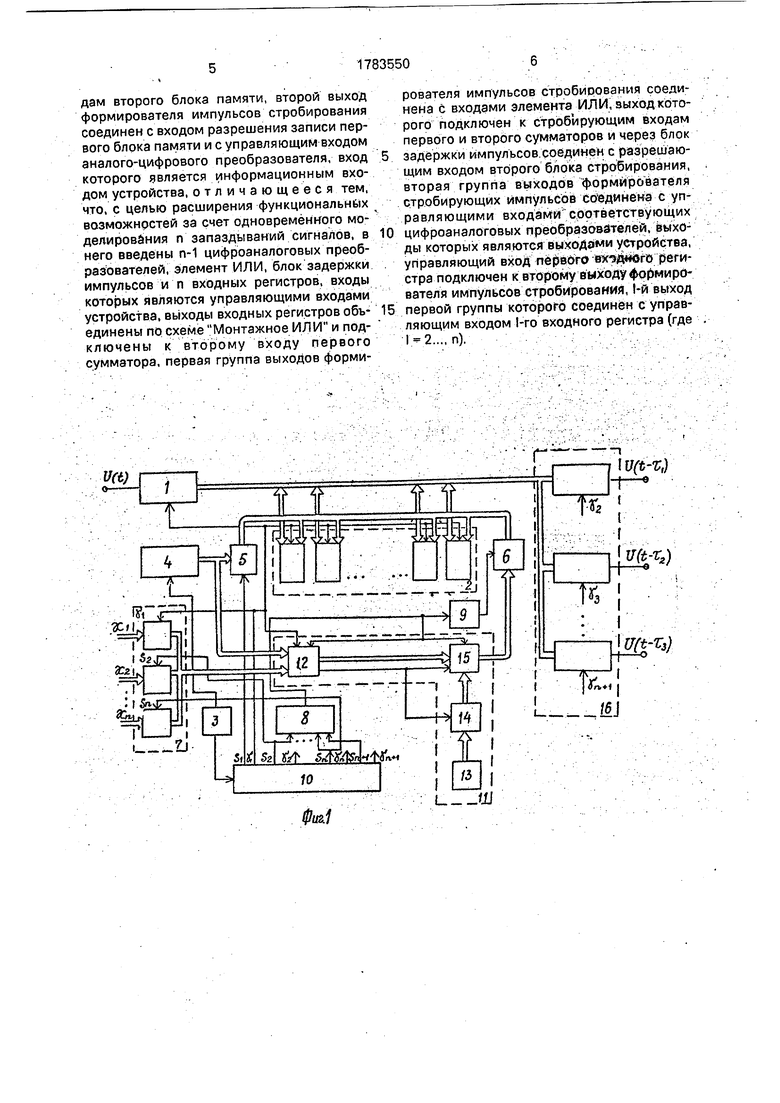

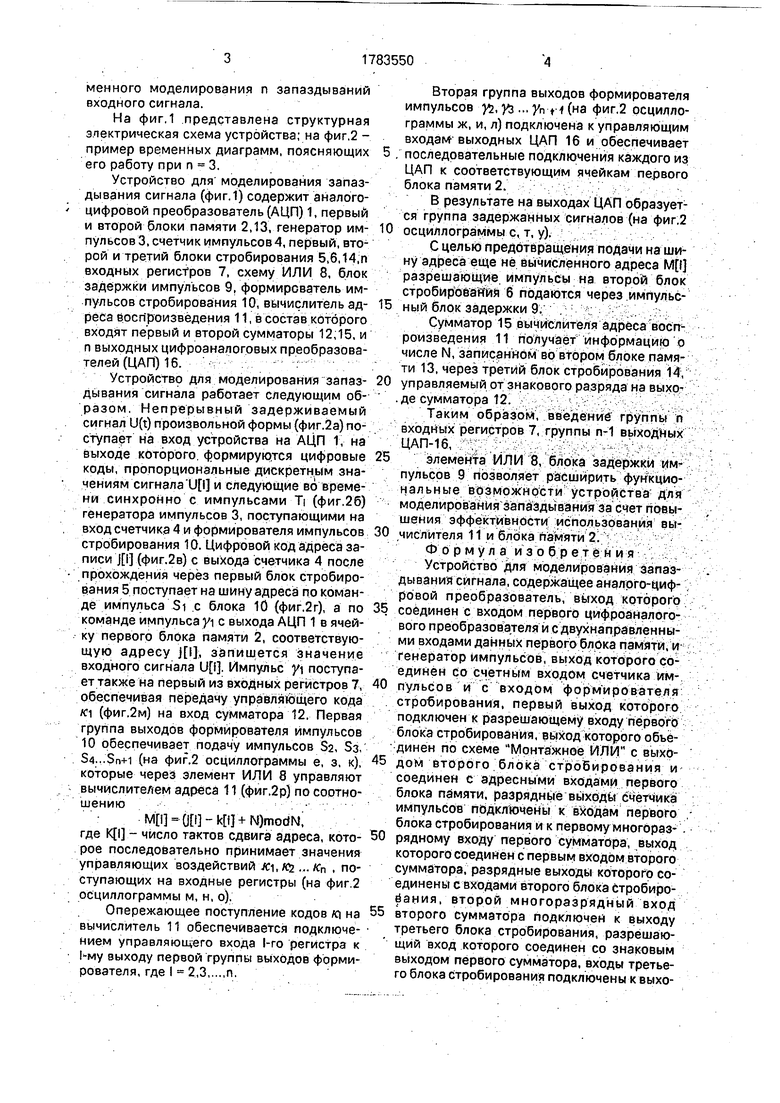

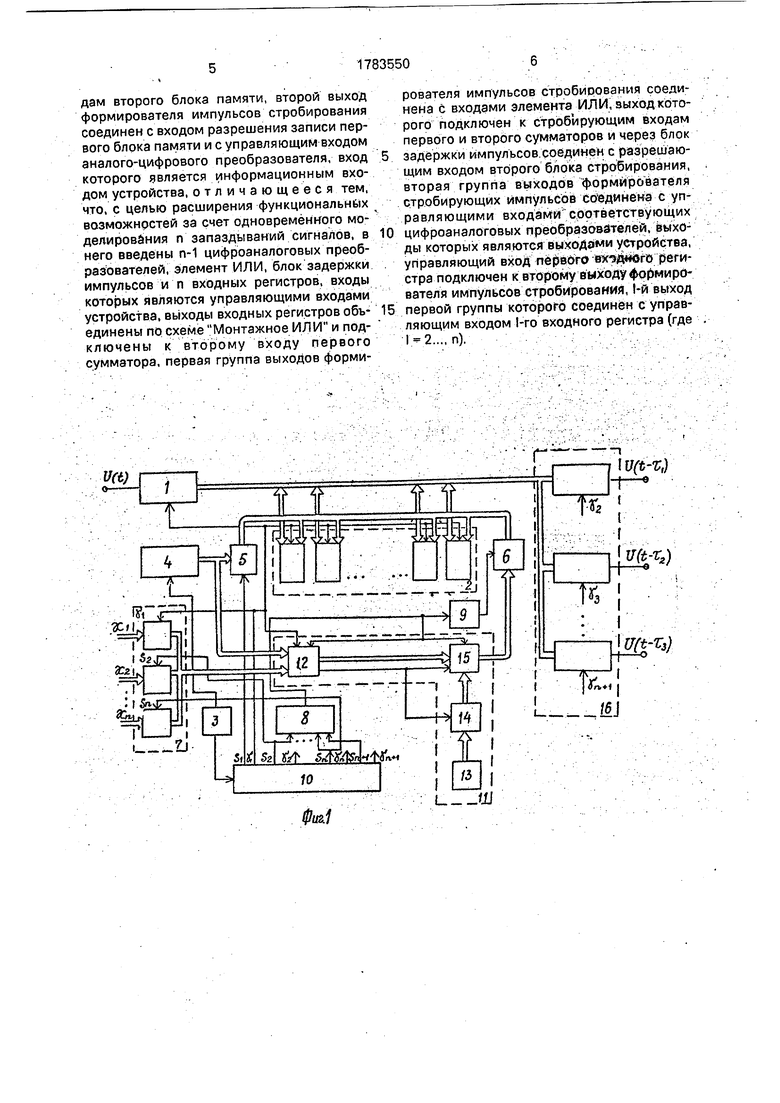

На фиг.1 представлена структурная эпектрическая схема устройства; на фиг.2 - пример временных диаграмм, поясняющих его работу при п 3,

Устройство для моделирования запаздывания сигнала (фиг.1) содержит аналого- цифровой преобразователь (АЦП) 1, первый и второй блоки памяти 2,13, генератор импульсов 3, счетчик импульсов 4, первый, второй и третий блоки стробирования 5,б,14,п входных регистров 7, схему ИЛИ 8, блок задержки импульсов 9, формирователь импульсов стробирования 10, вычислитель адреса воспроизведения 11, в состав которого входят первый и второй сумматоры 12,15, и п выходных цифроаналоговых преобразователей (ЦАП) 16.

Устройство для моделирования запаздывания сигнала работает следующим образом. Непрерывный задерживаемый сигнал U(t) произвольной формы (фиг.2а) поступает на вход устройства на АЦП 1, на выходе которого формируются цифровые коды, пропорциональные дискретным значениям сигнала и следующие во времени синхронно с импульсами Т| (фиг.26) генератора импульсов 3, поступающими на вход счетчика 4 и формирователя импульсов стробирования 10. Цифровой код адреса записи (фиг.2в) с выхода счетчика 4 после прохождения через первый блок стробирования 5 поступает на шину адреса по команде импульса Si с блока 10 (фиг.2г), а по команде импульса yi с выхода АЦП 1 в ячейку первого блока памяти 2, соответствующую адресу }, запишется значение входного сигнала . Импульс yi поступает также на первый из входных регистров 7, обеспечивая передачу управляющего кода /ci (фиг.2м) на вход сумматора 12. Первая группа выходов формирователя импульсов 10 обеспечивает подачу импульсов $2, 5з, $4...Sn+i (на фиг.2 осциллограммы е, з, к), которые через элемент ИЛИ 8 управляют вычислителем адреса 11 (фиг.2р) по соотношению

Of - + N)modN, где - число тактов сдвига адреса, которое последовательно принимает значения управляющих воздействий JCi, KZ ... /cn , поступающих на входные регистры (на фиг 2 осциллограммы м, н, о).

Опережающее поступление кодов к на вычислитель 11 обеспечивается подключением управляющего входа 1-го регистра к 1-му выходу первой группы выходов формирователя, где I 2,3, ..,п.

Вторая группа выходов формирователя импульсов у2, Уз ... УП 11 (на фиг.2 осциллограммы ж, и, л) подключена к управляющим входам выходных ЦАП 16 и обеспечивает

, последовательные подключения каждого из ЦАП к соответствующим ячейкам первого блока памяти 2.

В результате на выходах ЦАП образуется группа задержанных сигналов (на фиг.2

осциллограммы с, т, у).

С целью предотвращения подачи на шину адреса еще не вычисленного адреса М{1 разрешающие импульсы на второй блок стробировайия 6 подаются через импульсный блок задержки 9.

Сумматор 15 вычислителя адреса воспроизведения 11 получает информацию о числе N, записанном во втором блоке памяти 13, через третий блок стробирования 14,

управляемый от знакового разряда на выхо- .де сумматора 12.

Таким образом, введение группы п входных регистров 7, группы п-1 выходных ЦАП-16,

элемента ИЛИ 8, блока задержки импульсов 9 позволяет расширить функциональные возможности устройства для моделирования запаздывания за счет повышения эффективности использования вычислителя 11 и блока памяти 2.

Формула изобретения Устройство для моделирования запаздывания сигнала, содержащее аналого-цифровой преобразователь, выход которого

соединен с входом первого цифроаналого- вого преобразователя и с двухнаправленны- ми входами данных первого блока памяти, и генератор импульсов, выход которого соединен со счетным входом счетчика импульсов и с входом формирователя строЗироЁания, первый выход которого подключен к разрешающему входу первого блока стробирования, выход которого объединен по схеме Монтажное ИЛИ с выходом второго блока строБирования и соединен с адресными входами первого блока памяти, разрядные выходы счетчика импульсов подключены к входам первого блока стробирования и к первому многоразрядному входу первого сумматора, выход которого соединен с первым входом второго сумматора, разрядные выходы которого соединены с входами второго блока стробиро- ёания, второй многоразрядный вход

второго сумматора подключен к выходу третьего блока стробирования, разрешающий вход которого соединен со знаковым выходом первого сумматора, входы третьего блока стробирования подключены к выходам второго блока памяти, второй выход формирователя импульсов стробирования соединен с входом разрешения записи первого блока памяти и с управляющим входом аналого-цифрового преобразователя, вход которого является информационным входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет одновременного моделирования п запаздываний сигналов, в него введены п-1 цифроаналоговых преобразователей, элемент ИЛИ, блок задержки импульсов и п входных регистров, входы которых являются управляющими входами устройства, выходы входных регистров объединены по схеме Монтажное ИЛИ и подключены к второму входу первого сумматора, первая группа выходов формирователя импульсов стробиоования соединена с входами элемента И Л И, выход которого подключен к стробирующим входам первого и второго сумматоров и через блок

задержки импульсов соединен с разрешающим входом второго блока стробирования, вторая группа выходов формирователя стробирующих импульсов соединена с управляющими входами соответствующих

цифроаналоговых преобразователей, выходы которых являются выходами устройства, управляющий вход первого ехидного регистра подключен к второму выходу формирователя импульсов стробирования, 1-й выход

первой группы которого соединен с управляющим входом 1-го входного регистра (где 1 2..., п).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1545233A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство для измерения динамических характеристик | 1983 |

|

SU1168902A1 |

| Устройство для магнитной записи-воспроизведения звуковых сигналов | 1986 |

|

SU1339637A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

Изобретение относится к гибридной вычислительной технике и может быть использовано для машинного моделирования динамики сложных объектов с запаздыванием в различных областях техники. Цель изобретения - расширение функциональных возможностей за счет одновременного моделирования п запаздываний сигналов. Для этого в устройство введены цифроаналого- вые преобразователи, элемент ИЛИ, блок задержки импульсов и входные регистры. 2 ил

ЩЪ-Ъд

т-Ъ)

г ЛЬппппппппппппппппппппппппппП Ј

П П п П П П П П П П П П П П П П П П П П П Я П П П П П

$ ш п п п п п п п п п п п п п п п п п п п п п п п п п п п

3$ & I I I I I I I I I I I I I I I I I I I I I I I I I I I I

.ff& П П П П П П П П П П П П П. П П П П П П П П П П П П П П П

и.) Г, I I I I I 1 I I I I I I I I I I I I I ,1 1 I I I I t I I J к).Ь ППГТПППППППППППП ПППППГСППППППП Jt

П)п „ n f4lts ISM4NM4f4M f4 AnHnL г,J

Фаз. 2

| Титов Н,М | |||

| и др | |||

| Моделирование систем с запаздыванием | |||

| М.: Энергия, 1969 | |||

| Способ формирования запаздывания сигнала | 1988 |

|

SU1599875A1 |

Авторы

Даты

1992-12-23—Публикация

1990-01-10—Подача