SJ

00 GJ О

Изобретение относится к цифровой информационно-измерительной технике и может быть использовано для преобразования быстроизменяюицихся сигналов в цифровой код, а также для сопряжения цифровых вы- числительных машин с аналоговыми каналами, имеющими большой динамический диапазон сигнала.

Известно устройство для аналого-цифрового преобразования, основанное на ав- тематическом управлении напряжения смещения, подаваемого на вход аналого- цифрового преобразователя совместно с входным сигналом, что позволяет расширить динамический диапазон входных сигналов и увеличить точность преобразования. Это устройство содержит блок изменения координаты положения, выполненный на суммирующем усилителе и ключах, аналого-цифровой преобразователь, постоянное запоминающее устройство, блок управления, выполненный на двух постоянных запоминающих устройствах и регистре памяти.

Данное устройство обеспечивает высо- кую скорость преобразования, однако, не позволяет обеспечить высокую точность при малых значениях напряжения сигнала и тем самым существенно расширить динамический диапазон, так как расширение ра- бочего диапазона происходит только в области больших напряжений, превышающих верхний предел работы аналого-цифрового преобразователя.

Наиболее близким по технической сущ- ности к изобретению является устройство для аналого-цифрового преобразования с автоматическим выбором предела измерений, принцип работы которого основан на автоматическом управлении коэффициен- том передачи блока масштаба путем пред- варительной оценки уровня входного сигнала и вычисления, исходя из этого, такого значения коэффициента передачи блока масштаба, которое обеспечит наименьшее значение приведенной погрешности. Устройство содержит блок аналогового запоминания, блок масштаба, аналого-цифровой преобразователь, блок выбора масштаба, включающий постоянное запоминающее устройство, цифровой делитель, а также регистр, блок синхронизации, арифметико-логический блок, регистр масштаба, элемент ИЛИ, таймер.

Это устройство характеризуется высо- кой точностью преобразования, однако оно обладает малым быстродействием и не позволяет существенно расширить динамический диапазон устройства. Эти недостатки обусловлены тем, что каждое преобразование производится за два цикла; в первом цикле - предварительное преобразование и вычисление коэффициента передачи блока масштаба, а во втором - собственно точное преобразование, что увеличивает соответственно полное время преобразования в 2 раза. Включение на входе устройства аналогового запоминающего устройства не позволяет обеспечить линейность характеристики преобразования при малых уровнях сигнала и тем самым ограничивает динамический диапазон входных сигналов.

Целью изобретения является повышение скорости преобразования при одновременном расширении динамического диапазона.

Поставленная цель достигается тем, что в устройство аналого-цифрового преобразования с автоматическим выбором предела измерения, содержащее блок масштаба, аналоговое запоминающее устройство, аналого-цифровой преобразователь, арифметико-логический блок, блок в ыбора масштаба и блок синхронизации, при этом первый выход аналого-цифрового преобразователя подключен к первому входу арифметико-логического блока и к первому входу блока выбора масштаба, второй вход аналогового запоминающего устройства и второй вход аналого-цифрового преобразователя соединены с шиной Запуск, а выход арифметико-логического блока является выходной шиной устройства, введен блок анализа скорости, при этом первый вход блока анализа скорости подключен к первому выходу блока синхронизации, второй выход которого подключен к третьему входу блока выбора масштаба, вход блока синхронизации подключен к второму выходу аналого-цифрового преобразователя, второй вход блока анализа скорости соединен с вторым выходом блока выбора масштаба, выход блока анализа скорости подключен к второму входу блока выбора масштаб, третий вход блока формирования, первый вход блока масштаба и второй вход арифметико-логического блока подключены к первому выходу блока выбора масштаба, первый вход аналого-цифрового преобразователя соединен с выходом аналогового запоминающего устройства, первый вход которого подключен к выходу блока масштаба, второй вход блока масштаба является входной шиной устройства, при этом блок выбора масштаба выполнен на преобразователе кода, первым ПЗУ, регистре, сумматоре, втором ПЗУ и элементе И-НЕ, первый вход сумматора подключен к выходу первого ПЗУ, а второй вход сумматора и первый вход второго ПЗУ подключены к выходу регистра, выход сумматора подключен к первому входу регистра, второй вход регистра подключен к выходу элемента И-НЕ, выход регистра является первым выходом блока, первый вход первого ПЗУ подключен к выходу преобразовате- ля кодов, второй вход первого ПЗУ является вторым входом блока, вход преобразователя кодов является первым входом блока, выход первого ПЗУ подключен к второму входу второго ПЗУ и является вторым выхо- дом блока, первый вход элемента И-НЕ подключен к выходу второго ПЗУ, второй вход эл-змента И-НЕ является третьим входом блока, блок анализа скорости выполнен на ПЗУ, с маторе и регистре, причем пер- вый вход регистра подключен к выходу сум- , матора, а выход регистра подключен к второму входу сумматора, второму входу ПЗУ и является выходом блока, первый вход сумматора подключен к выходу ПЗУ, пер- вый вход которого является вторым входом блока, второй вход регистра является первым входом блока.

Предлагаемое устройство, по сравнению с прототипом, обеспечивает возмож- ность повышения скорости преобразования и расширения динамического диапазона измеряемых сигналов за счет введения блока анализа скорости, нового алгоритма управления блоком масштаба, основанного на анализе мгновенных значений входного сигнала и скорости изменения входного сигнала, что позволяет организовать адаптивное управление блоком масштаба, при котором величина приведенной погрешно- сти зависит от скорости изменения входного напряжения.

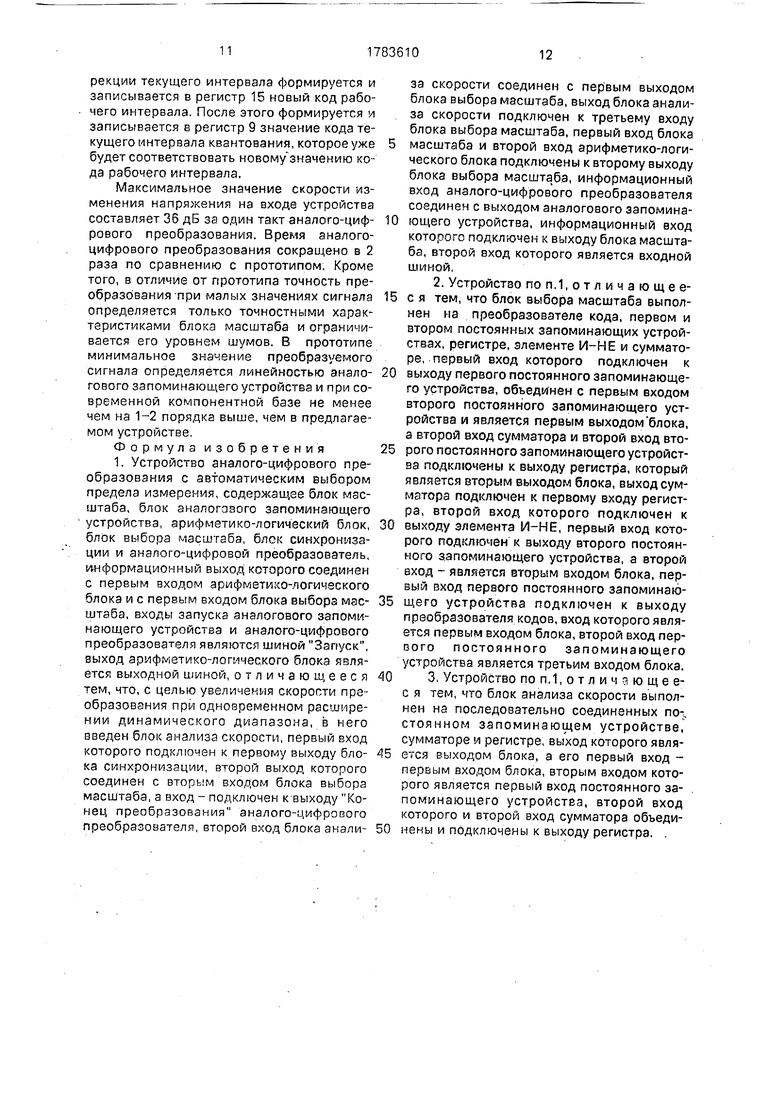

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - временная диаграмма его работы.

Устройство аналого-цифрового преобразования с автоматическим выбором предела измерения (фиг.1) включает блок 1 масштаба, аналоговое запоминающее устройство 2, аналого-цифровой преобразова- тель 3, арифметико-логический бло к 4, блок 5 выбора масштаба, включающий преобразователь кодов 6, первое ПЗУ 7, сумматор 8, регистр 9, второе ПЗУ 10, элемент И-НЕ 11, а также блок 12 анализа скорости, включа- ющий ПЗУ 13, сумматор 14, регистр 15, а также блок синхронизации 16, входную клемму запуска 17, выходную клемму 18 и входную клемму 19. Первый выход аналого- цифрового преобразователя 3 подключен к первому входу арифметико-логического блока 4 и первому входу блока 5 выбора масштаба, а второй вход аналогового запоминающего устройства 2 и второй вход ана- лого-цифрового преобразователя 3

подключены к шине 17 запуска. Выход арифметико-логического блока 4 является входной шиной 19 устройства. Первый выход блока 12 анализа скорости подключен к первому выходу блока 16 синхронизации, второй выход которого подключен к третьему входу блока 5 выбора масштаба, а вход блока 16 синхронизации подключен к второму выходу аналого-цифрового преобразователя 3. Второй вход блока 12 анализа скорости соединен с вторым выходом блока 5 выбора масштаба.

Выход блока 12 анализа скорости подключен к второму входу блока 5 выборамас- штаба, г первый вход блока 1 масштаба и второй вход арифметико-логического блока 4 подключены к первому выходу блока 5 выбора масштаба. Первый вход аналого- цифрового преобразователя 3 соединен с выходом аналогового запоминающего устройства 2, первый вход которого подключен к выходу блока 1 масштаба, а второй вход блока 1 масштаба является входной клеммой 19 устройства.

Первый вход сумматора 8 и первый вход

второго ПЗУ 10 подключены к выходу регистра 9. Второй вход регистра 9 подключен к выходу элемента И-НЕ 11, выход регистра 9 является первым выходом блока 5 выбора масштаба, Первый вход первого ПЗУ 7 является вторым входом блока 5 выбора масштаба, вход преобразователя кодов 6 является первым входом блока 5 выбора масштаба. Выход первого ПЗУ 7 подключен к второму входу второго ПЗУ 10 и является вторым выходам блока 5 выбора масштаба. Первый вход элемента И-НЕ 11 подключен к выходу второго ПЗУ 10, а второй вход элемента И-НЕ 11 является третьим входом блока 5 выбора масштаба.

Вход регистра 15 подключен к выходу сумматора 14. а выход регистра 15 подключен к второму входу сумматора 14, второму входу ПЗУ 13 и является выходом блока 12 анализа скорости. Первый вход сумматора 14 подключен к выходу ПЗУ 13, первый вход которого является вторым входом блока 12 анализа скорости, второй вход регистра 15 является первым входом блока 12 анализа скорости.

Практическая реализация всех охарактеризованных функциональных блоков устройства аналого-цифрового преобразования с автоматическим выбором предела измерения на более низком структурном уровне, чем это показано на фиг.1 и изложено выше, известна.

Блок 1 масштаба представляет собой программируемый усилитель, Блок 2 аналогового запоминающего устройства может

быть реализован на интегральной микросхеме К1100СК2. Блок 16 синхронизации может быть реализован на ждущем мультивибраторе К155АГЗ. ПЗУ 7, 10 и 13 могут быть выполнены на любом интегральном ПЗУ с организацией 256 х 4 (например, К556РТ4), преобразователь б кодов может быть выполнен на интегральном ПЗУ с организацией не менее 4096 х 4 или реализован на комбинационной схеме дешифрации. В качестве сумматоров 8, 14 может быть использован арифметический 4-разрядный сумматор К155ИМ1, в качестве регистров 9 и 15 - регистры К155ИР15.

Сущность изобретения заключается в следующем. С точки зрения обеспечения наименьшей приведенной погрешности аналого-цифрового преобразования управление коэффициентом передачи блока масштаба должно осуществляться таким образом, чтобы при любых значениях входного сигнала на входе устройства значение напряжения на входе аналого-цифрового преобразователя (АЦП) 3 находилось как можно ближе к верхнему пределу рабочего диапазона АЦП. Разбивают весь диапазон входных напряжений АЦП на п интервалов, где п - количество разрядов АЦП, и считают, что некоторая 1-я выборка с весом старшего разряда к находится в k-м интервале квантования. Чем выше находится интервал квантования выборки, тем меньшее значение имеет приведенная погрешность, и с точки зрения порядкового номера интервала квантования можно оценивать приведенную погрешность квантования.

Управление коэффициентом передачи блока масштаба осуществляется таким образом, чтобы каждая текущая выборка находилась в самом верхнем интервале. С этой целью после каждого такта аналого-цифрового преобразователя осуществляется анализ значения полученной выборки и определяется соответствующий ей интервал квантования. Затем вычисляется новое значение коэффициента передачи блока 1 масштаба таким образом, чтобы следующая выборка, взятая через постоянное значение времени дискретизации, оказалась в n-м интервале квантования. Очевидно, что при бы- строизменяющемся напряжении на входе устройства за время между двумя соседними выборками она может выйти за верхний предел п-го интервала квантования и, соответственно, за рабочий диапазон АЦП, и в этом случае значение такой выборки будет искажено. С целью предотвращения перегрузки блока АЦП осуществляется анализ скорости изменения входного напряжения. Чем выше скорость изменения напряжения;

тем более низким должен быть выбран рабочий интервал квантования, т.е. такой интервал, в котором должны находиться все текущие выборки сигнала. По мере изменения скорости изменения сигнала изменяется, соответственно, и рабочий интервал квантования. Таким образом, осуществляется адаптивное управление коэффициентом передачи блока масштаба с целью обеспечения минимальной приведенной погрешности преобразования и исключения перегрузки АЦП при данной скорости изменения входного сигнала,

Включение блока 1 масштаба непосредственно на вход устройства позволяет увеличить динамический диапазон, так как в этом случае динамический диапазон определяется диапазоном значений коэффициента передачи блока 1 масштаба, точностью установки коэффициента передачи и шумовыми свойствами блока масштаба и может быть достаточно большим,

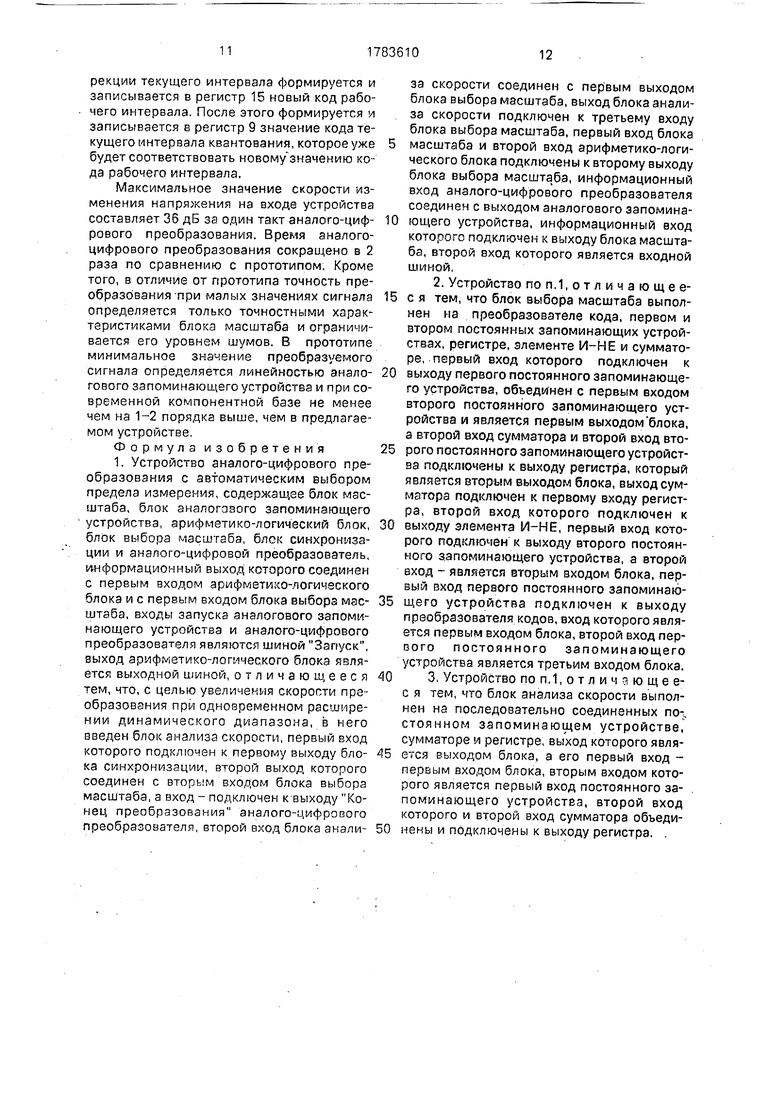

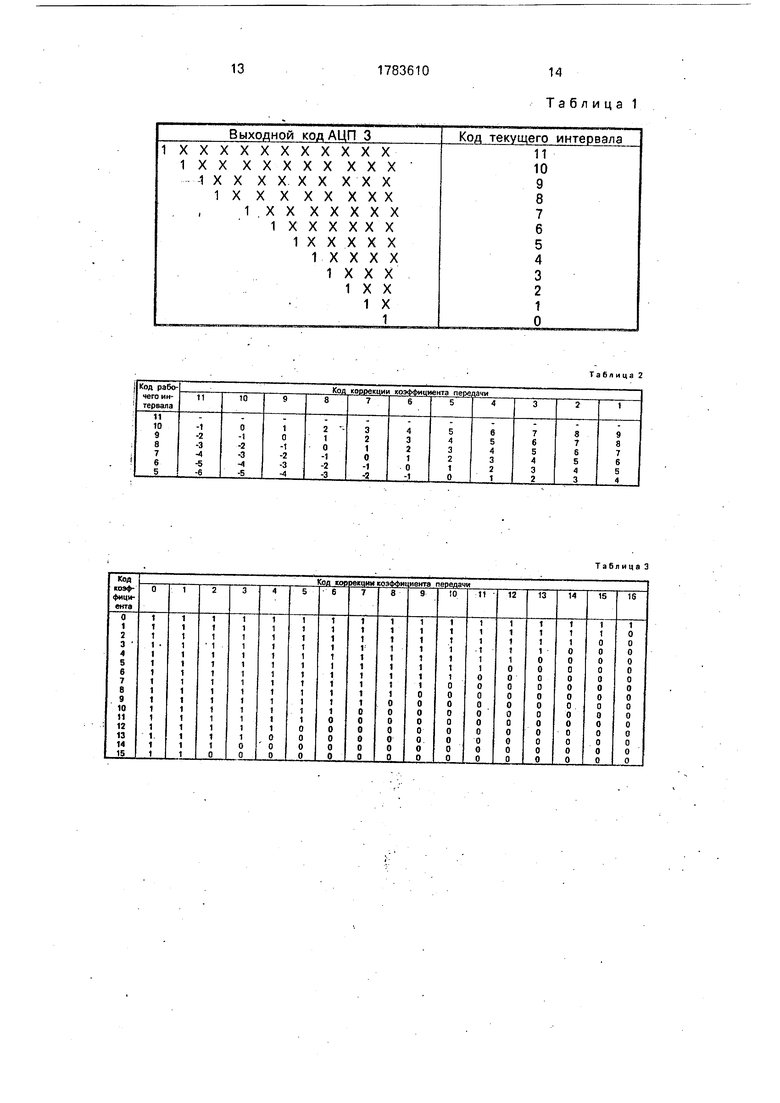

Устройство работает следующим образом. По приходу очередного импульса запу- сга по шине 17 производится фиксация выходного напряжения блока 1 масштаба в аналоговом запоминающем устройстве 2 и преобразование его в цифровой код аналого-цифровым преобразователем 3. Блок 1 масштаба управляется 4-разрядным кодом и обеспечивает изменение коэффициента передачи от 1 до 215, при этом коэффициент. передачи может принимать значения из следующего ряда: 1, 2, 4, 8, 16, 32... 32768. Результат аналого-цифрового преобразования поступает на вход преобразователя кодов б, где осуществляется кодирование текущего интервала квантования двоичным 4-разрядным кодом (табл. 1). С выхода преобразователя б кодов код интервала поступает на первый вход ПЗУ 7, на второй вход которого с блока 12 анализа скорости подается 4-разрядный код рабочего интервала, в котором должна находиться текущая выборка. ПЗУ 7 осуществляет формирование 4- разрядного кода коррекции коэффициента передачи блока 1 масштаба. Прошивка ПЗУ 7 приведена в табл, 2. Код коррекции с выхода ПЗУ 7 поступает на второй вход сумматора 8, на первый вход которого подается код коэффициента передачи блока 1 масштаба, который хранится в регистре 9. В этом случае, если текущая выборка попала в интервал квантования, который на данный

5 момент определен как рабочий, то формируемый код коррекции равен 0000; таким образом, после суммирования в сумматоре 8 с коэффициентом передачи блока 1 масштаба в регистр 9 будет переписано то же значение. Если интервал квантования текущей

0

5

0

5

0

5

0

5

0

выборки оказался ниже рабочего интервала, например, на один интервал, это значит, что коэффициент передачи блока 1 масштаба должен быть увеличен в два раза и формируемый код коррекции ПЗУ 7 будет равен 0001. Если интервал квантования текущей выборки на один интервал выше рабочего интервала, то в ПЗУ 7 формируется код 1111, который представляет собой дополнительный код числа - 1 и, будучи просумми- рован в сумматоре 8 со значением кода коэффициента передачи, уменьшит его на 1, что соответствует уменьшению коэффициента передачи в 2 раза. Код коэффициента передачи с регистра 9 поступает на второй вход блока 1 масштаба и определяет тем самым требуемый коэффициент передачи, который должен быть установлен к приходу следующего импульса запуска АЦП 3 и аналогового запоминающего устройства 2. За- пись в резистор 9 осуществляется сигналом с блока 16 синхронизации,

Блок 16 синхронизации запускается сигналом окончания преобразования АЦП этом сигнал на втором выходе блока 16 синхронизации появляется с задержкой относительно сигнала на первом выходе на величину, равную времени установления в логических элементах блока 5 выбора масштаба. Сигнал на первом выходе блока 16 появляется соответственно с такой же задержкой относительно входного сигнала.

Код коррекции с выхода ПЗУ 7 поступает на первый вход ПЗУ 10, на второй вход которого подается код коэффициента пере- дачи с выхода регистра 9. Прошивка ПЗУ 10 приведена в табл. 3. ПЗУ 10 формирует сигнал запрета записи, который подается на первый вход элемента И-НЕ 11, в результате чего сигнал окончания преобразования с второго выхода АЦП не проходит на вход записи регистра 9. Формирование сигнала запрета записи осуществляется следующим образом. При значениях кода коэффициента передачи, близких к крайним значениям 0000 и 1111 при некоторых значениях кода коррекции, отличных от 0000, возможно получение инверсных значений кода коэффициента передачи, что приведет к неработоспособности устройства, Для исключения этого в ПЗУ 10 производится анализ текущего значения кода коэффициента передачи и кода коррекции, и при коде коррекции, большем некоторого значения для данного кода коэффициента передачи, на выходе формируется сигнал низкого уровня. Так, например, если код коэффициента передачи ра вен 1101, то при значении кода коррекции 0011, 0100, 0101 и более прохождение сигнала записи будет заблокировано, так как

на выходе сумматора 8 произойдет переполнение. Аналогично происходит формирование сигнала блокирования записи при переходе через нижний предел диапазона изменения кода коэффициента передачи.

Код коэффициента передачи с первого выхода блока 5 выбора масштаба поступает на второй вход арифметико-логического блока 4, в котором осуществляется преобразование данных с учетом коэффициента передачи блока масштаба. При этом код блока 3 АЦП представляет собой мантиссу числа, а код коэффициента передачи - порядок по основанию 2.

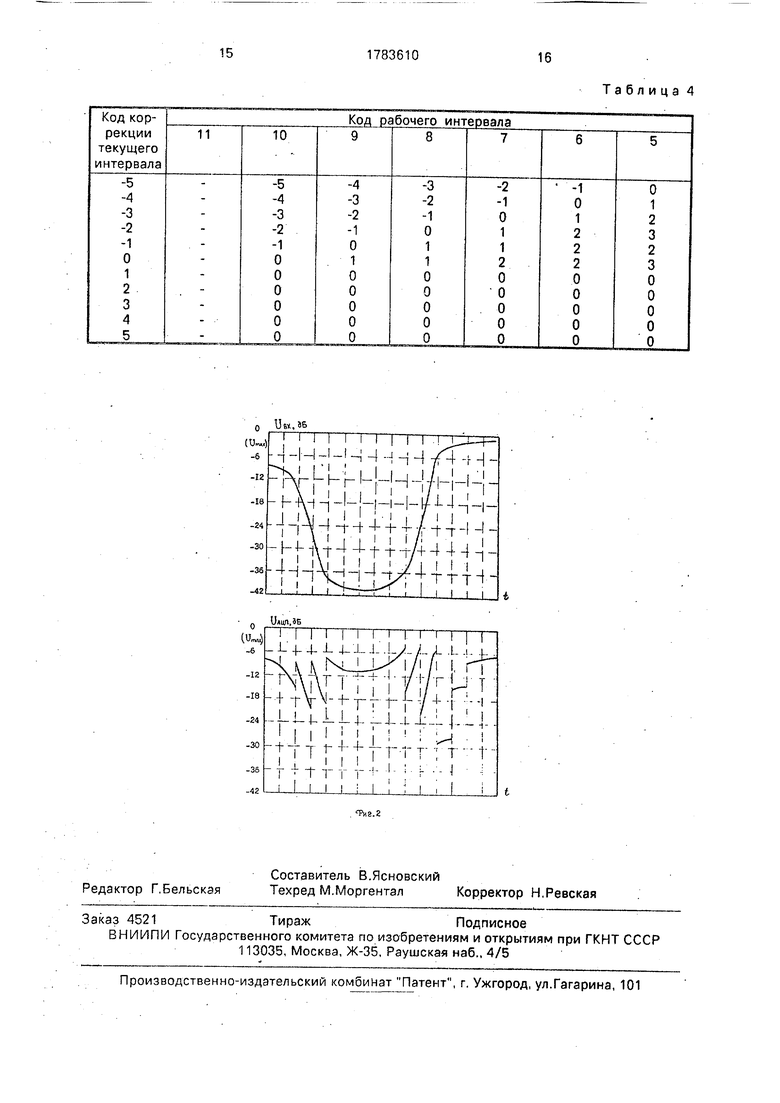

Код коррекции текущего интервала с второго выхода блока 5 выбора масштаба подается на второй вход блока 12 анализа скорости, в котором осуществляется формирование кода рабочего интервала. Код коррекции коэффициента передачи с выхода ПЗУ 7 поступает на первый вход ПЗУ 13, на второй вход которого подается код рабочего интервала с выхода регистра 15. ПЗУ 13 формирует код коррекции рабочего интервала, который подается на первый вход сумматора 14, в котором, в свою очередь, происходит его суммирование с кодом рабочего интервала. Прошивка ПЗУ 13 приведена в табл. 4.

Как видно из данных табл. 4, устанавливаемое значение кода рабочего интервала определяется кодом коррекции текущего интервала (т.е. скоростью изменения напряжения на входе устройства) и значением кода рабочего интервала на предыдущем такте преобразования, При больших значениях кода коррекции текущего интервала, т.е. при большой скорости изменения на- пр яжения рабочий интервал устанавливается в середине диапазона рабочих интервалов квантования АЦП. При малых скоростях изменения код рабочего интервала становится равным 10, что обеспечит один защитный интервал квантования. При появлении в этом случае на входе устройства положительного скачка напряжения ео скоростью нарастания не более 6 дБ за период аналого-цифрового преобразования перегрузка блока 3 АЦП будет исключена.

Так как сначала производится запись кода рабочего интервала в регистр 15, а затем запись кода текущего интервала в регистр 9, то формирование кода текущего интервала осуществляется в следующей последовательности. На l-м такте аналого- цифрового преобразования производится формирование в ПЗУ 7 кода коррекции текущего интервала на основании кода рабочего интервала,,сформированного на (Ы) такте. Затем по сформированному код

рекции текущего интервала формируется и записывается в регистр 15 новый код рабочего интервала. После этого формируется и записывается в регистр 9 значение кода текущего интервала квантования,которое уже будет соответствовать новому значению кода рабочего интервала.

Максимальное значение скорости изменения напряжения на входе устройства составляет 36 дБ за один такт аналого-цифрового преобразования. Время аналого- цифрового преобразования сокращено в 2 раза по сравнению с прототипом. Кроме того, в отличие от прототипа точность преобразования при малых значениях сигнала определяется только точностными характеристиками блока масштаба и ограничивается его уровнем шумов. В прототипе минимальное значение преобразуемого сигнала определяется линейностью аналогового запоминающего устройства и при современной компонентной базе не менее чем на 1-2 порядка выше, чем в предлагаемом устройстве.

Формула изобретения 1. Устройство аналого-цифрового преобразования с автоматическим выбором предела измерения, содержащее блок масштаба, блок аналогового запоминающего устройства, арифметико-логический блок, блок выбора масштаба, блек синхронизации и аналого-цифровой преобразователь, информационный выход которого соединен с первым входом арифметико-логического блока и с первым входом блока выбора масштаба, входы запуска аналогового запоминающего устройства и аналого-цифрового преобразователя являются шиной Запуск, зыход арифметико-логического блока является выходной шиной, отличающееся тем, что, с целью увеличения скорости преобразования при одновременном расширении динамического диапазона, в него введен блок анализа скорости, первый вход которого подключен к первому выходу блока синхронизации, второй выход которого соединен с вторым входом блока выбора масштаба, а вход - подключен к выходу Конец преобразования аналого-цифрового преобразователя, второй вход блока анализа скорости соединен с первым выходом блока выбора масштаба, выход блока анализа скорости подключен к третьему входу блока выбора масштаба, первый вход блока

масштаба и второй вход арифметико-логического блока подключены к второму выходу блока выбора масштаба, информационный вход аналого-цифрового преобразователя соединен с выходом аналогового запоминающего устройства, информационный вход которого подключен к выходу блока масштаба, второй вход которого является входной шиной.

2. Устройство поп.1,отличающеес я тем, что блок выбора масштаба выполнен на преобразователе кода, первом и втором постоянных запоминающих устройствах, регистре, элементе И-НЕ и сумматоре, первый вход которого подключен к

выходу первого постоянного запоминающего устройства, объединен с первым входом второго постоянного запоминающего устройства и является первым выходом блока, а второй вход сумматора и второй вход второго постоянного запоминающего устройства подключены к выходу регистра, который является вторым выходом блока, выход сумматора подключен к первому входу регистра, второй вход которого подключен к

выходу элемента , первый вход которого подключен к выходу второго постоянного запоминающего устройства, а второй вход - является вторым входом блока, первый вход первого постоянного запоминающего устройства подключен к выходу преобразователя кодов, вход которого является первым входом блока, второй вход первого постоянного запоминающего устройства является третьим входом блока.

3. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок анализа скорости выполнен на последовательно соединенных по-. стоянном запоминающем устройстве, сумматоре и регистре, выход которого являстся выходом блока, а его первый вход - первым входом блока, вторым входом которого является первый вход постоянного запоминающего устройства, второй вход которого и второй вход сумматора объединены и подключены к выходу регистра.

13

1783610

14 Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Устройство для измерения температуры | 1988 |

|

SU1672237A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ АМПЛИТУДЫ ИМПУЛЬСОВ И ИЗМЕРИТЕЛЬ ЕГО РЕАЛИЗУЮЩИЙ (ВАРИАНТЫ) | 2021 |

|

RU2773621C1 |

| Анализатор амплитудных распре-дЕлЕНий | 1979 |

|

SU798868A1 |

| СПОСОБ ИНДЕНТИФИКАЦИИ ТОНАЛЬНЫХ СИГНАЛОВ В СЕТЯХ СВЯЗИ И ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2291405C2 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

Изобретение относится к цифровой информационно-измерительной технике и может быть использовано для преобразования быстроизменяющихся сигналов в цифровой код, а также для сопряжения цифровых вычислительных машин с аналоговыми канала/7 ми, имеющими большой динамический диапазон. Цель изобретения - повышение скорости преобразования при одновременном расширении динамического диапазона. Устройство содержит блок 1 масштаба, аналоговое запоминающее устройство 2, аналого-цифровой преобразователь 3, арифметико-логический блок 4, блок 5 выбора масштаба, блок 16 синхронизации. Введение в устройство 12 анализа скорости и установление-новых связей в блоке 5 выбора масштаба позволяет обеспечить за счет анализа мгновенных значений и скорости изменения напряжения сигнала управление коэффициентом передачи блока 1 масштаба с целью обеспечения минимальней приведенной погрешности и исключения перегрузки АЦП при данной скорости изменения входного сигнала. 2 з.п. ф-лы, 2 ил. (Л С

Таблица 2

Таблица 3

Таблица А

| Устройство для аналого-цифрового преобразования | 1987 |

|

SU1425828A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство аналого-цифрового преобразования с автоматическим выбором предела измерения | 1986 |

|

SU1379941A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-23—Публикация

1990-12-20—Подача