I 1

Изобретение относится к вычисли- - тельной технике и может быть испольN.

зовано в запоминающих устройствах.

Цель изобретения - повышение быстродействия устройства.

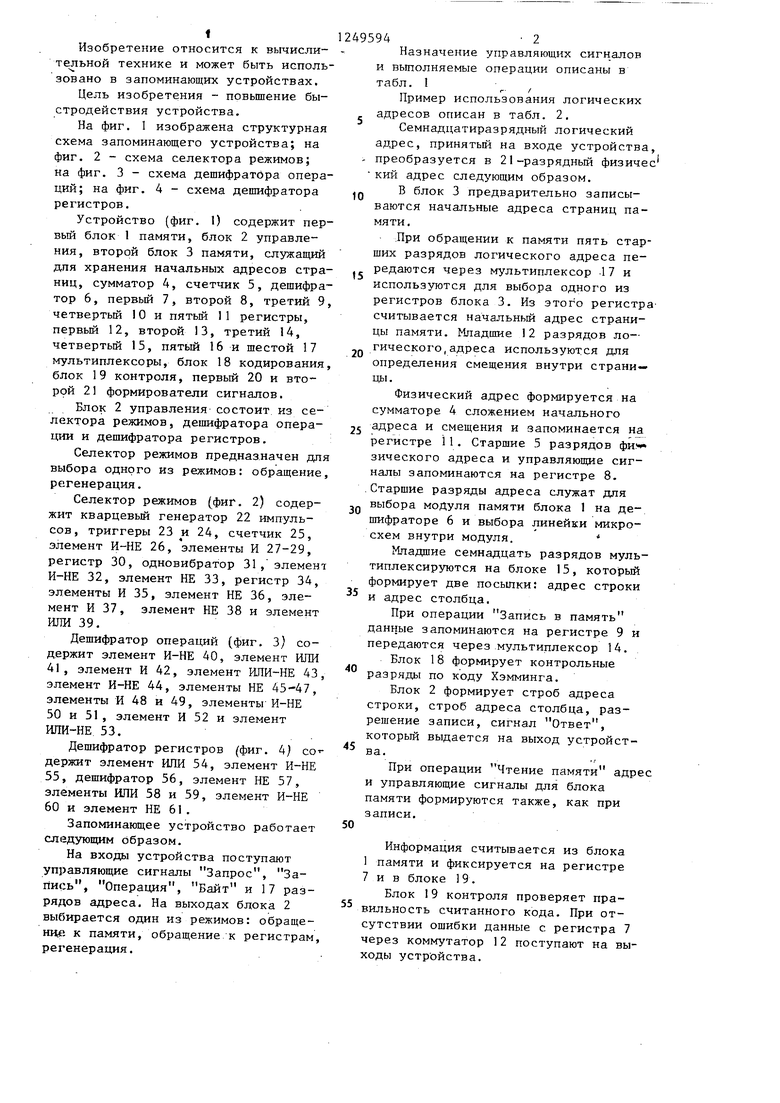

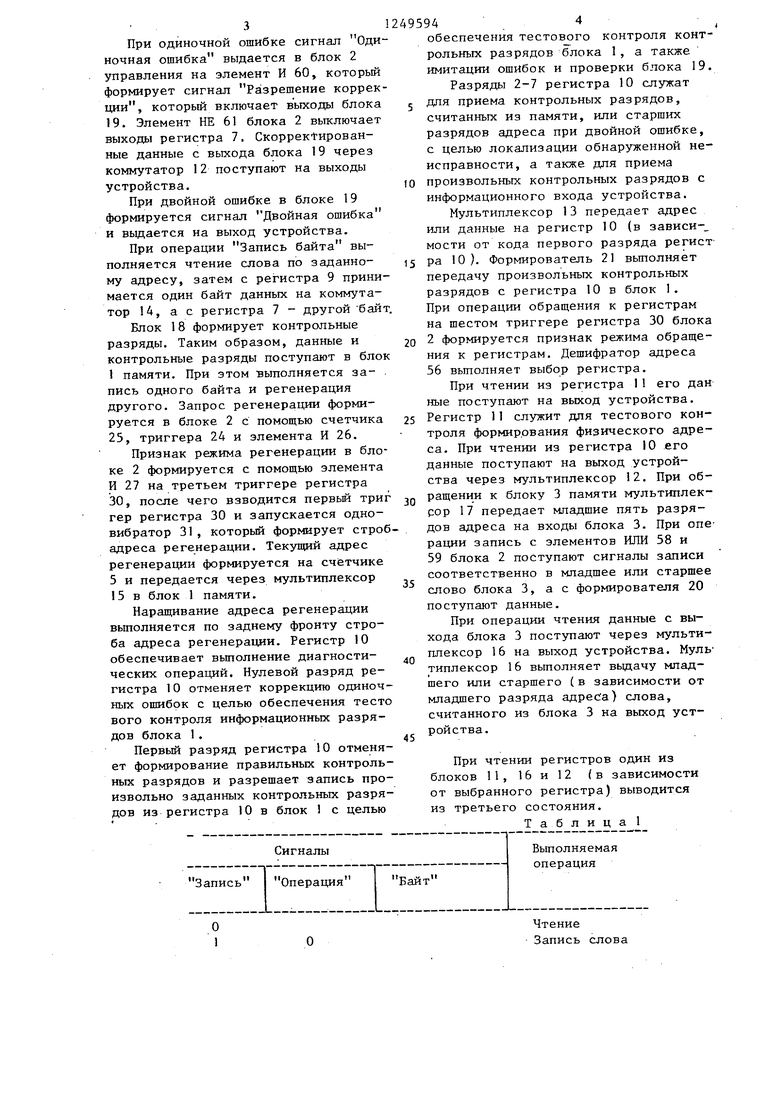

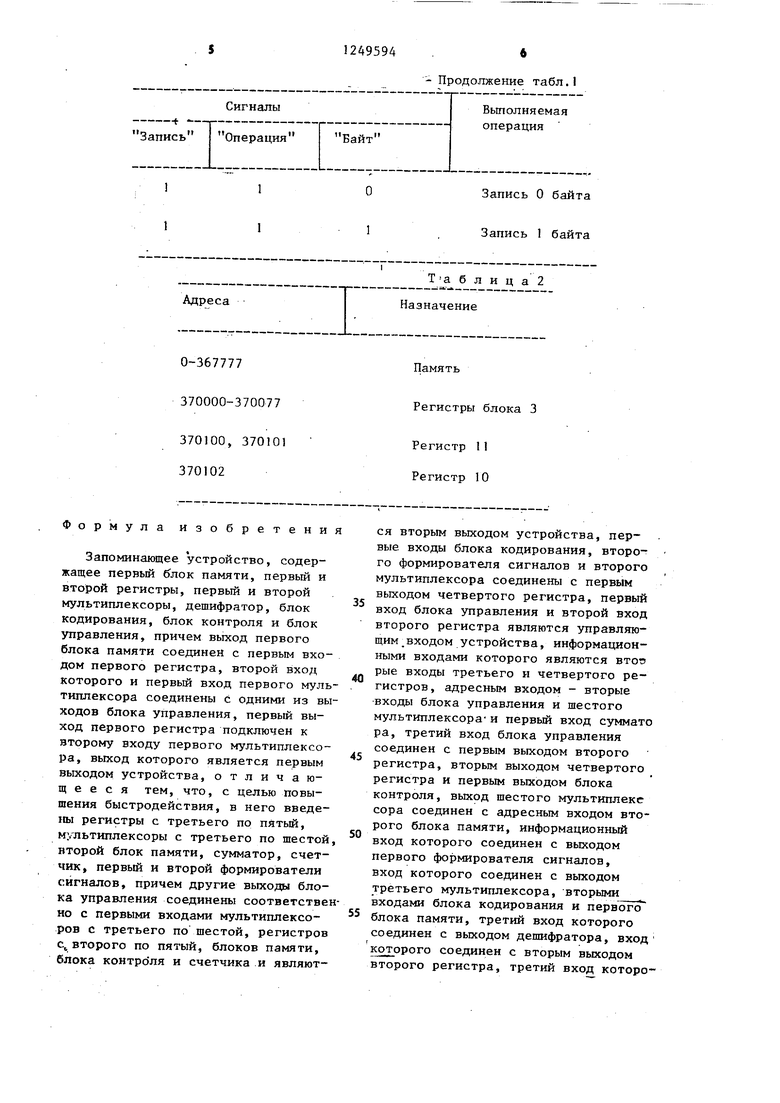

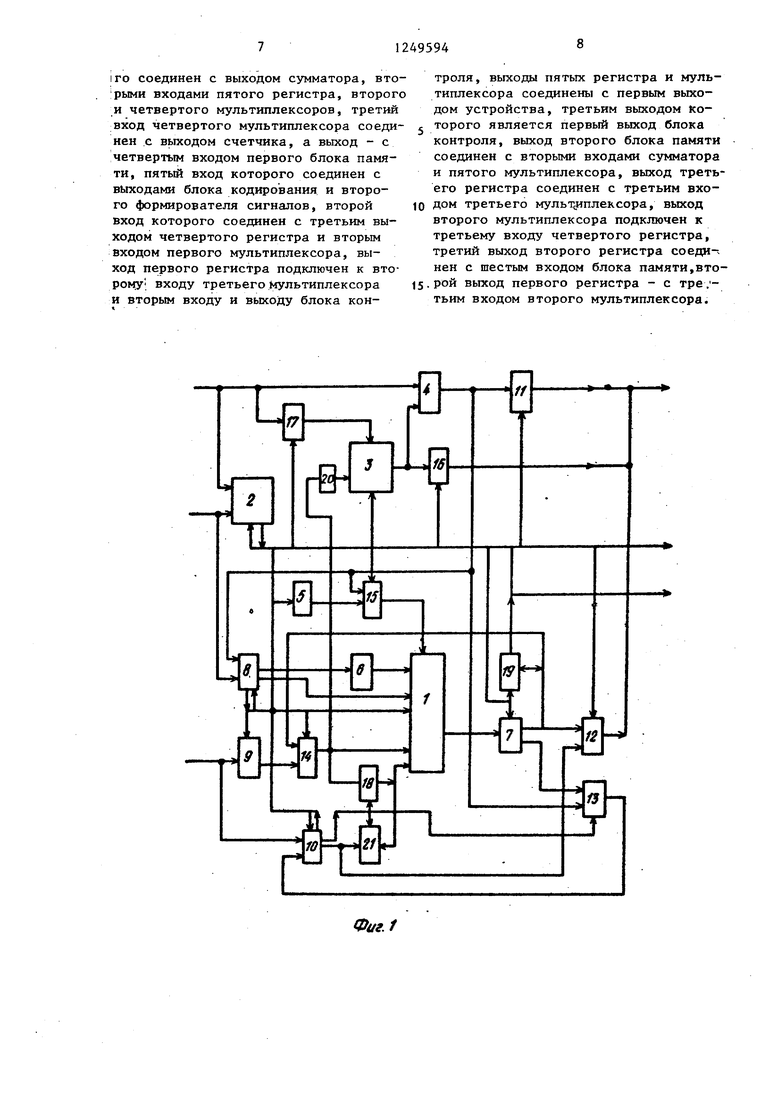

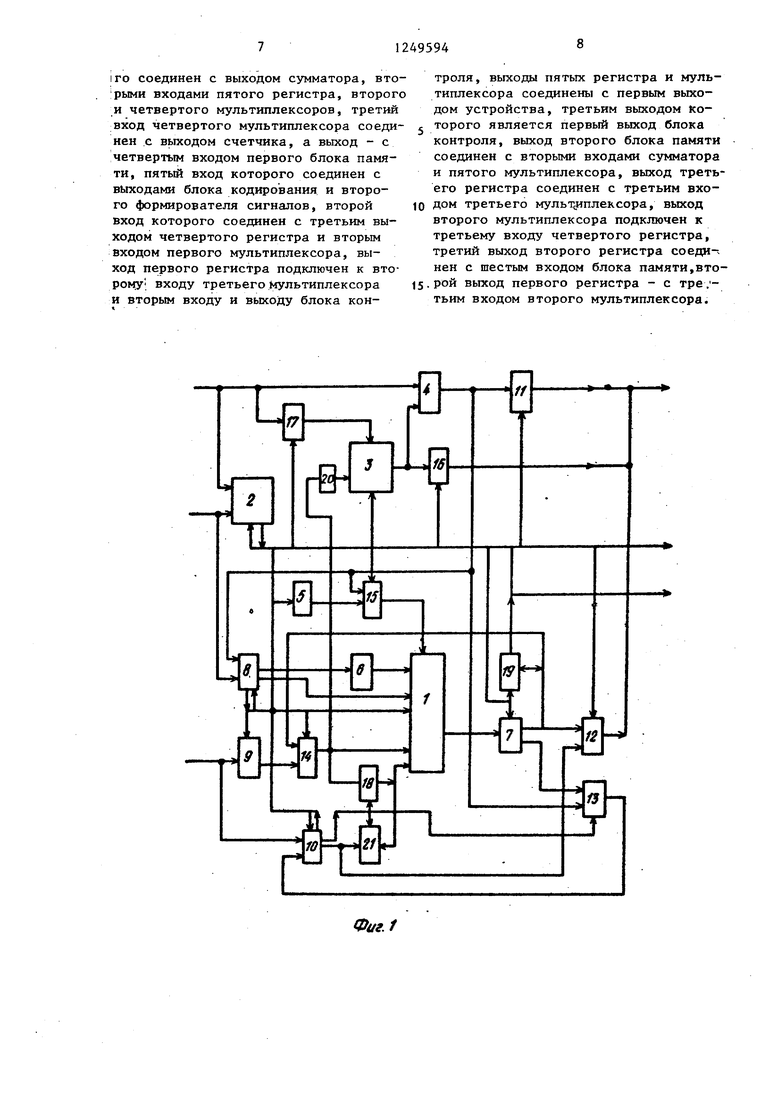

На фиг. 1 изображена структурная схема запоминающего устройства; на фиг. 2 - схема селектора режимов; на фиг. 3 - схема дешифратора операций; на фиг. 4 - схема дешифратора регистров.

Устройство (фиг. 1) содержит первый блок 1 памяти, блок 2 управления, второй блок 3 памяти, служащий для хранения начальных адресов страниц, сумматор 4, счетчик 5, дешифратор 6, первый 7, второй 8, третий 9, четвертый 10 и пятый 11 регистры, первьй 12, второй 13, третий 14, четвертый 15, пятый 16 и шестой 17 мультиплексоры, блок 18 кодирования, блок 19 контроля, первый 20 и второй 21 формирователи сигналов.

Блок 2 управления состоит из селектора режимов, дешифратора операции и дешифратора регистров.

Селектор режимов предназначен для выбора одного из режимов: обращение, регенерация.

Селектор режимов (фиг. 2) содержит кварцевый генератор 22 импульсов, триггеры 23 и 24, счетчик 25, элемент И-НЕ 26, элементы И 27-29, регистр 30, одновибратор 31, элемент И-НЕ 32, элемент НЕ 33, регистр 34, элементы И 35, элемент НЕ 36, элемент И 37, элемент НЕ 38 и элемент ИЛИ 39.

Дешифратор операций (фиг. 3) содержит элемент И-НЕ 40, элемент ИЛИ 41, элемент И 42, элемент ИЛИ-НЕ 43, элемент И-НЕ 44, элементы НЕ 45-47, элементы И 48 и 49, элементы И-НЕ 50 и 51, элемент И 52 и элемент ИЯИ-НЕ 53.

Дешифратор регистров (фиг. 4) со держит элемент ИЛИ 54, элемент И-НЕ 55, дешифратор 56, элемент НЕ 57, элементы ИЛИ 58 и 59, элемент И-НЕ 60 и элемент НЕ 61.

Запоминающее устройство работает следующим образом.

На входы устройства поступают управляющие сигналы Запрос, Запись, Операция, Байт и 17 разрядов адреса. На выходах блока 2 выбирается один из режимов: обраще- к памяти, обращение к регистрам, регенерация.

10

f5

249594 2

Назначение управляющих

и вьтолняемые операции описаны в

табл. 1 ,

Пример использования логических адресов описан в табл. 2.

Семнадцатиразрядный логический адрес, принятый на входе устройства, - преобразуется в 21-разрядный физичес кий адрес следующим образом.

В блок 3 предварительно записываются начальные адреса страниц памяти.

.При обращении к памяти пять старших разрядов логического адреса передаются через мультиплексор Л 7 и используются для выбора одного из регистров блока 3. Из этого регистра- считывается начальный адрес страницы памяти. Младшие 12 разрядов логического, адреса используются для определения смещения внутри страницы.

Физический адрес формируется на сумматоре 4 сложением начального 25 адреса и смещения и запоминается на регистре 11 . Старшие 5 разрядов фи зического адреса и управляюпще сигналы запоминаются на регистре 8. .Старшие разряды адреса служат для выбора модуля памяти блока 1 на дешифраторе 6 и выбора линейки микросхем внутри модуля.

Младшие семнадцать разрядов мультиплексируются на блоке 15, который формирует две посыпки: адрес строки и адрес столбца.

При операции Запись в память данные запоминаются на регистре 9 и передаются через мультиплексор 14.

Блок 18 формирует контрольные разряды по коду Хэмминга.

Блок 2 формирует строб адреса строки, строб адреса столбца, разрешение записи, сигнал Ответ, который выдается на выход устройст30

35

40

45

50

ва.

При операции Чтение памяти адрес и управляющие сигналы для блока памяти формируются также, как при записи.

Информация считывается из блока 1 памяти и фиксируется на регистре 7 и в блоке 19.

Блок I9 контроля проверяет пра- вильность считанного кода. При отсутствии ошибки данные с регистра 7 через коммутатор 12 поступают на выходы устройства.

Блок 2 формирует строб адреса строки, строб адреса столбца, разрешение записи, сигнал Ответ, который выдается на выход устройст

ва.

При операции Чтение памяти адрес и управляющие сигналы для блока памяти формируются также, как при записи.

Информация считывается из блока 1 памяти и фиксируется на регистре 7 и в блоке 19.

Блок I9 контроля проверяет пра- вильность считанного кода. При отсутствии ошибки данные с регистра 7 через коммутатор 12 поступают на выходы устройства.

3

При одиночной ошибке сигнал Одиночная ошибка выдается в блок 2 управления на элемент И 60, который формирует сигнал Разрешение коррекции, который включает в ыходы блока 19. Элемент НЕ 61 блока 2 выключает выходы регистра 7. Cкoppeкtиpoвaн- ные данные с выхода блока 19 через коммутатор 12 поступают на выходы устройства.

При двойной ошибке в блоке 19 формируется сигнал Двойная ошибка и выдается на выход устройства.

При операции Запись байта выполняется чтение слова по заданному адресу, затем с регистра 9 принимается один байт данных на коммутатор 14, ас регистра 7 - другой байт

Блок 18 формирует контрольные разряды. Таким образом, данные и контрольные разряды поступают в блок 1 памяти. При этом вьтолняется за- пись одного байта и регенерация другого. Запрос регенерации формируется в блоке 2 с помощью счетчика 25, триггера 24 и элемента И 26.

Признак режима регенерации в блоке 2 формируется с помощью элемента И 27 на третьем триггере регистра 30, после чего взводится первьй триг гер регистра 30 и запускается одно- вибратор 31, которьй формирует строб адреса регенерации. Текущий адрес регенерации формируется на счётчике 5 и передается через мультиплексор 15 в блок 1 памяти.

Наращивание адреса регенерации вьтолияется по заднему фронту строба адреса регенерации. Регистр 10 обеспечивает вьтолнение диагностических операций. Нулевой разряд регистра 10 отменяет коррекцию одиночных ошибок с целью обеспечения тесто вого контроля информационных разрядов блока 1.

Первый разряд регистра 10 отменяет формирование правильных контрольных разрядов и разрешает запись произвольно заданных контрольных разрядов из регистра 10 в блок 1 с целью

5

10

15

20

495944

обеспечения тестового контроля контрольных разрядов блока 1, а также имитации ошибок и проверки блока 19.

Разряды 2-7 регистра 10 служат для приема контрольных разрядов, считанных из памяти, или старших разрядов адреса при двойной ошибке, с целью локализации обнаруженной неисправности, а также для приема произвольных контрольных разрядов с информационного входа устройства.

Мультиплексор 13 передает адрес или данные на регистр 10 (в зависи- мости от кода первого разряда регист ра 10). Формирователь 21 вьшолняет передачу произвольных контрольных разрядов с регистра 10 в блок 1. При операции обращения к регистрам на шестом триггере регистра 30 блока 2 формируется признак режима обращения к регистрам. Дешифратор адреса 56 вьтолняет выбор регистра.

При чтении из регистра 11 его дан ные поступают на выход устройства. Регистр 11 служит для тестового контроля формирования физического адреса. При чтении из регистра 10 его данные поступают на выход устройства через мультиплексор 12. При обращении к блоку 3 памяти мультиплексор 17 передает младшие пять разрядов адреса на входы блока 3. При операции запись с элементов ИЛИ 58 и 59 блока 2 поступают сигналы записи соответственно в младшее или старшее слово блока 3, ас формирователя 20 поступают данные.

При операции чтения данные с выхода блока 3 поступают через мультиплексор 16 на выход устройства. Муль типлексор 16 выполняет вьщачу младшего или старшего ( в зависимости от младшего разряда адреса) слова, считанного из блока 3 на выход устройства.

25

0

5

0

5

При чтении регистров один из блоков 11, 16 и 12 (в зависимости от выбранного регистра) выводится из третьего состояния.

Т а б л и ц а 1

Адреса

0-367777 370000-370077

370100, 370101 370102

Формула изобретения

Запоминающее устройство, содержащее первый блок памяти, первый и второй регистры, первый и второй мультиплексоры, дешифратор, блок кодирования, блок контроля и блок управления, причем выход первого блока памяти соединен с первым входом первого регистра, второй вход которого и первый вход первого мультиплексора соединены с одними из выходов блока управления, первый выход первого регистра подключен к второму входу первого мультиплексора, выход которого является первым вькодом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены регистры с третьего по пйтьй, мультиплексоры с третьего по шестой второй блок памяти, сумматор, счетчик, первый и второй формирователи сигналов, причем другие выходы блока управления соединены соответственно с первыми входами мультиплексоров с третьего по шестой, регистров с. второго по пятый, блоков памяти, блока контроля и счетчика и являют- Продолжение табл.1

Запись О байта Запись 1 байта

Т а б л и ц а 2

Назначение

Память

Регистры блока 3

Регистр 1I Регистр 10

ся вторым выходом устройства, первые входы блока кодирования, второго формирователя сигналов и второго мультиплексора соединены с первым выходом четвертого регистра, первый вход блока управления и второй вход второго регистра являются управляющим входом устройства, информационными входами которого являются втоп рые входы третьего и четвертого регистров , адресным входом - вторые входы блока управления и шестого мультиплексора и первый вход суммато ра, третий вход блока управления соединен с первым выходом второго регистра, вторьм выходом четвертого регистра и первым выходом блока контроля, выход шестого мультиплекг сора соединен с адресным входом второго блока памяти, информационный вход которого соединен с выходом первого формирователя сигналов, вход которого соединен с выходом третьего мультиплексора, вторыми входами блока кодирования и первого блока памяти, третий вход которого соединен с выходом дешифратора, вход которого соединен с вторым выходом второго регистра, третий вход которо

I го соединен с выходом сумматора, вто- рыми входами пятого регистра, второго и четвертого мультиплексоров, третий вход четвертого мультиплексора соединен с вьпсодом счетчика, а выход - с четвертым входом первого блока памяти, пятый вход которого соединен с выходами блока кодирования и второго формирователя сигналов, второй вход которого соединен с третьим выходом четвертого регистра и вторым входом первого мультиплексора, выход первого регистра подключен к второму; входу третьего мультиплексора и вторым входу и выходу блока кон

троля, выходы пятых регистра и мультиплексора соединены с первым выходом устройства, третьим выходом которого является первый выход блока контроля, выход второго блока памяти соединен с вторыми входами сзгмматора и пятого мультиплексора, выход третьего регистра соединен с третьим входом третьего мульТ(Иплексора, выход второго мультиплексора подключен к третьему входу четвертого регистра, третий выход второго регистра соеди- нен с шестым входом блока памяти,второй выход первого регистра - с тре;- тьим входом второго мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Запоминающее устройство | 1987 |

|

SU1481865A1 |

| Устройство сопряжения для контроля блоков памяти | 1991 |

|

SU1836723A3 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1254498A2 |

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1985 |

|

SU1277214A1 |

, Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств повышенной надежности. Цель изобретения - повышение быстродействия устройства. Устройство со;держит блоки памяти, служащие для хранения данных и начальных адресов страниц, блок управления, сумматор для преобразования адреса, счетчик, формирующий адреса регенерации, дешифратор, регистры, мультиплексоры, блок кодирования, блок контроля. В устройстве осуществляется исправление одиночной ошибки и обнаружение двойной ошибки. Синхронный режим управления обеспечивает высокое быстродействие, т.к. при этом исключается запас времени, необходимый для перекрытия разброса параметров, присущего асинхроиным схемам. ,4 ил, 2 табл.

Фиг.1

Фиг. 2

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Запоминающее устройство с контролем | 1983 |

|

SU1120412A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-07—Публикация

1985-01-18—Подача