входом первого элемента И К-го элемента 2И-ИЛИ, первый вход первого элемента И каждой группы соединен с М-м разрядом регистра множимого, первый вход второго элемента И каждой группы соединен с выходом первого разряда регистра множимого, первый вход первого элемента И 8 -го элемен -а 2И-ИЛИ каждой группы соединен соответственно с (В+1)-м выходом регистра множимого (,...J первый вход второго элемента И t-го элемента 2Й-ИЛИ каждой группы соединен соответственно с -м выходом регистра множимого, прямой выход младшего разряда первой .группы разрядов регистра множителя соединен с вторыми входами первых элементов И элементов 2И-ИЛИ и вторыми входами второго элемента И первой группы, выход первого элемента И устройства соединен с вторыми входами вторнпс элементов И элементов 2И-ИЛИ и первого элемента И первой группы, выход К-го элемента 2И-ИЛИ устройства соединен с вторЫ1 И входами вторых элементов И элементов 2И-ИПИ и вторыми входами первого элемента И (1с-«-1)-й

группы, выход k-го полусумматора устройства соединен с вторыми, входами первых элементов И элементов 2И-ИЛИ и вторыми входами первых элементов И элементов 2И-ИЛИ и вторыми входами второго элемента И (К+1)-и грзшпы, выход первого и второго элемента И К-и группы соединен с вторыми входами соответственно (М+1)-го и первого полусумматоровk-и группы полусумматоров, выход Р-го элемента 2И-ИЛИ К-и группы соединен с вторым входом (€ + 1)-го полусумматора If-и группы, выход с -го полусумматора С -и группы соединен с (2К+й-2)-м весовым входом сумматора двухрядового кода Ц 1,.. .,(И+1), выходы первого и второго элемента И (11/2+1)-и группы соединены соответственно с (fH+W)-M и {H + l)-M весовыми вхада ас сумматора двухрядового кода, выход -го элемента 2И-Ш1И (М/2+1)-й группы соединен с СИ + 6)-м весов(Я4 входсж сум атора двухрядового кода, шина логической единицы устройства соединена с (М+2)-м и с (ftiH-2|t+1)-M весовыми входами сумматбраГ двухрядового кот да.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для умножения | 1989 |

|

SU1658148A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1989 |

|

SU1735842A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Устройство для умножения | 1981 |

|

SU991414A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

УСТРОЙСТВО ДЛЯ УЬЩОЖЕНИЯ, содержащее М -разряный регистр множимого, N -разрядный регистр множителя, сумматор двухрядового кода, параллельньй сумматор, регистр результата, причем разрядные выходы параллельного сумматора соединены с соответствующими входами регистра результата, отличающееся тем, что, с целью расширения области применения, в него введены элемент И, N/2 элементов 2И-ИПИ, N/2 полусумматоров, (//2+1) групп по два элемен-. та И и (М-1) элементов 2И-ИЛИ в каждой, М/2 групп полусумматоров по (М+1) полусумматоров в каждой, регистр множителя содержит (N/2+1) групп разрядов, причем первая группа разрядов содержит два младших разряда регистра множителя, j-я группа разрядов регистра множителя (j 2,..-,, ...,N/2+1) содержит по три разряда, причем старший разряд г-и группы регистра-множителя (i 1,...,S/2+1) равен по значению младшему разряду (|л-И)-й группы разрядов регистра множителя, выход старшего разряда первой группы разрядов регистра множителя соединен с первым входом элемента И и с (М+2) весовым входом сумматора двухрядового кода, инверсный выход млуадшего разряда первой группы разрядов регистра множителя соединен с вторым входом элемента И, инверс11ый выход старшего разряда первой группы разрядов регистра множителя соединен с первым весовым входом сумматора двухрядового кода и с первыми входами полусумматоров первой группы, выход старшего разряда (К+1)-й группы разрядов регистра множителя соединен с первым входом первого элемента И К-го элемента 2И-ИЛИ и с (M+2k+2)-M весовым входом сумматора двухрядового кода (,.,., (Л ,..,М/2), инверсный выход старшего разряда (К+О-й группы разрядов регистра множителя соединен с первым входом второго элемента И К-го элемента 2И-ИЛИ, с первыми входами по- ;Лусумматоров

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в специализированных дафровых арифметических устройствах.

i Известны устройства для умножения двоичного числа (множимого) на другое двоичное число (множитель), использу ющие для формирования произведения ряд сложений-вычитаний кратных множимого .

Наиболее близким по технической сущности к изобретению является устройство для умножения, содержащее perHctp множителя, регистр множимого, сумматор двухрядового кода, сумматор приведения двухрядового кода в однорядовый, регистр результата L2J.

Однако чтобы получить произведение дополнительного кода множителя и кода множимого в известное устройство необходимо ввести специальный

блок преобразования прямого кода множителя в дополнительный, что уменьшает быстродействие устройства и требует допопнительиык здтрат оборудования.

Цель изобретения - расширение области применения устройства.

Поставленная цель достигается тем что в устройство для умножения/ содержащее М-разрядный регистр множимого, N -разрядный регистр множителя, сумматор двузфяд ого кода, паралпелъны cywuaTopf регистр результата причем разрядные выхода параллельного сумматора соединены с соответствукщюш В1содами регистра результата, введены элемент И,Н/2 элементов 2И-ЩШ, -К/2 полусумматоров,, (N/2+1) групп по два элемента И и(1Ц-1) элементов 2И-ИШ в каждой, .М/2 групп полусумматЬров по (1+1) полусумматоров в , pjerHCTp множителя содержит (N/2+1) групп разрядов, приче первая группа разрядов содержит два младших разряда регистра множителя, 4 -я группа разрядов регистра множителя (j 2,...,N/2+1) содержит по три разряда, причем старший разряд i-й группы регистра множителя ( 1,. ...,N/2+1) равен по значению младшему разряду (4+1)-и группы разрядов регистра множителя, выход старшего разряда первой группы разрядов регистра множителя соединен с первым входом элемента И и с (М+2) весовым входом сумматора двухрядового кода, инверсный выход младшего разряда первой группы разрядов регистра множителя соединен с вторым входом элемента И-, инверсный выход старшего разряда первой группы разрядов регистра множителя соединен с первым весовьм входом сут матора двухрядового кода и с первыми входами полусумматоров первой группы, выход старшего разряда (+1)-й группы разрядов регистра множителя соединен с первым входом первого элемента И If-го элемента 2И-ИПИ и с (M+2k+2)-:M весовьш входом сумматора двухрядового кода (,...,N/2), инверсный выход старшего разряда (k+1)-M группы разрядов регистра множителя соединен с первьм входом второго элемента И 1 -го элемента 2И-ИЛИ, с первюш входами полусумматоров ()-A группы полусуюоторов и с ()-м весовым входом сумматора двухрядовог кода, выход второго разряда (k.+1)-u группы разрядов регистра множителя соединен с вторым входом второго элемента И k -го элемента 2И-ШШ и с первым входом k-ro полусугоштора, инверсный выход второго разряда (+1)-й группы разрядов регистра множителя соединен с вторым входом первого элемента И k-го элемента 2И-ИЛИ, выход )шадшего разряда{К+1) - ft

V. группы разрядов регистра мнсокителя сое динен с третьим вХодом второго элемента И k-го элемента 2И-ИЛИ и с вторым входом k-го полусумматора, инверсный выход младшего разряда (К+1)й группы разрядов регистра мно .жителя соединен с третьим входом первого элемента И k-ro элемента 2И-ИЛИ, первый вход первого элемента И каждой группы соединен с М-м разрядом регистра множимого, первый вхЪд BTopforo элемента И каждой группы соединен с выходом первого разряда регистра множимого, первый вход первого элемента И 6 го элемента 2И-ИЛИ каждой группы соединен соответственно с (6+1)-м выходом регистр множимого (Е 1,...,М-1), первый вход второго элемента И Е-го элемента 2И-ИЛИ каящой группы соединен соответственно с С -м выходом регистр множимого, прямой выход младшего разряда первой группы разрядов регистра множителя соединен с вторыми входами первых элементов И элементов 2И-ИПИ и вторыми входами второго элемента И первой группы, выход первого элемента И устройства соединен с вторыми входами вторых элементов И элементов 2И-ИПИ и первого элемента И первой группы, выход k-го элемента )2И-РШИ устройства соединен с вторыми входами вторых элементов И элементов 2И-ИЛИ и вторыми входами первого .элемента И (У; + 1)-й группы, -выход k-г полусумматора устройства соединен с вторыми входами первых элементов И элементов 2И-ИЛИ и вторыми входами первых элементов И элементов 2И-ИЛИ и вторыми входами второго элемента И Ос+1)-й группы, выход первого и второго элемента И k.-й группы соединен с вторыми входами соответственно {М+1)-го и первого полусумматоровk-ой группы полусумматоров, выход В-го элемента 2И-ШШ 1(-й группы соединен с вторым входом (Е+1)-го полусумматора k-й группы, выход (-го полусумматора k-и группы соединен с (21:+(-2)-м весовым входом сумматора двухрядового кода ( 1,.. .,М+1), выходы первого и второго элемента И (.N/2+1)-и группы соединены соответственно с (М+Ю-м и (N+1)-M весовь ш входами сумматора двухрядового кода,, выход 8-го элемента 2И-ИЛИ (Л/2+1)-й группы соединен с (11+в)-м весовьм входом сумматора двухрядового кода, шина логической единицы устройства соединена с (М+2)-м и с (M+2k+1)-M весовыми входами сумматора двухрядового кода.

На чертеже представлена блок-схема устройства для умножения.

Устройство содержит регистр 1 множителя, регистр 2 множимого, блок: 3 аиализа разрядов множителя и фор,мирования кратных множимого, содержащий двухвходовой элемент И (3-1), ..(Н/2) элементов 2И-ШШ (3-2,3-ji),

получения произведения дополнительного кода M--f на другое двоичное число обоцтись без блока предварительного перевода прямого кода М в дополнител| ный (реализуемый инверсией прямого кода и суммированием его с единицей дополнительного кода),что уменьшает йремя умножения и экономит оборудование при использовании изоб-

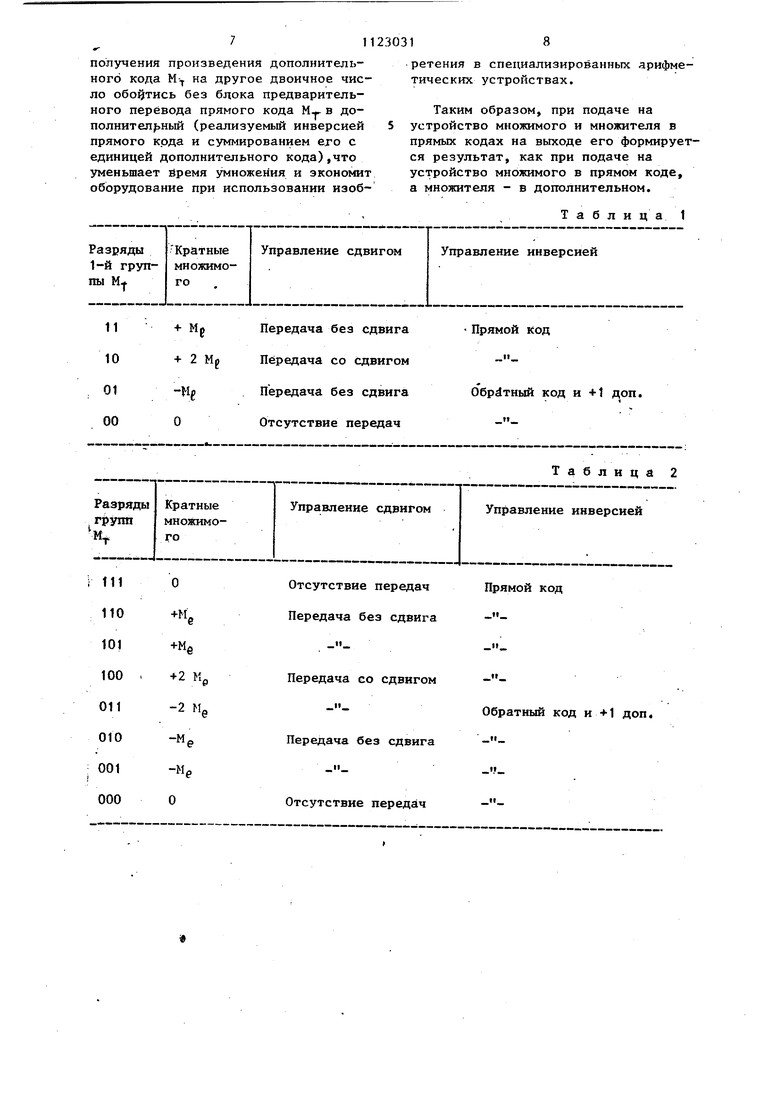

11 МрПередача без сдвига

10+ 2 МрПередача со сдвигом

01-ЩПередача без сдвига

00ООтсутствие передач

til

о

Отсутствие передач 110

+Ме

Передача без сдвига 101 || +Ме 100

+2 Mg

Передача со сдвигом Oil -2М,

п 010

-Me

Передача без сдвига 001 11

-Мй

000

Отсутствие передач

ретения в специализированных арифметических устройствах.

Таким образом, при подаче на устройство множимого и множителя в прямых кодах на выходе его формируется результат, как при подаче на устройство множимого в прямом коде, а множителя - в дополнительном.

Таблица 1

Прямой код

Обратный код и +1 доп.

Таблица 2

Прямой код

Обратный код и +1 доп. ||

11

г44-Ш

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гаврилов Ю.В., Пучко А.Н | |||

| Арифметические устройства быстродействующих ЭЦВМ | |||

| М., Советское радио, 1970, с | |||

| Способ закалки пил | 1915 |

|

SU140A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-07—Публикация

1982-08-18—Подача