Изобретение откосится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств з этих областях.

Известны дискретные асинхронные устройства,, содержащие блок элементов па- мяти и комбинационные цепи, реализующие функции выходов и переключений (1). Недостатком этих устройств является отсутствие четкой синхронизации срабатывания элементов, что в свою очередь повышает вероятность возникновения риска сбоя, для устранения которого требуется сложное распределение и учет задержек в критических точках асинхронных схем..

Известны синхронные дискретные устройства, в которых исключение риска сбоя за счет неравенства задержки распространения сигналов в логических цепях обеспечивается синхронизирующими сигналами (2). Недостатком этих устройств является то.

что сбои в блоке памяти полностью нарушают алгоритмы функционирования.

Известно избыточно-кодированное синхронное дискретное устройство, содержащее комбинационный блок, блок памяти и восстанавливающий орган, которое позволяет скорректировать часть сбоев (3).

По своей технической сущности и достигаемому положительному эффекту это устройство является наиболее близким к изобретению. Недостатком известного устройства является то, что в его блоке памяти могут накапливаться сбои в интервалах между синхронизирующими сигналами. Это, в свою очередь, нарушает процесс восстановления информации восстанавливающим органом и снижает устойчивость к сбоям.

Целью изобретения является повышение устойчивости к сбоям. Поставленная цель достигается тем что в дискретное устройство, содержащее комбинационный блок, блок памяти и восстанавливающий орел С

-ч со о

N

00

VJ

тан, вход которого связан с выходом блока памяти, а выход - с одним из входов комбинационного блока, другой вход которого является информационным входом устройства, а один из выходов - информационным выходом устройства, снабженного также тактовым входом, введены коммута- тор„.;элемент ИЛИ, элемент задержки, эле- ме$т И, инвертор и тактовый генератор, выход которого подключен к одному из входов элемента И, другой вход которого через инвертор связан с тактовым входом устройства, а выход - с одним из входов элемента ИЛИ, другой вход которого через элемент, задержки подсоединен к тактовому входу устройства, а выход - к синхронизирующему входу блока памяти, вход начальной установки которого является входом начальной установки устройства, а информационный вход соединен с выходом коммутатора, первый и второй информационные входы которого подключены, соответственно ко второму выходу комбинационного блока и к выходу восстанавливающего органа, а управляющий вход коммутатора соединен с тактовым входом устройства.

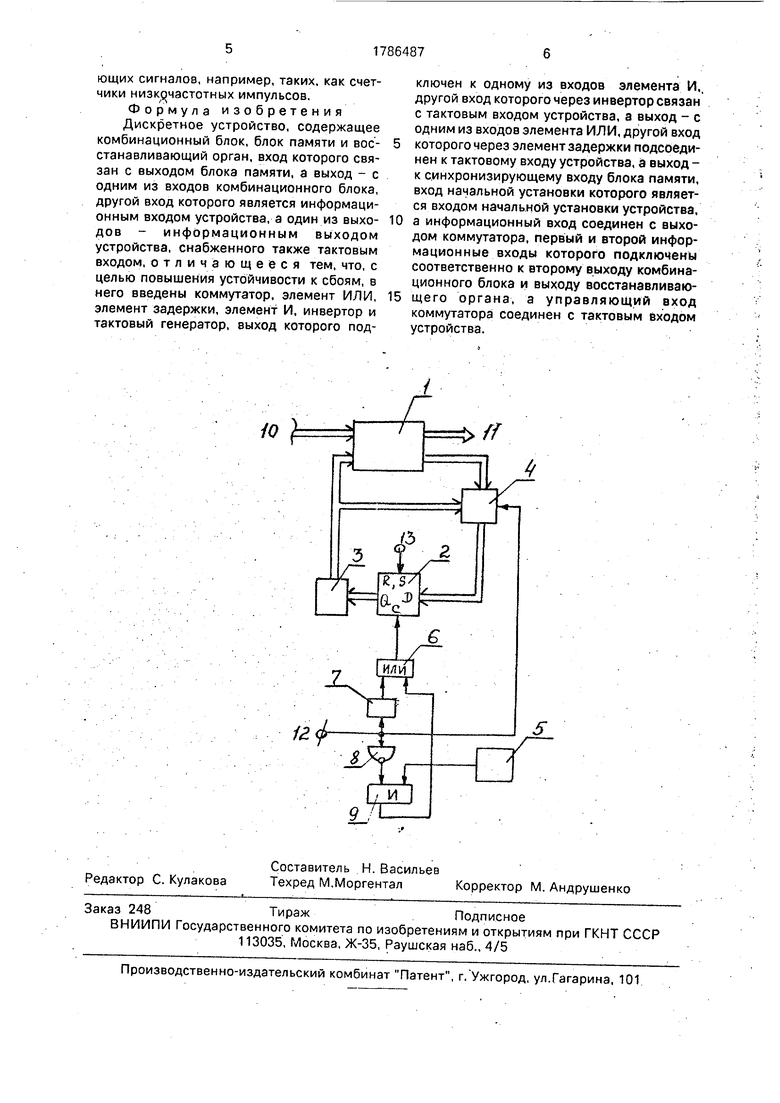

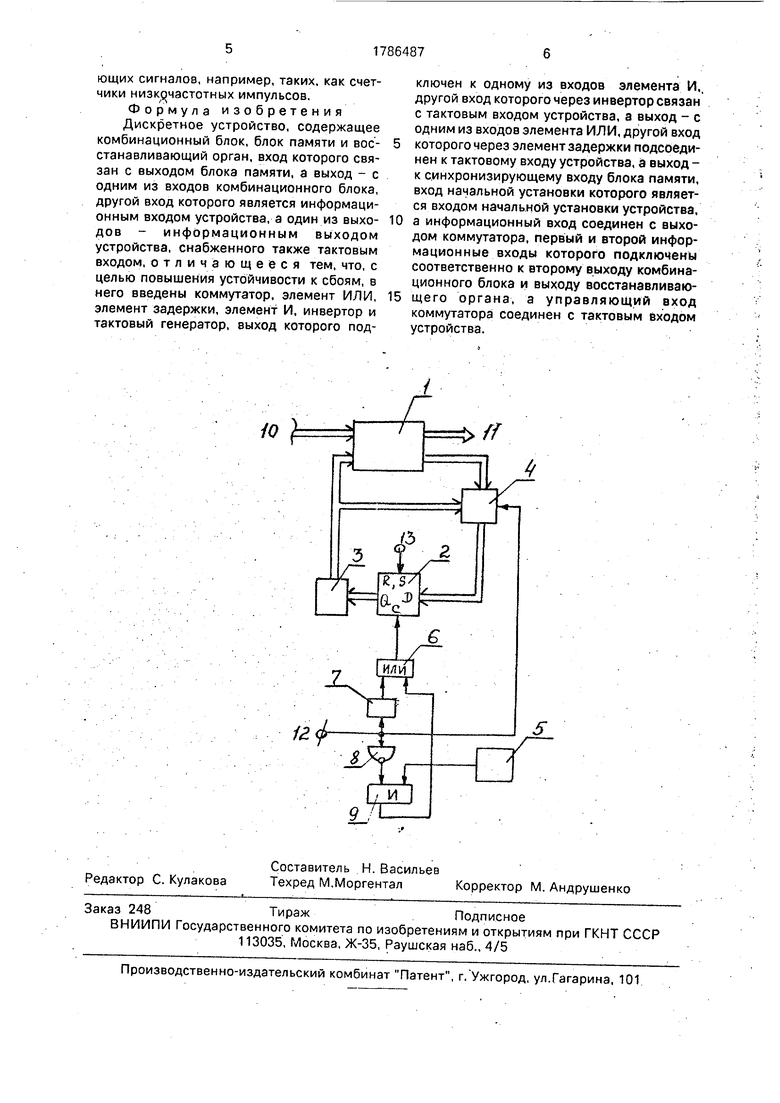

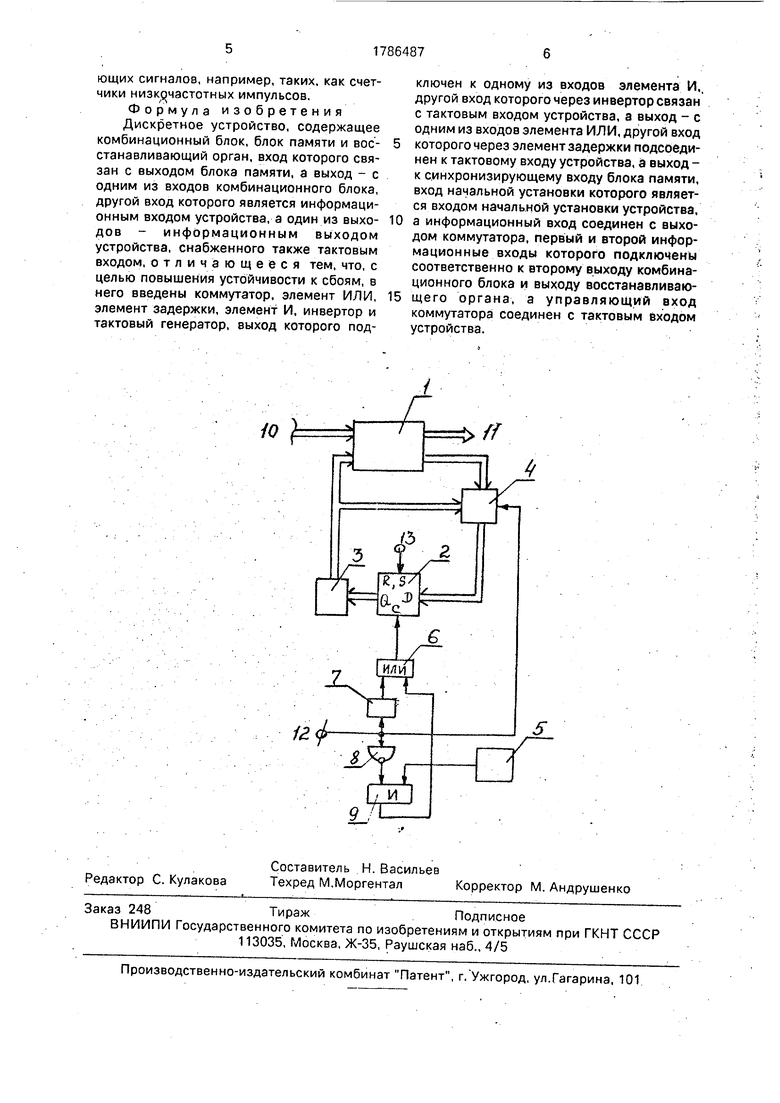

На чертеже представлена блок-схема дискретного устройства.

Устройство содержит комбинационный блок 1, блок 2 памяти, восстанавливающий орган 3, коммутатор 4, тактовый генератор 5, элемент ИЛИ 6, элемент 7 задержки, инвертор 8, элемент И 9, вход 10, выход 11, тактовый вход 12 и установочный вход 13.

. Вход 10 и выход 11 соединены соответственно с первым входом и выходом комбинационного блока 1. Выход блока 2 памяти через восстанавливающий орган 3 связан со вторым входом комбинационного блока 1 и первым входом коммутатора 4, выход которого соединен с информационным входом блока 2 памяти. Второй выход комбина- ционного блока 1 соединен со вторым входом коммутатора 4. Вход 13 соединен с установочным входом блока 2 памяти. Тактовый вход 12 через элемент 7 задержки связан с первым входом элемента ИЛИ 6 и через инвертор 8 - с первым входом элемента И 9, выход которого соединен со вторым входом элемента ИЛИ 6, выход которого соединен с синхронизирующим входом блока 2 памяти. Управляющий вход коммутатора 4 соединен с входом 12. Выход тактового генератора 5 соединен со вторым входом элемента И 9.

Перед началом работы устройство приводится в исходное состояние сигналом по входу 13.

При поступлении тактовых сигналов на вход 12 устройство производит преобразование входной информации в выходную. Результатом преобразования является код

выходе 11. При этом в режиме переключения передний фронт тактового сигнала снЈ- чала переключает коммутатор 4 в режим пропускания сигналов с выхода блока 1,а затем, через время, необходимое для уста0 новления переходных процессов, на ронизирующий вход блока 2, которЦй производит запоминание входной информации. В статическом режиме коммутатор 4 пропускает информацию с выхода восста5 навливающего органа 3. При этом последовательность импульсов с генератора .5 поступает на синхронизирующий вход блЬ- ка 2, осуществляя в нем непрерывное подтверждение информации.j

0 Ввиду того, что восстановленное орф- ном 3 состояние непрерывно вводится;в блок 2, производится активное многократное исправление сбоев в течение периода тактовой частоты. Для надежной работы ус5 тройства требуется обеспечить Тги/т S J2, где fT, fi-и тактовая частота и частота тактового генератора 5. Блок 2 памяти является регистром с шиной начальной установки;и шиной синхронизации. Разрядность perncfr0 pa соответствует длине избыточного код|а, который используется в данном дискретном устройстве. Восстанавливающий орган 3 я|з- ляется схемой комбинационного типа, котр- рая осуществляет преобразование

5 избыточного кода с блока 2 памяти,.содержащего ошибки, в исправленный код. Например, если избыточный код является кодом с повторением, то вбсстанавлива - щий орган осуществляет покомпонентное

0 голосование входной информации, Коммутатор 4 представляет собой набор управляемых ячеек, выполняющих функцию F АВ + АВ, где А - управляющий вход; В.В - соответствующие информац 45 онные входы.

.Комбинационный блок 1 реализует лэ- гические функции выходов и переходов устройства и может быть выделен в любсй конкретной реализации дискретного усг0 ройства. : .,.. .; ;, ,..;

Сравнивая работу данного устройства с известным, можно отметить, что устойчивость к сбоям данного устройства выше BBI- ду того, что оно исключает возможное ъ

5 накопления сбоев в процессе работы.

Устройство может быть эффективно и :- пользовано при построении цифровых систем, работавших в условиях повышенных помех. Особенно это относится к устройствам с большой скважностью синхронизир ющих сигналов, например, таких, как счетчики низкочастотных импульсов.

Формула изобретения Дискретное устройство, содержащее комбинационный блок, блок памяти и восстанавливающий орган, вход которого связан с выходом блока памяти, а выход - с одним из входов комбинационного блока, другой вход которого является информационным входом устройства, а один из выходов - информационным выходом устройства, снабженного также тактовым входом, отличающееся тем, что, с целью повышения устойчивости к сбоям, в него введены коммутатор, элемент ИЛИ, элемент задержки, элемент И, инвертор и тактовый генератор, выход которого под0

5

ключей к одному из входов элемента И,, другой вход которого через инвертор связан с тактовым входом устройства, а выход - с одним из входов элемента ИЛИ, другой вход которого через элемент задержки подсоединен к тактовому входу устройства, а выход - к синхронизирующему входу блока памяти, вход начальной установки которого является входом начальной установки устройства, а информационный вход соединен с выходом коммутатора, первый и второй информационные входы которого подключены соответственно к второму выходу комбинационного блока и выходу восстанавливающего органа, а управляющий вход коммутатора соединен с тактовым входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронное дискретное устройство | 1987 |

|

SU1786488A1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ ПРЕДУПРЕЖДЕНИЯ О ВОЗНИКНОВЕНИИ СЕЙСМИЧЕСКИХ ТОЛЧКОВ И ЦУНАМИ | 2008 |

|

RU2363963C1 |

| МОДУЛЯТОР ДИСКРЕТНОГО СИГНАЛА ПО ВРЕМЕННОМУ ПОЛОЖЕНИЮ | 2018 |

|

RU2677358C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 2020 |

|

RU2722462C1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение устойчивости к сбоям -- достигается тем, что в дискретное устройство, содержащее комбинационный блок, блок памяти и восстанавливающий орган, введены коммутатор, элемент ИЛИ, элемент задержки, элемент 14, инвертор, тактовый генератор, обеспечивающие исключение возможности накопления сбоев в процессе работы устройства. 1 ил.

Авторы

Даты

1993-01-07—Публикация

1987-04-06—Подача