Изобретение относится к накоплению информации, а именно к устройствам для контроля аппаратуры цифровой магнитной записи: накопителей на магнитных дисках и лентах.

Цель изобретения - повышение достоверности контроля динамических характеристик системы синхронизации.

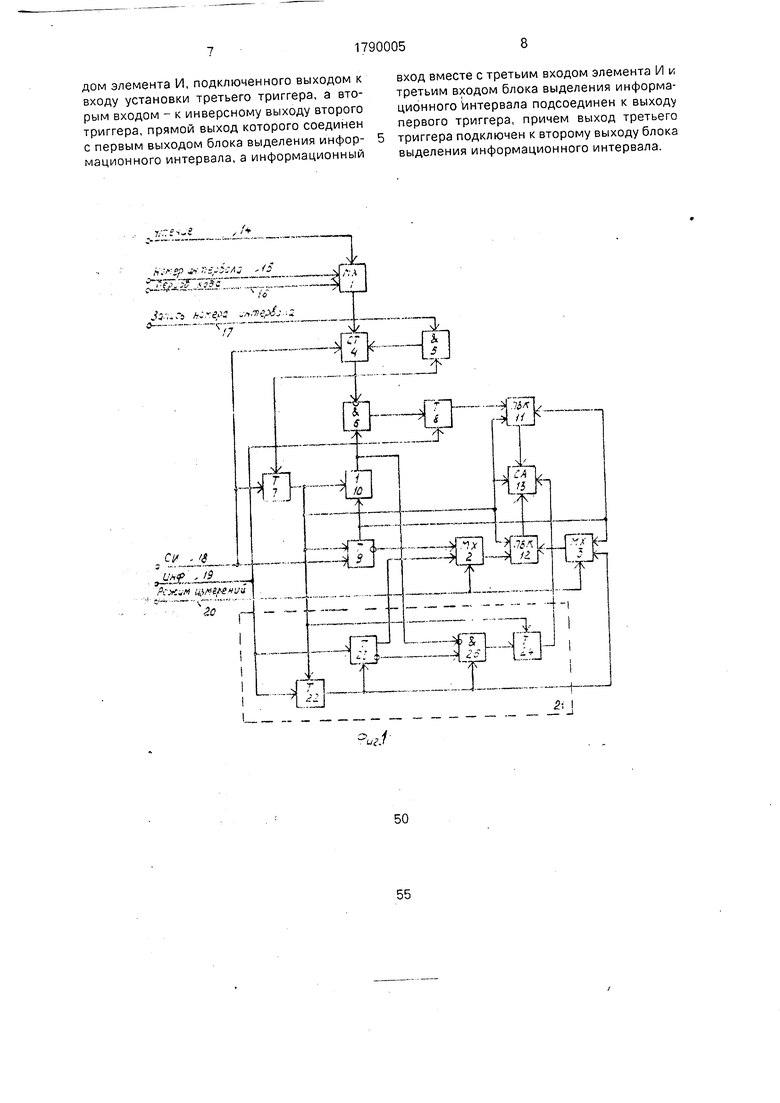

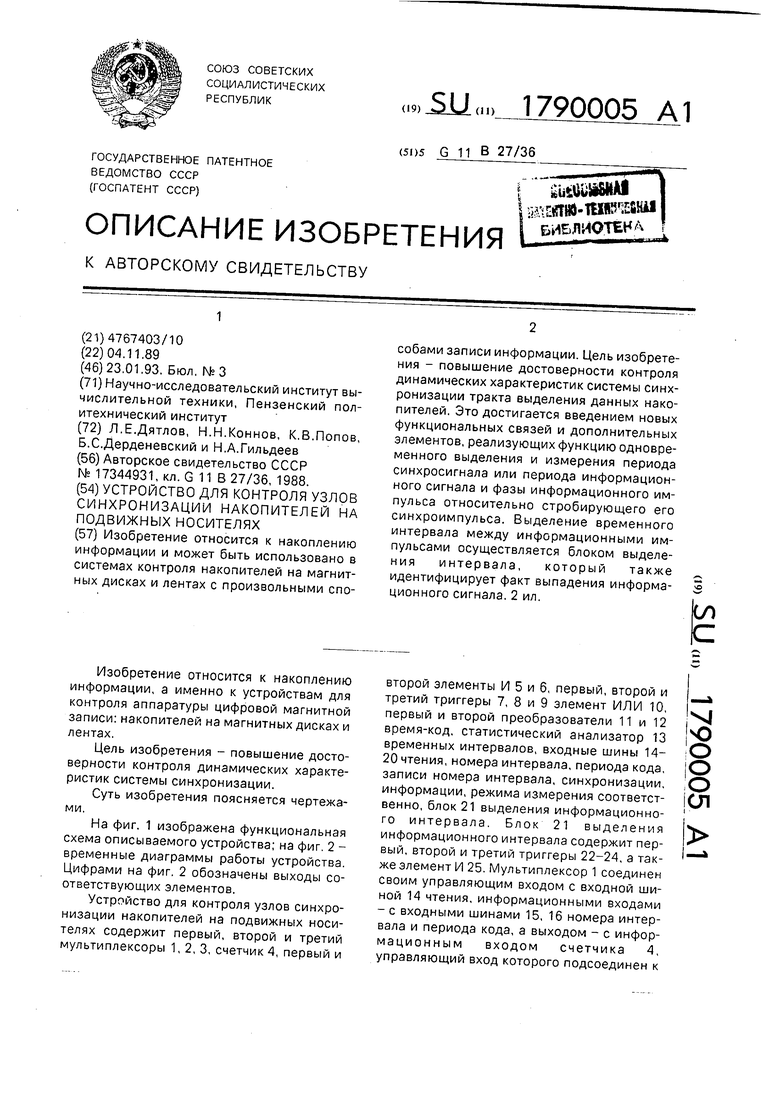

Суть изобретения поясняется чертежами.

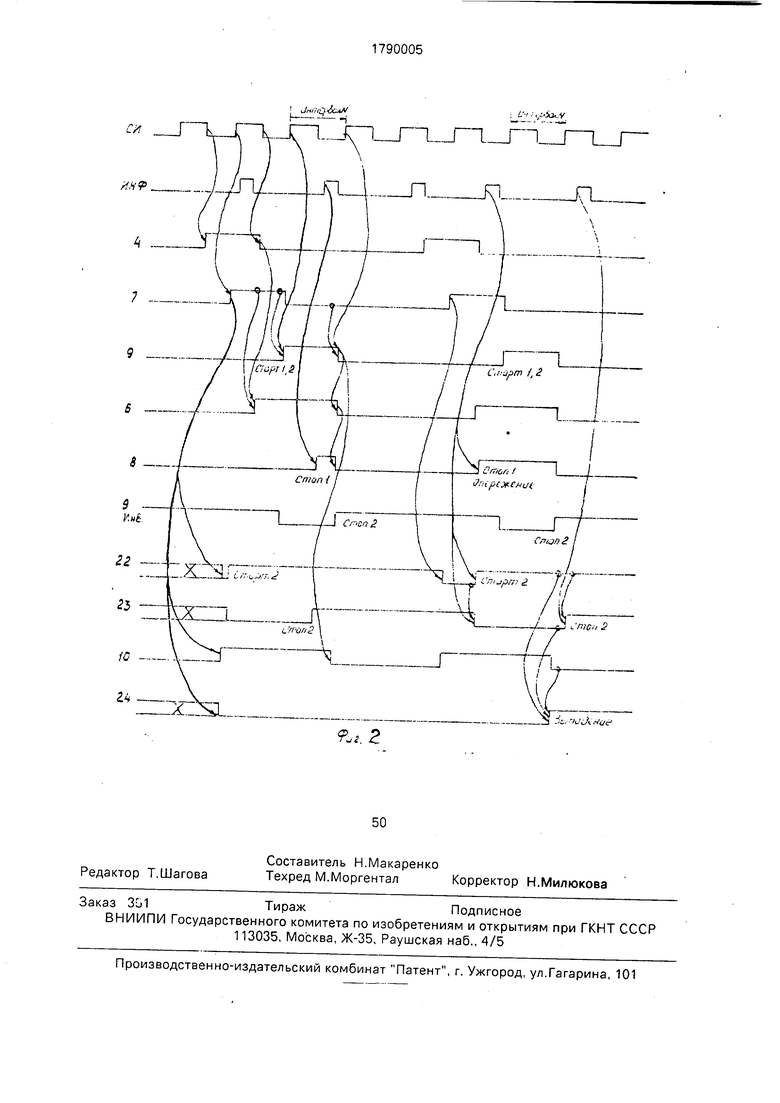

На фиг. 1 изображена функциональная схема описываемого устройства; на фиг. 2 - временные диаграммы работы устройства. Цифрами на фиг, 2 обозначены выходы соответствующих элементов.

Устройство для контроля узлов синхронизации накопителей на подвижных носителях содержит первый, второй и третий мультиплексоры 1, 2, 3, счетчик 4, первый и

второй элементы И 5 и 6, первый, второй и третий триггеры 7, 8 и 9 элемент ИЛИ 10, первый и второй преобразователи 11 и 12 время-код, статистический анализатор 13 временных интервалов, входные шины 14- 20 чтения, номера интервала, периода кода, записи номера интервала, синхронизации, информации, режима измерения соответственно, блок 21 выделения информационного интервала. Блок 21 выделения информационного интервала содержит первый, второй и третий триггеры 22-24, а также элемент И 25. Мультиплексор 1 соединен своим управляющим входом с входной шиной 14 чтения, информационными входами - с входными шинами 15, 16 номера интервала и периода кода, а выходом - с информационным входом счетчика 4, управляющий вход которого подсоединен к

ч ю о о о

1СЛ

выходу элемента И 5, снабженного входной шиной 17 записи номера интервала. Входная шина 18 синхронизации подключена к входу занесения триггера 7, к счетному входу счетчика 4, выход которого подсоединен к информационному входу триггера 7, инверсному входу элемента И 6 I втор омУ входу элемента И 5. Выходы преобразователей 11 и 12 подключены к информационным входам статистического анализатора 13. Входная шина 20 режима измерений подсоединена к управляющим входам 2-го и 3-го мультиплексоров. Вход занесения триггера 9 соединен с входной шиной 18 синхронизации, информационный вход - с выходом триггера 7, инверс- ный выход - с первым входом мультиплексора 2, а прямой выход - с вторым входом элемента ИЛИ 10, первый вход которого подключен к выходу триггера 7, а выход - к прямому входу элемента И 6, соединенного своим входом с входом сброса триггера 8. Вход установки триггера 8 подключен к входной шине 19 информации, а выход - к стоповому входу преобразователя 11 время-код, стартовый вход которого соединен с прямым выходом триггера 9, а вход начального сброса вместе с аналогичными входами статистического анализатора 13 временных интервалов и преобразователя 12 время-код подключен к выходу триггера 7. Мультиплексор 3 соединен первым информационным входом с прямым выходом триггера 9, а выходом - со стартовым входом преобразователя 12, стоповый вход которого подключен к выходу мультиплексора 2. Блок 2 выделения информационного интервала подсоединен своими тремя входами соответственно к входной шине 19 информации, к выходу триггера 7 и к выходу элемента ИЛИ 10, а тремя выходами - соответственно к второму входу мультиплексора 2, к третьему информационному входу статистического анализатора 13 временных интервалов и к второму информационному входу мультиплексора 3. В блоке 21 вход установки триггера 20 вместе с входом занесения триггера 23 подключен к первому входу блока выделения информационного интервала, второй вход которого соединен с входами сброса 22 триггеров 22 и 24, а третий - с первым (инверсным) входом элемента И 25, подключенного выходом к входу установки триггера 24, а вторым входом - к инверсному выходу триггера 23, прямой выход которого соединен с первым выходом блока 21, а информационный вход вместе с третьим входом элемента И 25 и третьим

выходом блока 21 подсоединен к выходу первого триггера 22, причем выход третьего триггера 24 подключен к второму выходу блока 21.

Устройство для контроля узлов синхронизации накопителей на подвижных носителях работает следующим образом.

Выделение интервала из входной последовательности синхроимпульсов прово- 0 дится при помощи мультиплексора 1, счетчика 4 и первого элемента И 5. При этом на входную шину номера интервала 15 подается двоичный код N - 2, N - номер исследуемого интервала синхропоследова5 тельности,

По переднему фронту N - 1 такта синх- ропоследовательности триггер 7 переписывает информацию с выхода переноса счетчика 2, принимает единичное состоя0 ние. С появлением переднего фронта на выходе триггера 7 начинается новый цикл измерений. При этом происходит начальный сброс преобразователей 11 и 12 время- код и статистического анализатора 13

5 временных интервалов, триггеров 22 и 24 блока выделения информационного интервала. Триггеры 8 и 9 также находятся в сбро- шенном состоянии, триггер 23 блока выделения информационного интервала в

0 общем случае может находиться в любом состоянии. Измерение фазы информационного импульса относительно стробирующе- го его синхроимпульса производится преобразователем 11 время-код. Выделе5 ние N-го такта синхропоследовательности осуществляется триггером 9, который работает как элемент задержки на 1 такт информации с триггера 7. Передний фронт с триггера 9 воспринимается преобразовате0 лем 11 время-код как стартовый сигнал. Следует отметить, что информационный сигнал может опережать соответствующий ему синхроимпульс. В этом случае фаза между ними является отрицательной. Чтобы

5 учесть эту ситуацию, измерение фазы может начинаться на полтакта раньше выделенного интервала. Окно длиною в 1,5 такта формируется элементом И 6, выход которого подключен к асинхронному входу сброса

0 триггера 8. С приходом информационного импульса во время действий окна триггер 8 переходит в единичное состояние, что является стоповым сигналом для преобразователя 11 время-код. Если стоповый сигнал

5 пришел раньше стартового, значит фаза отрицательна. Триггер 8 исключает возможность многократной выдачи стоповых сигналов в случае, если во время действия окна придет несколько информационных импульсов.

Преобразователь 12 время-код предназначен для измерения:

1) периода синхросигнала в N-M его такте;

3) временного интервала между информационными импульсами для М-го такта синхросигнала.

Задание режима измерения при этом осуществляется по соответствующей входной шине 20, которая управляет мульти- .плексорами 2 и 3, коммутирующими стартовый и стоповый входы преобразователя 42 время-код на те части схемы, которые отвечают за выделение вышеназванных временных интервалов. Выделение временного интервала между информационными импульсами осуществляется блоком 21 выделения информационного интервала в окне, обхватывающем N и N -1 такты синхро- последовательности. Для выделения этого окна используется элемент ИЛИ 10. С приходом первого информационного импульса

триггер 22 принимает единичное состояние, выдавая тем самым стартовый сигнал на преобразователь 12 время-код. По переднему фронту следующего сигнала информации, единица с выхода триггера 22

переписывается на триггер 23, измерение временного интервала прекращается. В случае выпадения информационного сигнала, к моменту окончания окна с элемента ИЛИ 10, триггер 22 установится в единичное

состояние, а триггер 23 будет сброшен. Такая ситуация дешифрируется элементом 25 И, при этом триггер 24 устанавливается в единицу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Преобразователь время-амплитуда импульсов | 1987 |

|

SU1444949A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1984 |

|

SU1167647A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для тактовой синхронизации канала цифровой магнитной записи-воспроизведения | 1990 |

|

SU1767530A2 |

| УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ ИЗМЕРИТЕЛЯ ИСКАЖЕНИЙ СТАРТСТОПНЫХ ТЕЛЕГРАФНЫХ СИГНАЛОВ | 1971 |

|

SU320073A1 |

| Статистический анализатор | 1988 |

|

SU1735870A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

Изобретение относится к накоплению информации и может быть использовано в системах контроля накопителей на магнитных дисках и лентах с произвольными способами записи информации. Цель изобретения - повышение достоверности контроля динамических характеристик системы синхронизации тракта выделения данных накопителей. Это достигается введением новых функциональных связей и дополнительных элементов, реализующих функцию одновременного выделения и измерения периода синхросигнала или периода информационного сигнала и фазы информационного импульса относительно стробирующего его синхроимпульса. Выделение временного интервала между информационными импульсами осуществляется блоком выделения интервала, который также идентифицирует факт выпадения информационного сигнала.2 ил. 00

Формула изобретения 1. Устройство для контроля узлов синхронизации накопителей на подвижных носителях, содержащее входную шину чтения, соединенную с управляющим входом первого мультиплексора, информационные входы которого подключены к входным шинам номера интервала и периода кода, а выход - к информационному входу счетчика, управляющий вход которого подсоединен к выходу первого элемента И, снабженного входной шиной записи номера интервала, входную шину информации, входную шину синхронизации, подключенную к счетному входу счетчика, выход которого подсоединен к информационному входу первого триггера и к второму входу первого элемента И, второй и третий триггеры, первый и второй преобразователи время-код, подключенные выходами к информационным входам статистического анализатора временных интервалов, а входы начального сброса которых объединены с одноименным входом статического анализатора, входную шину режима измерений, подсоединенную к управляющему входу второго мультиплексора, и элемент ИЛИ, отличающееся тем, что, с целью повышения достоверности контроля динамических характеристик системы синхронизации, в него введены второй элемент И, третий мультиплексор, соединенный первым информационным входом с прямым выходом третьего триггера, управляющим входом - с входной шиной режима измерений, а выходом - со стартовым входом второго преобразователя время-код, стоповый вход которого подключен к выходу второго мультиплексора, блок выделения информационного интервала, три входа которого подсоединены соответственно к входной шине информации, к выходу первого триггера и к выходу элемента ИЛИ, а три выхода - соответственно к второму входу второго мультиплексора, к третьему информационному входу статистического анализатора временных интервалов и к второму информационному входу третьего мультиплексора, при этом выход первого триггера подключен к входу начального сброса преобразователей время-код, вход занесения третьего триггера соединен с входной шиной синхронизации, информационный вход-с выходом первого триггера, инверсный выход - с первым входом второго мультиплексора, а прямой выход - с вторым входом элемента ИЛИ, первый вход которого подключен к выходу первого триггера, а выход - к прямому входу второго элемента И, соединенного другим входом с выходом счетчика, своим выходом - с входом сброса второго триггера, вход установки которого подключен к входной шине информации, а выход - к стоповому входу первого преобразователя время-код, стартовый вход которого соединен с прямым выходом третьего триггера, причем входная шина синхронизации подключена к входу занесения первого триггера.

вход вместе с третьим входом элемента И и третьим входом блока выделения информационного Интервала подсоединен к выходу первого триггера, причем выход третьего триггера подключен к второму выходу блока выделения информационного интервала.

Ј// ,/ i.V

я/, г

| Авторское свидетельство СССР № 17344931, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-01-23—Публикация

1989-11-04—Подача