(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| Резервированный генератор синхроимпульсов | 1984 |

|

SU1175037A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для управления загрузкой бункеров | 1987 |

|

SU1533963A1 |

| СЧЕТЧИК С СОХРАНЕНИЕМ КОЛИЧЕСТВА ЕДИНИЦ | 2020 |

|

RU2761135C1 |

| Устройство для контроля блоков синхронизации | 1983 |

|

SU1134940A1 |

| Устройство для синхронизации памяти | 1984 |

|

SU1247853A1 |

Использование: область импульсной техники, в быстродействующих системах цифровой обработки сигналов и исполнительных устройствах цифровых следящих систем. Сущность изобретения: устройство содержит: 1 IK-триггер (1), 1 счетчик (2), 2 дополнительных IK-триггера (З, 4), 1 схему блокировки (5), 3 элемента И (6, 9, 10), 2 коммутатора (7, 11), 1 дешифратор (8), 2 п- разрядных регистра начальной фазы (12, 13). 1 элемент НЕ (14). 5 ил.

XJ

Ю СО Сл)

§

Устройство относится к области импульсной техники и может быть использовано, в частности, в быстродействующих системах цифровой обработки сигналов и исполнительных устройствах цифровых следящих систем.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения рабртоспособности при произвольном и переменном коэффициентах деления.

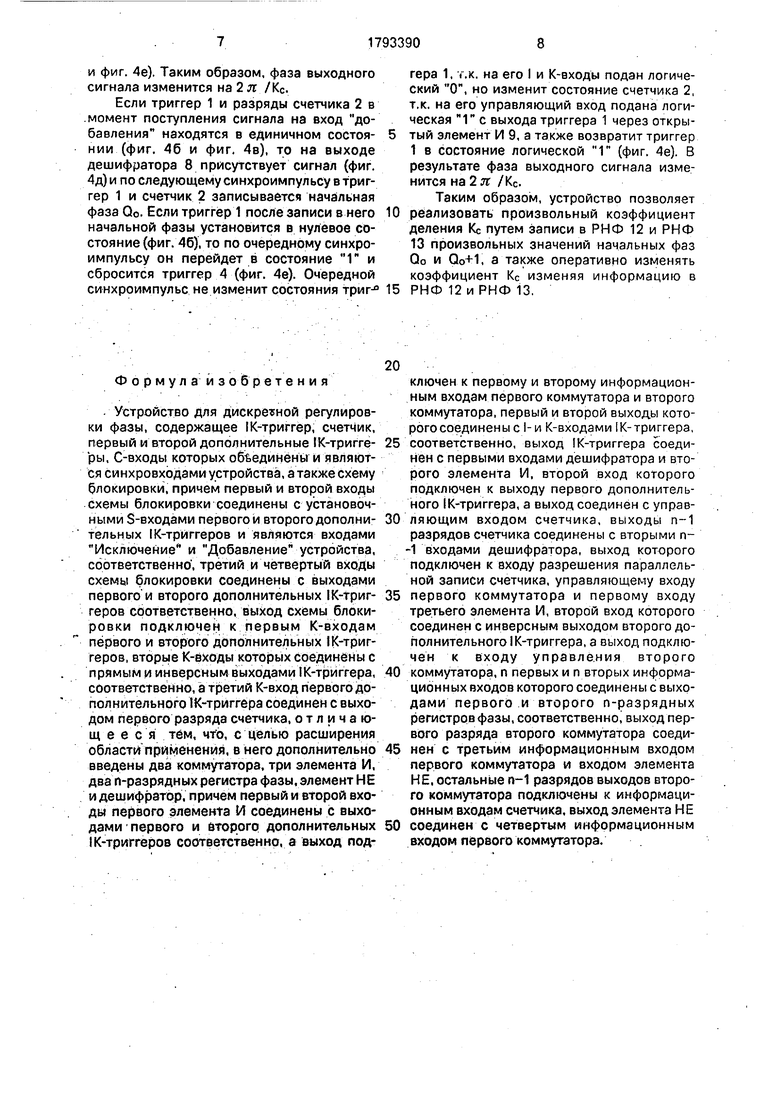

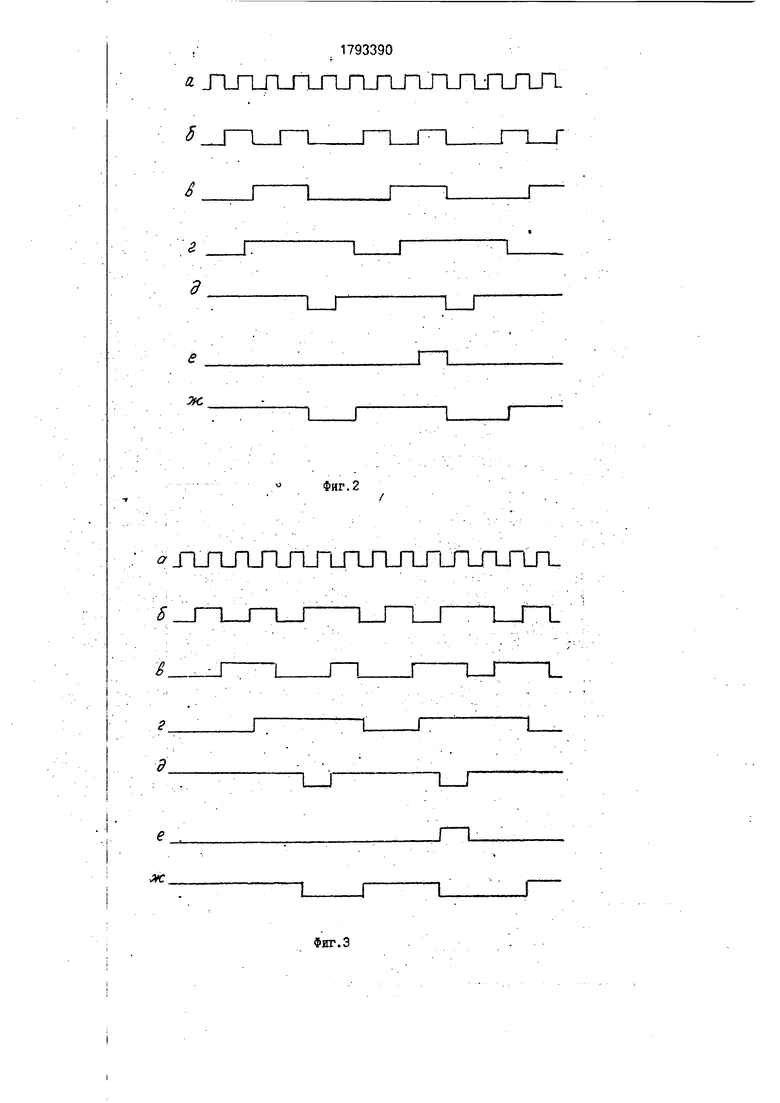

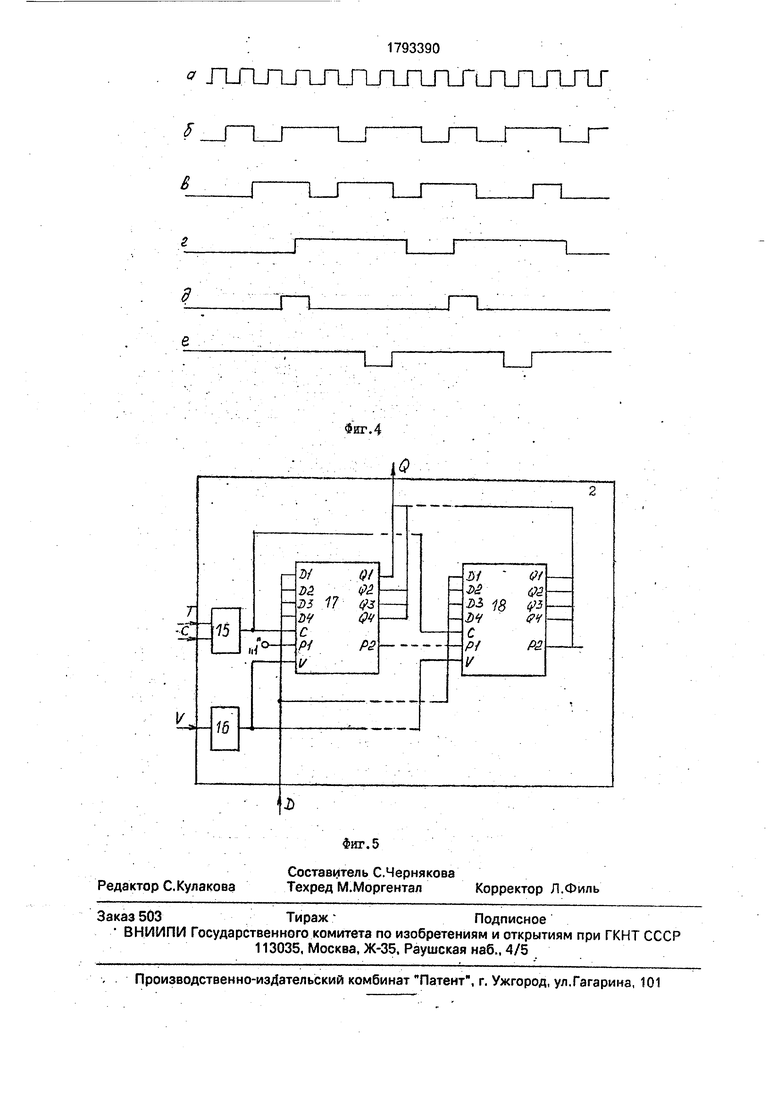

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу предлагаемого устройства при поступлении управляющего сигнала на вход исключение ; на фиг. 3 - временные диаграммы, поясняющие работу предлагаемого устройства при поступлении управляющего сигнала на вход добавление ; на фиг. 4 - временные диаграммы, поясняющие работу предлагаемого устройства при поступлении управляющего сигнала на вход добавления при нахождении IK-триггера и разрядов счетчика в единичном состоянии; на фиг. 5 - структурная схема счетчика.

Устройство для дискретной регулиров ки фазы (фиг. 1) содержит: IK-триггер 1, счетчик 2, первый и второй дополнительные IK-триггеры З и 4, схему блокировки (СБ) 5, элемент И 6, коммутатор 7, дешифратор 8. элементы И 9 и 10, коммутатор 11, первый и второй о-разрядныё регистры начальной фазы 12 и 13, элемент НЕ 14.

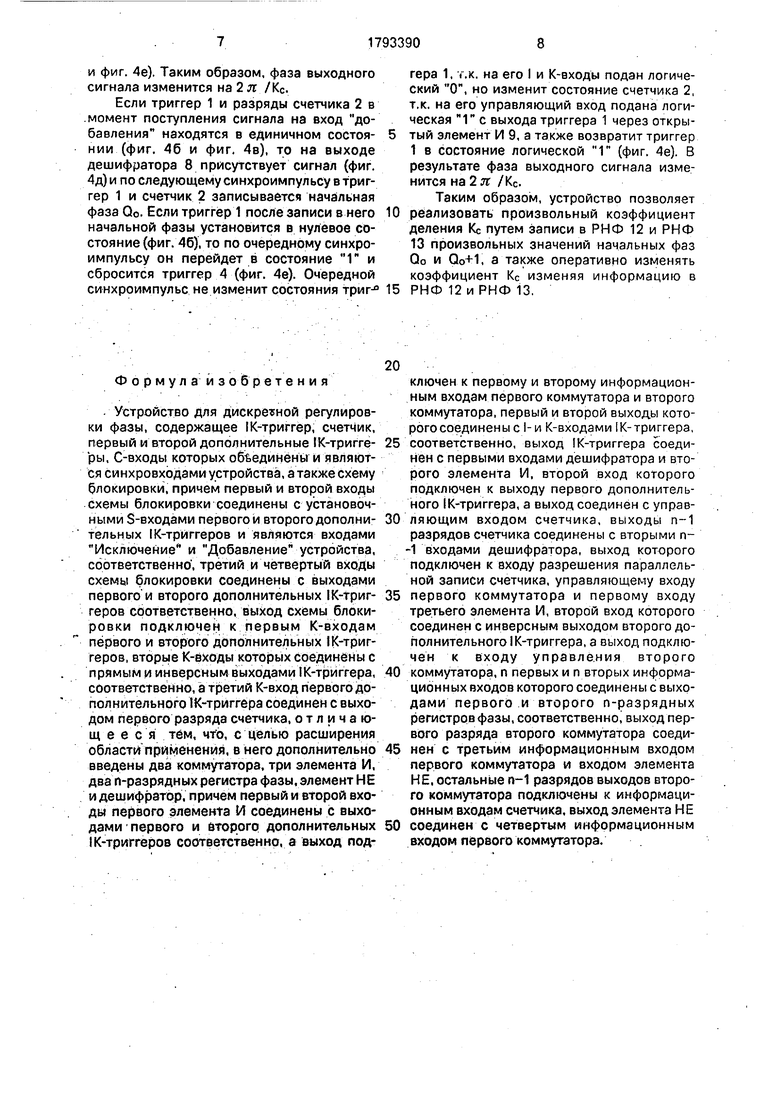

Счетчик (фиг. 5) содержит: элемент И 15, элемент НЕ 16, двоичные синхронные счетчики 17 и 18.

.Устройство работает следующим образом. ... ...

Произвольный коэффициент деления устройства обеспечивается известным способом путем записи в триггер 1 и счетчик 2 определенного состояния триггера 1. и всех разрядов счётчика 2. При этом запись начального состояния осуществляется при следующих условиях. Обозначим через Q(T) состояние разрядов триггера 1 и счетчика 2 на такте Т, через QK - состояние переполнения триггера 1 и счетчика 2. Тогда отсутствие управляющих импульсов добавления и исключения

Q(T+1) Q(T)+1,Q0 0(Т)Ок(1)

Q(T+1) Q0. Q(T) QK- При поступлении импульса исключения

Q(T+1) Q(T). VQ(T),. (2)н а при поступлен1 и импульса добавления

Q(T+1) Q(T)2,Q(T)QK-1

Q(T+1) Qo, Q(T) QK - 1(3) Q(T+1) Qo+1,Q(T) QK

Из третьего управления системы (З) следует, что в том случае, когда при поступлении импульса добавления триггер 1 и счетчик 2 находятся в состоянии переполнения QK,

следует производить запись начального состояния Q0+1, а не Qo.

На синхровходы триггера 1 и счетчика 2 поступают синхроимпульсы. При логических уровнях О на управляющих S-входах

триггеров 3 и 4 на их выходах присутствуют сигналы логической 1, вследствие чего на выходе элемента И 6 также присутствует единичный сигнал. В этом случае, если значения разрядов счетчика 2 и триггера 1 не

5 находятся в единичном состоянии, то сигнал на выходе дешифратора 8 отсутствует. При этом коммутатор 7 открыт для прохождения сигнала логической 1 с выхода элемента И 6 через первый и второй входы на У и К-вхо0 ды триггера 1. Элемент И 9 открыт для прохождения сигнала с выхода триггера 1 на управляющий вход счетчика 2, т.к. на его

второй вход поступает сигнал логической 1 с выхода триггера 3. Логические единиВ цы, присутствующие на I и К-входах триггера 1/ разрешают его переключение, а устройство работает как обычный двоичный счетчик. Когда значения всех разрядов счетчика 2 и триггера 1 примут значения 1, на

0 выходе дешифратора 8 появится сигнал логической 1. При этом счетчик 2 перейдете режим параллельной записи информации, а коммутатор 7 откроется для записи в триггер 1 информации о значении первого раз5 ряда начальной фазы устройства с выхода коммутатора 11. На выходе элемента И 10 присутствует сигнал логического О, т.к. триггер 4 находится, в единичном состоянии. Поэтому коммутатор 11 открыт для прохож0 дения информации с выхода РНФ 12, соответствующей начальной фазе устройства Qo. По очередному синхроимпульсу в триггер 1 и счетчик 2 перепишется значение начальной фазы устройства Q0, и сигнал на

5 выходе дешифратора 8 примет значение логического О. Таким образом, при отсутствии управляющих сигналов исключения и добавления устройство работает как счетчик с произвольным коэффициентом деле0 ния Кс, определяемым значением начальной фазы Q0 в РНФ 12. При подаче логического уровня 1 на вход исключения (фиг. 2г) триггер 3 начинает управляться по своим синхронным входам I, К и со

5 схемы 5 блокировки (СБ) 5 на первый К-вход триггера 3 поступает сигнал логической 1 (фиг.2ж). На 1-входе триггера 3 постоянно присутствует сигнал логической 1. Триггер 1 и первый разряд счетчика 2 периодически изменяют свои состояния (фиг.2б и фиг.2в)

и, когда сигналы на выходах принимают значения 1,триггерЗ переводится в состояние О (фиг.2д). Одновременно триггер 1 переходит в состояние 0(фиг.2б), и закрываются элементы И 6 и И 9. Очередной син- хроимпульс (фиг.2а) не изменит состояния триггера 1, т.к. на его I и К-входы подан логический О с выхода элемента И 6 через коммутатор 7, но не изменит состояния летчика 2, т.к. на его управляющий вход подан логический О с выхода элемента И 9, однако изменит состояние триггера 3, вс звращая его в 1 независимо от значения с& гнала с выхода СБ 5 (фиг, 2д). Появление логического О на выходе триггера 3 переводит СБ 5 в состояние логического О (фиг.2ж) и ее выходной сигнал, подаваемый н К-вход триггера 3, препятствует повторному переключению последнего в О. Воз- Bf ат СБ в 1 осуществляется окончанием в одного сигнала исключения (фиг. 2ж).

В том случае, если первое значение логической 1 на выходе триггера 1 после поступления сигнала исключения (фиг.2г) соответствует значению переполнения счетчика 2, то на выходе дешифратора 8 пс явится значение логической 1 (фиг. 2з) и ю очередному синхроимпульсу (фиг. 2а) в триггер 1 и счетчик 2 записывается значение начальной фазы Q0 из РНФ 12 через коммутатор 11, а триггер 3 сбрасывается в О, закрывая элементы И 6 и И 9.

По очередному синхроимпульсу триггер 1 не изменит своего состояния, т.к. на его I и К-входы подан логический О с выхода элемента И 6 через коммутатор 7, но не изменит состояния счетчика 2, т.к. на его управляющий вход подан логический О с вь хода элемента И 9, но изменит состояние триггера 3, который устанавливается 6 со- стэяние логической 1 (фиг. 2д). При этом отфывэются элементы И 6 и 1/1 9, и триггер 7 и счетчик 2 работают в счетном режиме.

Таким образом, в результате подачи ло- ги еского уровня 1 на вход исключения фг за выходного сигнала устройства изменяет :я (замедляется) на 2 п /Кс, где Кс - коэф- фу циент деления устройства.

При подаче логического уровня 1 на вход добавления (фиг. Зг) триггер 4 начи- наетуправляться посвоим синхронным входам I, К и С. С выхода СБ 5 на первый К-вход

тр

иггера 4 поступает сигнал логической 1н.

Тр иггер 1 периодически изменяет свое состояние и когда сигнал на его прямом выхо- де: принимает значение логического О, триггер 4 следующим синхроимпульсом (фиг. За) приводится в состояние О (фиг. Зд|. При этом закрывается элемент И 6, а триггер 1 переводится в состояние 1 (фиг.

0

0

5

0

5

0

5

0

5

5

36). Очередной синхроимпульс не изменит состояния триггера 1, т.к. на его I и К-входы подан логический О с выхода элемента И б через коммутатор 7, однако изменит состояние счетчика 2, т.к. на его управляющий вход подан сигнал логической 1 с выхода триггера 1 через открытый элемент И 9 (фиг. Зв), а также возвратит в состояние 1 триггер 4 независимо от значения сигнала с выхода СБ 5 (фиг.Зд). Появление логического О на выходе триггера 4 переводит СБ 5 в состояние логического О и ее выходной сигнал, поступающий на К-вход триггера 4, препятствует переключению последнего в О. Возврат СБ 5 в 1 осуществляется окончанием входного сигнала добавления (фиг.Зж).

В том случае, если триггер 1 в момент поступления сигнала на вход добавления (фиг.З) находится в состоянии логического О (фиг.Зб), а все разряды счетчика 2 находятся .в единичном состоянии, то по очередному синхроимпульсу триггер 4 перейдет в состояние О., а триггер 1 - в состояние 1. При этом откроется элемент И 10 (фиг Зе), т.к. на инверсном выходе триггера 4 и выходе дешифратора 8 появятся логические 1. Поэтому коммутатор 11 откроется для. прохождения информации, содержащейся в РНФ 13 и соответствующей состоянию триггера 1 и счетчика 2 Qo + 1 (состояние младших разрядов 01 на фиг.Зв и фиг.Зб соответственно). По очередному синхроимпульсу в триггер 1 и счетчик 2 запишется начальная фаза из РНФ 13, установится в 1 триггер 4, Запись в счетчик начального состояния Qo+1 соответствует изменению фазы выходного сигнала на 2 л: /Кс

Если триггер 1 и разряды счетчика 2 в момент поступления сигнала на вход добавления находятся в единичном состоянии (фиг. 46 и фиг.4в). то на выходе дешифратора 8 присутствует сигнал (фиг. 4д) и по следующему синхроимпульсу в триггер 1 и счетчик 2 записывается начальная фаза Qo из РНФ 12. Если триггер 1 после записи в него начальной фазы остается в состоянии 1, то по очередному синхроим- пул ьсу он перейдет в состояние О (фиг. 46). Следующий синхроимпульс переведет триггер 1 в состояние 1, а триггер 4 - в состояние О (фиг. 4е). По очередному синхроимпульсу триггер 1 не изменит своего состояния, т.к. на его t и К-входы подан логический О, однако изменит состояние счетчика 2, т.к. на его управляющем входе присутствует 1 с выхода триггера 1 через открытый элемент И 9, а также возвратит триггер 4 в состояние логической 1(фиг. 4в

и фиг. 4е). Таким образом, фаза выходного сигнала изменится на 2 я /Кс.

Если триггер 1 и разряды счетчика 2 в .момент поступления сигнала на вход добавления находятся в единичном состоя- нии (фиг. 46 и фиг. 4в), то на выходе дешифратора 8 присутствует сигнал (фиг. 4д)и по следующему синхроимпульсу в триггер 1 и счетчик 2 записывается начальная фаза Qo. Если триггер 1 после записи в него начальной фазы установится в нулевое состояние (фиг. 46), то по очередному синхроимпульсу он перейдет в состояние Г и сбросится триггер 4 (фиг. 4е). Очередной синхроимпульс не изменит состояния триг-°

Формула изобретения

- Устройство для дискретной регулировки фазы, содержащее IK-триггёр, счетчик, первый и второй дополнительные ГК-тригге- ры, С-входы которых объединены и являются синхровходами устройства, а также схему блокировки, причем первый и второй входы схемы блокировки соединены с установочными S-входами первого и второго дополнительных 1К-триггеров и являются входами Исключение и Добавление устройства, соответственно , третий и четвертый входы схемы блокировки соединены с выходами первого и второго дополнительных IK-триггеров соответственно, выход схемы блокировки подключен к первым К-входам первого и второго дополнительных 1К-триг- геров, вторые К-входы которых соединены с прямым и инверсным выходами К-трйггера, соответственно, а третий К-вход первого дополнительного Ж-трйггера соединен с выходом первого разряда счетчика, отличаю- щ е ее я тем, что, с целью расширения области применения, в него дополнительно введены два коммутатора, три элемента И, два n-разрядных регистра фазы, элемент НЕ и дешифратор, причем первый и второй входы первого элемента И соединены с выходами первого и второго дополнительных IK-триггеров соответственно, а выход подгера 1, т.к. на его I и К-входы подан логический О, но изменит состояние счетчика 2, т.к. на его управляющий вход подана логическая 1 с выхода триггера 1 через открытый элемент И 9, а также возвратит триггер 1 в состояние логической Г (фиг. 4е). В результате фаза выходного сигнала изменится на 2л /Кс.

Таким образом, устройство позволяет реализовать произвольный коэффициент деления Кс путем записи в РНФ 12 и РНФ 13 произвольных значений начальных фаз Qo и Qo+1, а также оперативно изменять коэффициент Кс изменяя информацию в РНФ 12 и РНФ 13.

ключей к первому и второму информационным входам первого коммутатора и второго коммутатора, первый и второй выходы кото- рогосоединеныс 1-й К-входами IK-триггера,

соответственно, выход IK-триггера соединен с первыми входами дешифратора и второго элемента И, второй вход которого подключен к выходу первого дополнительного iK-триггера, а выход соединен с управляющим входом счетчика, выходы п-1 разрядов счетчика соединены с вторыми п- -1 входами дешифратора, выход которого подключен к входу разрешения параллельной записи счетчика, управляющему входу

первого коммутатора и первому входу третьего элемента И, второй вход которого соединен с инверсным выходом второго дополнительного IK-триггера, а выход подключен к входу управления второго

коммутатора, п первых и п вторых информационных входов которого соединены с выходами первого и второго п-разрядных регистров фазы, соответственно, выход первого разряда второго коммутатора соединен с третьим информационным входом первого коммутатора и входом элемента НЕ. остальные гт-1 разрядов выходов второго коммутатора подключены к информационным входам счетчика, выход элемента НЕ

соединен с четвертым информационным входом первого коммутатора.

о- Jijnjijaj jijaj rLrijn riJ L

J L

г.

д

0Фиг.2

; jiTLTLnjTJTjTJijn

э

LJ

ж.

1Г

Jt

1-ГТ

1793390

JlJnJTJTJTJlJ-LriJ

| Устройство для дискретной регулировки фазы | 1979 |

|

SU871098A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| (И) УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ РЕГУЛИРОВКИ ФАЗЫ | |||

Авторы

Даты

1993-02-07—Публикация

1990-06-25—Подача