Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении унифицированных блоков синхронизации дискретных устройств.

Цель изобретения - повьшение быстродействия.

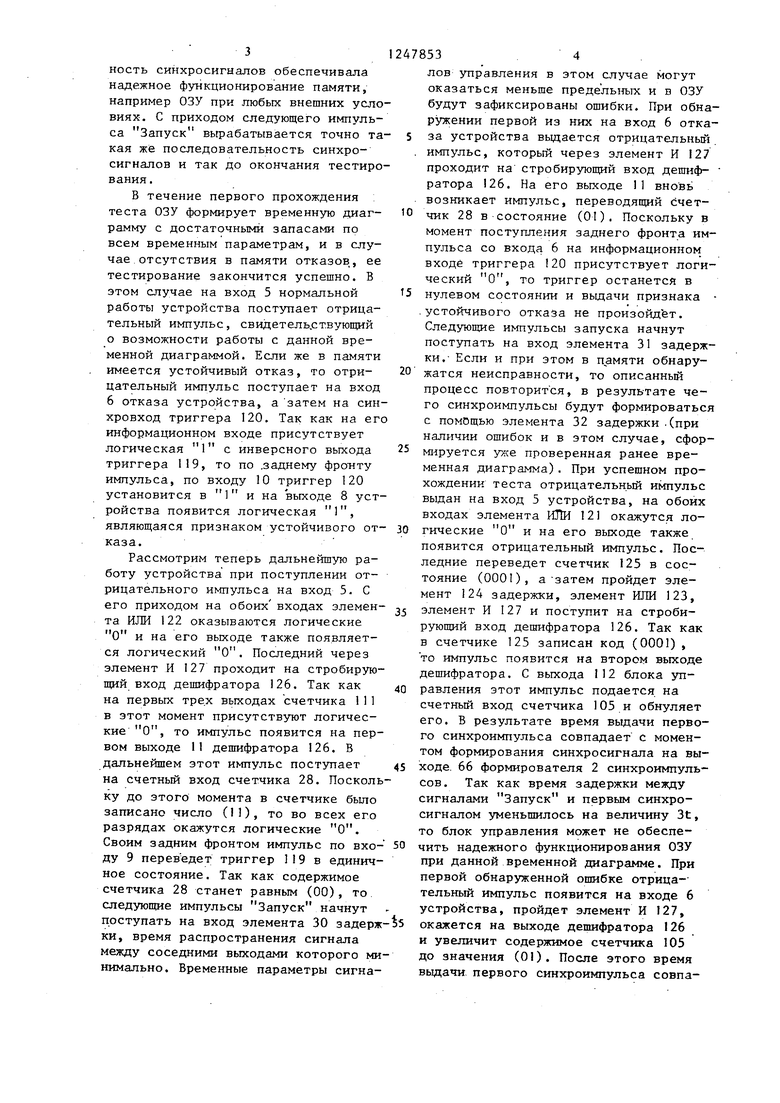

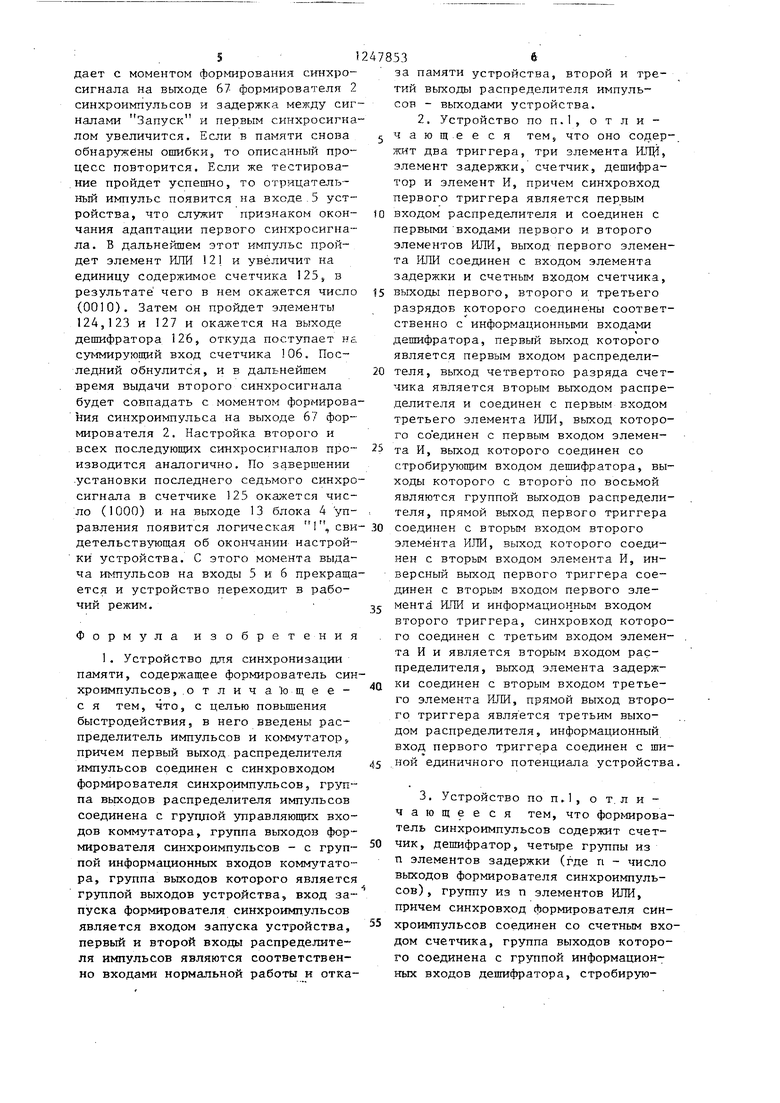

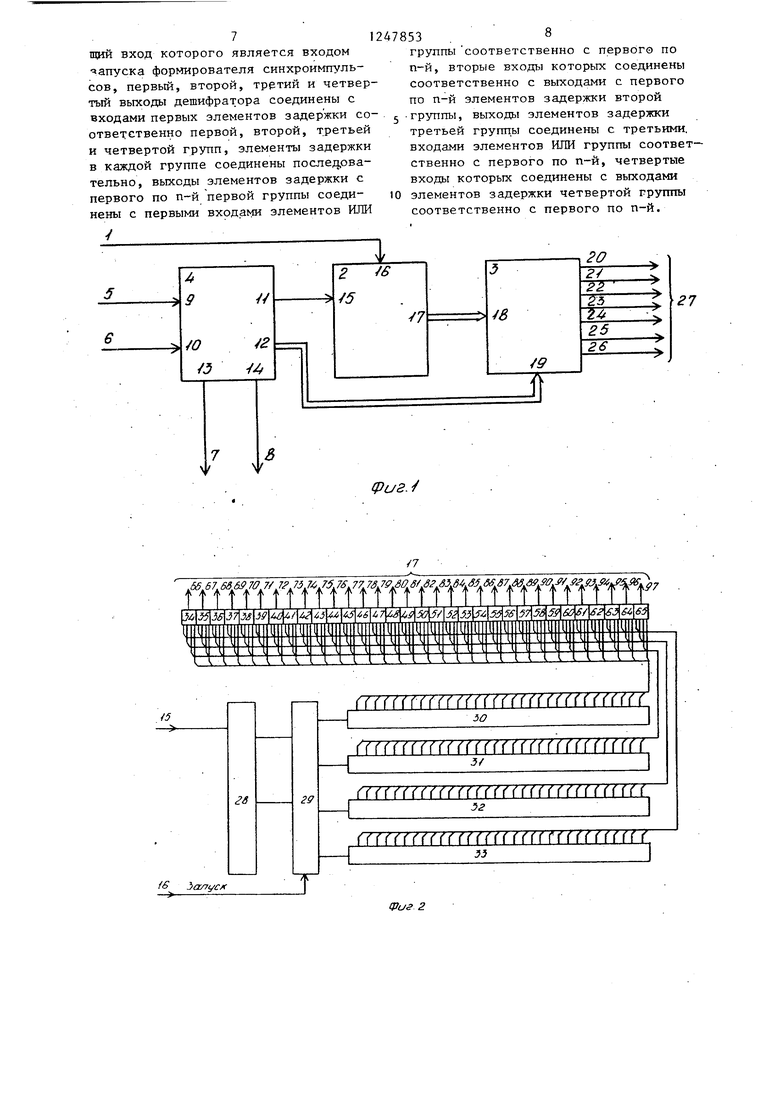

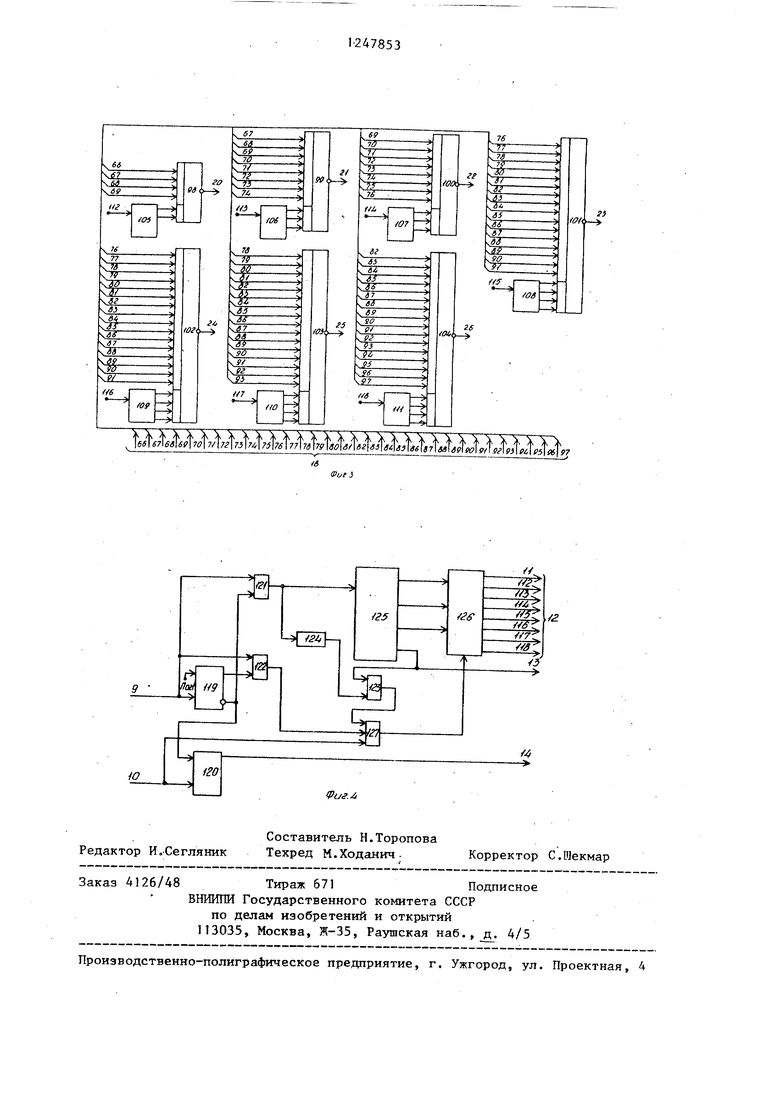

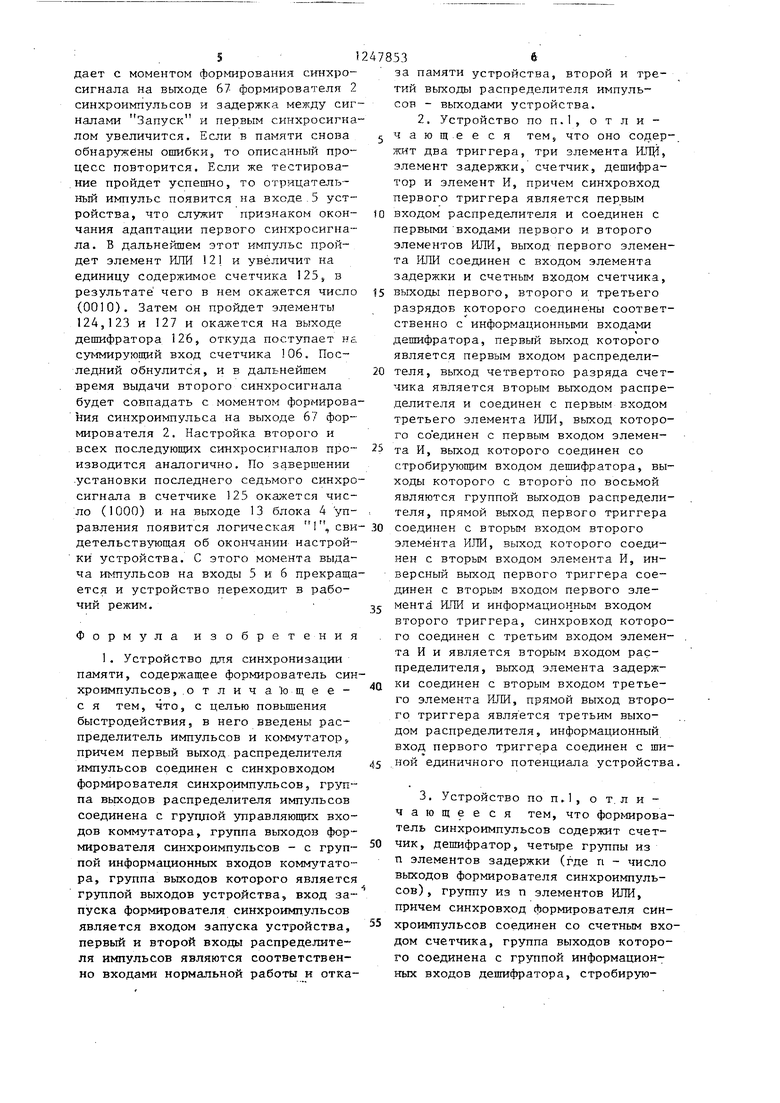

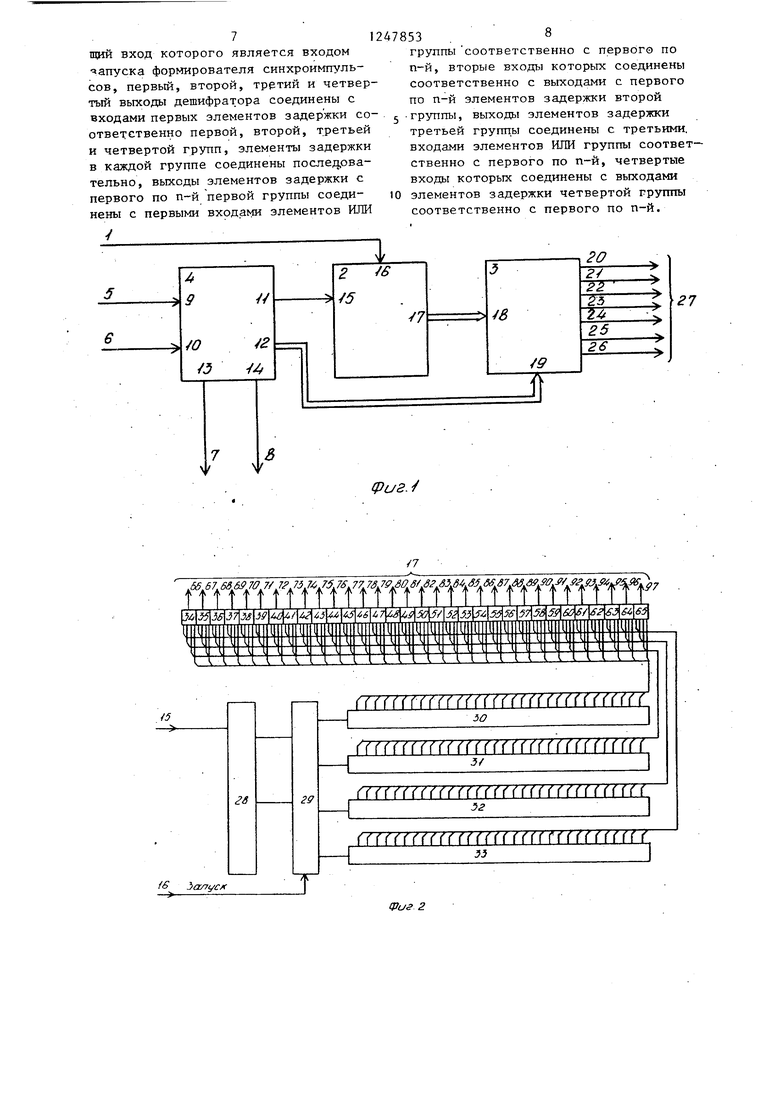

На фиг.1. представлена схема устройства; на фиг.2 - схема формирователя синхроимпульсов; на фиг.3 - схема коммутатора; на фиг.А - схема блока управления.

Устройство содержит вход 1 запуска, формирователь .2 синхросигналов, коммутатор 3, блок 4 управления, вход 5 блокировки адаптации, вход 6 разрешения продолжения адаптации, выход 7 оконча ния настройки устройства, выход 8 сигнала отказа, входы 9 и 10 .распределителя, первый выход П блока управления, группа 12 выходов бло- управления, второй и третий выходы 13 и 14 блока управления, синхро- вход 15 формирователя 2 синхроимпульсов, вход 16 запуска формировате- 25 яснена на примере его использования

ля 2 синхроимпульсов,.группа 17 вьпсо- для управления памятью.

дов формирователя 2 синхроимпульсов, При выдаче устройством той или

группа 18 информационных входов коммутатора 3, группа 19 управляющих .входов коммутатора, выходы 20 - 26 коммутатора, группы 27 выходов устройства. Формирователь 2 синхроимпульсов содержит счетчик 28, дешифртор 29, группы 30 - 33 элементов задержки, элементы ИЛИ 34-65 групп, в ходы 66-97. Коммутатор 3 содержит мультиплексоры 98 - 104, счетчики 105 - 1П, управляющие входы 112 - 118. Блок управления содержит триггеры 119 и 120, элементы ИЛИ 121 - 123, элемент 124 задержки, счетчик 125, дешифратор 126, элемент И 127.

Устройство работает следующим образом.

Вначале производится настройка устройства, перед началом которой триггеры 119 и 120 и счетчик 125 блока 4 управления устанавливаются

В О, а во все разряды счетчика 28 формирователя 2 синхроимпульсов и счетчиков 105-11 коммутатора 3 записываются 1 (цепи начальной установки не показаны).

I

В исходно м состоянии на входе 1 запуска устройства сигнал отсутству- .ВТ, отсутствует сигнал на входе 16 формирователя 2 синхроимпульсов, что с ответствует логическому О на

стробирующем входе депгафратора 29,

на выходе которого сохраняются логические .О и ни один из элементов

30-33 задержки не запускается. Следовательно, на всех входах элементов ИЛИ 34-65 и на выходах формирователя 2 синхроимпульсов оказываются i логические 0.

Так как на выходах счетчиков 105- 11 1 коммутатора 3 присутствуют логические 1 , то на выходы 20-26 -мультиплексоров 98-104 поступают инверсные значения данных, находящихся на их . последних информационных входах, т .е. на входах 69,74,76,9.1,92,93, и 97 соответственно. Поскольку в исходном состоянии до поступления сигнала запуска на этих входах, также как и на других информационных входах муль- типлексоров присутствуют логические О, то на выходах 20-26 коммутатора 3 сказываются логические 1, означающие отсутствие синхросигналов. Датгее работа устройства будет по

5

иной последовательности синхросигналов проводится тестирование памяти, 30 с началом котор.ого -на вход начинают поступать импульсы Запуск. Они проходят на стробирующий вход дешифратора 29 и так как оба разряда счетчика 28 находятся в единичном

ТТ 1 1

СОСТОЯНИИ, то логич.еская

появит 5

ся на последнем четвертом выходе де- щифратора и поступит на вход элемента 33 задержки четвертой группы. Элементы 30-33 задержки имеют 32 выхода 40 причем tjg t, t. тяе t - время распространения сигнала между соседними выходами i-ro элемента. Следовательно, на выходах 66-97 элементов ИЛИ 34-65 сформируется наиболее растянутая во времени последовательность синхроимпульсов.

45

50

Так как перед началом тестирования в счетчиках 105-111 коммутатора 3 записаны 1, то исходная, последовательность синхросигналов на выходах 20-26 мультиплексоров совпадает с последовательностью синхроимпульсов на их последних информационных входах. Соединения между последними S5 информационными .входами мультиплексоров 98-104 и выходами элементов ИЛИ 34-65 вьтолняются таким образом, чтобы сформированная последователь3

ность синхросигналов обеспечивала надежное функционирование памяти, например ОЗУ при любых внешних условиях. С приходом следующего импульса Запуск вьфабатывается точно такая же последовательность синхросигналов и так до окончания тестирования.

В течение первого прохождения теста ОЗУ формирует временную диаграмму с достаточными запасами по всем временным параметрам, и в случае отсутствия в памяти отказов,, ее тестирование закончится успешно. В этом случае на вход 5 нормальной работы устройства поступает отрицательный импульс, свидетель,ст.вующий о возможности работы с данной временной диаграммой. Если же в памяти имеется устойчивый отказ, то отрицательный импульс поступает на вход 6 отказа устройства, а затем на син- хровход триггера 120. Так как на его информационном входе присутствует логическая 1 с инверсного выхода триггера 119, то по .заднему фро нту импульса, по входу 10 триггер 120 установится в 1 и на выходе 8 устройства появится логическая 1, являющаяся признаком устойчивого отказа.

Рассмотрим теперь дальнейшую работу устройства при поступлении отрицательного импульса на вход 5. С его приходом на обоих входах элемента ИЛИ 122 оказываются логические О и на его выходе также появляется логический О. Последний через элемент И 127 проходит на стробирую- щий вход дешифратора 126. Так как на первых трех выходах счетчика 111 в этот момент присутствуют логические О, то импульс появится на первом выходе 11 дешифратора 126. В дальнейшем этот импульс поступает на счетный вход счетчика 28. Поскольку до этого момента в счетчике было записано число (И), тс во всех его разрядах окажутся логические О. Своим задним фронтом импульс по входу 9 переведет триггер 119 в единичное состояние. Так как содержимое счетчика 28 станет равным (00), то следующие импульсы Запуск начнут поступать на вход элемента 30 задержки, время распространения сигнала между соседними выходами которого минимально. Временные параметры сигна478534

лов управления в этом случае могут оказаться меньше предельных и в ОЗУ будут зафиксированы ошибки. При обнаружении первой из них на вход 6 отка- 5 за устройства вьщается отрицательньй . импульс, который через элемент И 127 проходит на стробируюш гй вход дешиф- ратора 126. На его выходе И вновь возникает импульс, переводящий счет 0 чик 28 в состояние (01), Поскольку в момент поступления заднего фронта импульса со входа 6 на информационном входе триггера 120 присутствует логический О, то триггер останется в

5 нулевом состоянии и выдачи признака - .устойчивого отказа не произойдет. Следующие импульсы запуска начнут поступать на вход элемента 31 задержки.- Если и при этом в памяти обнару20 жатся неисправности, то описанный процесс повторит ся, в результате чего синхроимпульсы будут формироваться с помощью элемента 32 задержки . (при наличии ошибок и в этом случае, сфор25 мируется проверенная ранее временная диаграмма). При успешном прохождении теста отрицательный импульс выдан на вход 5 устройства, на обоих входах элемента ИПИ 121 окажутся ло30 гические О и на его выходе также появится отрицательный импульс. Последние переведет счетчик 125 в состояние (0001), а-затем пройдет элемент 124 задержки, элемент ИЛИ 123,

5 элемент И 127 и поступит на строби- рующий вход дешифратора 126. Так как в счетчике 125 записан код (0001), то импульс появится на втором выходе дешифратора. С выхода 112 блока уп0 равления этот импульс подается на счетный вход счетчика 105 и обнуляет его. В результате время выдачи первого синхроимпульса совпадает с моментом формирования синхросигнала на вы5 ходе. 66 формирователя 2 синхроимпульсов. Так как время задержки между сигналами Запуск и первым синхросигналом уменьшилось на величину 3t, то блок управления может не обеспе0 чить надежного функционирования ОЗУ при данной временной диаграмме. При первой обнаруженной ошибке отрица- тельный импульс появится на входе 6 устройства, пройдет элемент И 127, 5 окажется на выходе дешифратора 126 и увеличит содержимое счетчика 105 до значения (01). После этого время выдачи первого синхроимпульса совпа- .5

дает с моментом формирования синхросигнала на выходе 67 формирователя 2 синхроимпульсов и задержка между сигналами Запуск и первым синхросигналом увеличится. Если в памяти снова обнаружены ошибки то описанный процесс повторится. Если же тестирова.кие пройдет успешно, то отрицатепь- ный импульс появится на входе.5 устройства, что служит признаком окончания адаптации первого синхросигнала. В дальнейшем этот импульс пройдет элемент ИЛИ 121 и увеличит на единицу содержимое счетчика 125, в результате чего в нем окажется число (0010). Затем он пройдет элементы 124,123 и 127 и окажется на выходе дешифратора 126, откуда поступает нь суммирующий вход счетчика 106. Последний обнулится, и в дальнейшем время выдачи второго синхросигнала будет совпадать с моментом формирования синхроимпульса на выходе 67 формирователя 2. Настройка второго и всех последуюшзях синхросигн.алов производится аналогично. По завершении .установки последнего седьмого синхросигнала в счетчике 125 окажется число (1000) и на выходе 13 блока 4 управления появится логическая I, свидетельствующая об окончании настрой кй устройства. С этого момента выдача иютульсов на входы 5 и 6 прекращается и устройство переходит в рабочий режим.

Формула изобретения

1 . Устройство для синхронизации памяти, содержащее формирователь синхроимпульсов, .отлича с я тем, что, с целью повышения быстродействия, в него введены распределитель импульсов и коммутатор причем первый выход.распределителя импульсов соединен с синхровходом формирователя синхроимпульсов, группа выходов распределителя импульсов соединена с грудпой управляюшзих входов коммутатора, группа выходов формирователя синхроимпульсов - с группой информационных входов коммутатора, группа выходов которого является группой выходов устройства, вход запуска формирователя синхроимпульсов является входом запуска устройства, первый и второй входы распределителя импульсов являются соответственно входами нормальной работы и отка2478536

за памяти устройства, второй и третий выходы распределителя импульсов - выходами устройства.

2. Устройство по п.

о т л и чающ.ееся тем, что оно содержит два триггера, три элемента ИОД, элемент задержки, счетчик, дешифратор и элемент И, причем синхровход первого триггера является первым

входом распределителя и соединен с первыми входами первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен с входом элемента задержки и счетным входом счетчика,

выходы первого, второго и третьего разрядов которого соединены соответственно с информационными входами дешифратора, первый выход которого является первым входом распределителя, выход четвертого разряда счетчика является вторым выходом распределителя и соединен с первым входом третьего элемента ИЛИ, выход которого со единен с первым входом элемента И, выход которого соединен со

стробируюш {м входом дешифратора, выходы которого с второго по восьмой являются группой выходов распределителя, прямой выход первого триггера

соединен с вторым входом второго элемента ИЛИ, выход которого соеди- .нен с вторым входом элемента И, инверсный выход первого триггера соединен с вторым входом первого элемента ИЛИ и информационным входом

второго триггера, синхровход которо- го соединен с третьим входом элемента И и является вторым входом распределителя, выход элемента задержки соединен с вторым входом третьего элемента РШИ, прямой выход второго триггера явля ется третьим выходом распределителя, информационный вход первого триггера соединен с ши.ной единичного потенциала устройства.

3. Устройство по П.1, о т. л и - чающееся тем, что формирователь синхроимпульсов содержит счетчик, дешифратор, четьфе группы из п элементов задержки (г де п - число выходов формирователя синхроимпульсов) , группу из п элементов ИЛИ, причем синхровход формирователя синхроимпульсов соединен со счетным входом счетчика, группа выходов которого соединена с группой информационных входов дешифратора, стробирующий вход которого является входом запуска формирователя синхроимпульсов, первый, второй, третий и четвертый выходы дешифратора соединены с входами первых элементов задержки соответственно первой, второй, третьей и четвертой групп, элементы задержки в каждой группе соединены послед5,ова- тельно, выходы элементов задержки с первого по п-й первой группы соединены с первыми входами элементов ИЛИ

66.6 7.666$7О 7/ 7. . 7S. 77.7А ef.S2..SS..S9Sff.//ff.ffJ.ff4,.fS,. 7 ТТТ ТтТ ФФТТТчТтгТ Т ТТ Т ТТ г рТТФ гт фт

1247853 .8

группы соответственно с первого по п-й, вторые входы которых соединены соответственно с выходами с первого по п-й элементов задержки второй 5 -группы, выходы элементов задержки третьей группы соединены с третьими, входами элементов ИЛИ группы соответственно с первого по п-й, четвертые входы которых соединены с выходами 10 элементов задержки четвертой группы соответственно с первого по п-й.

(Риг.-/

Фиг. Л

Редактор И.Сегляник

Составитель Н.Торопова Техред М.ХоданичЗаказ 4126/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| Устройство для контроля блоков синхронизации | 1983 |

|

SU1134940A1 |

| Микропрограммное устройство управления | 1981 |

|

SU959078A1 |

| Устройство для подготовки информации на перфоленте | 1977 |

|

SU684549A1 |

| Устройство для вывода информации | 1986 |

|

SU1322297A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2029352C1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении унифицированных блоков синхронизации дискретных устройств. Целью изобретения является повьшение быстродействия. Отличительной особенностью устройства является возможность формировать различные временные диаграммы с минимальным временем после запускающего сигнала. Поставленная цель достигается, введением блока управления и коммута- тора. 2 з.п. ф-лы, 4 ил. с ifi tc 4ib 00 СЛ СО

| Устройство для управления полупроводниковой памятью | 1977 |

|

SU746515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство синхронизации памяти | 1982 |

|

SU1101805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-30—Публикация

1984-06-06—Подача