(54) УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ РЕГУЛИРОВКИ ФАЗЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дискретной регулировки фазы | 1978 |

|

SU779904A1 |

| Устройство регулируемой задержки | 1984 |

|

SU1175020A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство для дискретной регулировки фазы | 1982 |

|

SU1027639A1 |

| Устройство для дискретной регулировки фазы | 1990 |

|

SU1793390A1 |

| Преобразователь телевизионного стандарта | 1981 |

|

SU1016850A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство для дискретной регулировки фазы | 1985 |

|

SU1269051A1 |

| Цифровой фазовращатель | 1984 |

|

SU1213434A1 |

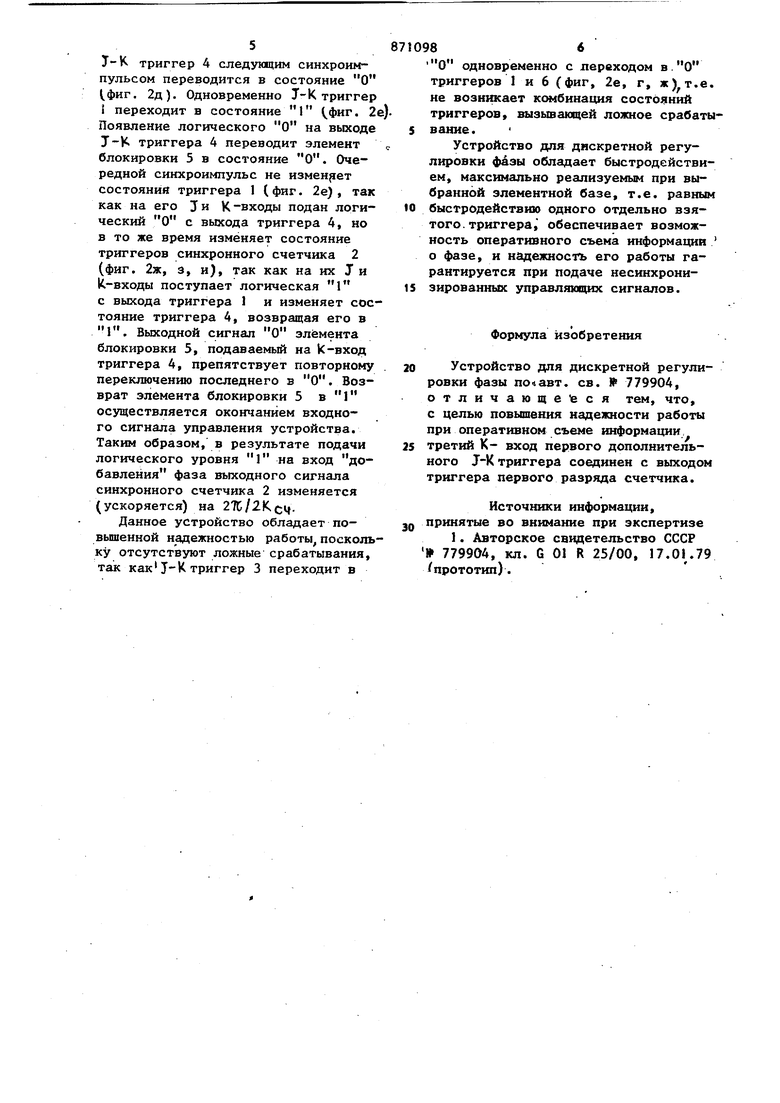

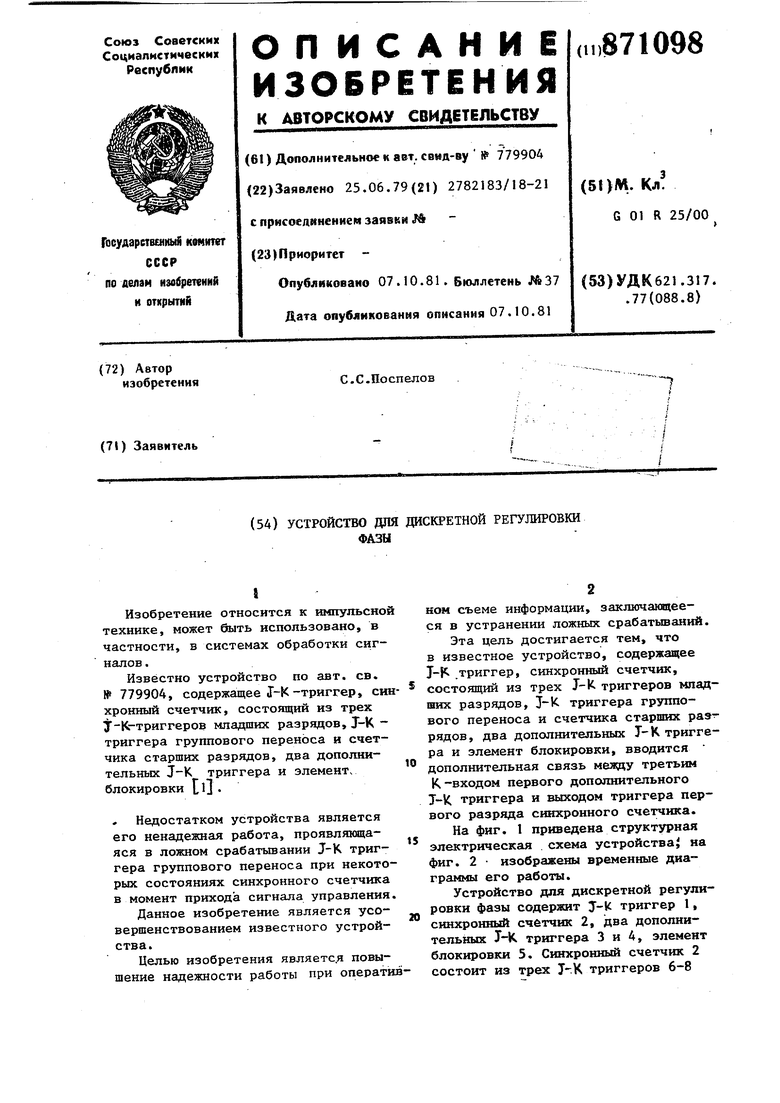

Изобретение относится к импульсно технике, может быть использовано, в частности, в системах обработки сигналов . Известно устройство по авт. св. № 779904, содержащее J-K-триггер, си кронный счетчик, состоящий из трех Т К-триггеров младших разрядов, J-K триггера группового переноса и счетчика старших разрядов, два дополнительных J-K триггера и элемент блокировки tl Недостатком устройства является его ненадежная работа, проявляняцаяся в ложном срабатывании J-K триггера группового переноса при некото рых состояниях синхронного счетчика в момент прихода сигнала управления Данное изобретение является усовершенствованием известного устройства. Целью изобретения являетс.я повышение надежности работы при операти НОМ съеме информации, заключанядееся в устранении ложных срабатываний. Эта цель достигается тем, что в известное устройство, содержащее .триггер, синхронный счетчик, состоящий из трех J-k. триггеров младших разрядов, J-K триггера группового переноса и счетчика старших раэ рядов, два дополнительных Т-К триггера и элемент блокировки, вводится дополнительная связь мезвду третьим К-входом первого дополнительного T-lC триггера и выходом триггера первого разряда синхронного счетчика. На фиг. 1 приведена структурная электрическая схема устройства на фиг. 2 изображены временные диаграммы его работы. Устройство для дискретной регулировки фазы содержит 7-k триггер 1, синхронный счётчик 2, два дополнительных J-K триггера 3 и 4, элемент блокировки 5. Синхронный счетчик 2 состоит из трех J-.K триггеров 6-8 младших разрядов, J-K триггера 9 группового переноса и счетчика 10 старших разрядов. Прямой выход J-K триггера 1 соединен с попарно объединенными J и К входами J-K триггеров 6-8 и вторым К-входом J-K триггера 3. Инверсный выход J-K триггера J соединен со вторым К-входом триггера 4. Прямые выходы Т-К триггеров 3 и 4 соединены с первым и вто рым входами элемента блокировки 5 и попарно объединенными Т и Квходами Т-К триггера 1. Первые К-вкрды J-K триггеров 3 и 4 соединены с выходом элемента блокировки 5. J-вхо ды J-K триггеров 3 и 4 соединены с источником логической единицы. 5 - вход триггера 3 соединен с третьим входом элемента блокировки 5 и является управляющг м входом ис ключения устройства. триг,гера 4 соединен с четвертым входом элемента блокировки 5 и является управляющим входом добавления уст ройства. Выход J-k триггера 6 соеди нен с попарно объединенными J и К входами J-K триггеров 7 и 8, первым J-входом J-K триггера 9 и третьим К-входом J-K триггера 3. Выход J- К триггера 7 соединен с объединенными J и К входами триггера 8 и вторым J-входом J-K триггера 9. Выход 7- К триггера 8 соединен с третьим J-вхо дом J-K триггера 9. Выход J-K триггера 9 соединен с его К-входами и входом управления счетчика 10, С-вх ды триггеров 1, 3, 4, 6-9 и счетчик 10 объединены и являются синхровходом устройства. Устройство работает следующим об разой. На синхровходы J-K триггеров 1, 3, 4, 6-9 и счетчика 10 поступают ci-шхроимпульсы (фиг. 2а). При логических уровнях О на управлякнцих входах устройства (фиг. 26, в) на в ходах триггеров 3 и 4 присутствуют логические 1, разрешаняцие переключение Т-К триггера 1, к устройст во работает как обычный синхронный счетчикС параллельным переносом с коэффициентом деления 2Кси где Kev коэффициент деления синхронного сче чика 2 (фиг. 2е, ж, 3, и). При пере ключении J-K триггеров 6-8 в состоя J-K триггер) 9 подготавлива ется к переключению. Очередной синх роимпульс переводит 3 -К, триггеры 1 и 9 в состояние J, а последую4щий --в состояние О (фиг. 2е, к). Такимобразом, J-k триггер 9 переходит всостояние 1 один раз за период работы группы триггеров 6-8 младших разрядов синхронного счетчика 2 на время действия одного синхроимпульса, разрешая последнему воздействовать на счётчик 10. При подаче логического уровня 1 на вход исключения устройства (фиг. Йб) J-K триггер 3 начинает управляться по своим синхронным входам J, К и С . С выхода элемента блокировки 5 на К-вход J- К, триггера 3 поступает сиг.нал 1. На J-входе тригт-ера 3 постоянно присутствует сигнап 1. Триггеры 1 и 6 периодически изменяют свое состояние (фиг. 2е, ж) и, когда сигналы на их выходах принимают значение J-K триггер следукицим синхроимпульсом переводится в состояние О . 2г) . Одновременно триггер переходит в состояние О (фиг. 2е). Появление логического О на выходе J-JC триггера 3 переводит элемент блокировки 5 в состояние О. Очередной синхроимпульс не изменя-г ет состояния триггера 1 (фиг. 2е , так как на его J и К-входы подан логический О с выхода триггера 3, не изменяет состояния триггеров синхронного счетчика 2 (фиг. 2ж з, и), .так как на их Ти К -входы поступает логический О с выхода триггера , однако изменяет состояние триггера 3, возвращая его в 1 (фиг. 2г). Выходной сигнал О элемента блокировки 5, подаваемый на К-вход триггера 3s в дальнейшем пре- пятствует повторному переключению последнего. Возврат элемента блокировки 5 в 1 осуществляется окончанием входного сигнала управления устройства. Таким образом, в результате подачи логического уровня 1 на вход исключения фаза выходного . сигнала синхронного счетчика 2 изменяется (замедляется ) на 21С/2КсцПри подаче логического уровня 1 на вход добавления (фиг. 2в J-K триггер 4 начинает управляться по своим синхронным входам J, К и С . С вьгкода элемента блокировки 5 на К-вход J-K триггера 4 поступает сигнал 1, на J-входе триггера 4 постоянно присутствуетосигнал i. Триггер I периодически изменяет состояние (фиг. 2е и когда сигнал на его выходе принимает значение О,

J-K триггер 4 следующим синхроимпульсом переводится в состояиие О фиг. 2д). Одновременно J-K триггер 1 переходит в состояние 1 (фиг. 2 Появление логического О на выходе J-K триггера 4 переводит элемент блокировки 5 в состояние О. Очередной синхроимпульс не изменяет состояния триггера 1 (фиг. 2е), так как на его J и К-входы подан логический О с выхода триггера 4, но в то же время изменяет состояние триггеров синхронного счетчика 2 (фиг. 2ж, 3, и), так как на их J и k-входы поступает логическая 1 с выхода триггера 1 и изменяет состояние триггера 4, возвращая его в 1. Выходной сигнал О элемента блокировки 5, подаваемый на k-вход триггера 4, препятствует повторному переключению последнего в О. Возврат элемента блокировки 5 в 1 осуществляется окончанием входного сигнала управления устройства. Таким образом, в результате подачи логического уровня 1 на вход добавления фаза выходного сигнала синхронного счетчика 2 изменяется (ускоряется) на 2TC/2Kci|,

Данное устройство обладает повышенной надежностью работы,поскольку отсутствуют ложные срабатывания, так какJ-К триггер 3 переходит в

одновременно с лереходом в.О триггеров I и 6 (фиг, 2е, г, ж)т.е. не возникает комбинация состояний триггеров, вызывающей ложное срабатыванне.

Устройство для дискретной регулировки фазы обладает быстродействием, максимально реализуемым при выбранной элементной базе, т.е. равным

быстродействию одного отдельно взятого, триггера, обеспечивает возможность оперативного съема информации о фазе, и надежность его работы гарантируется при подаче несинхронизированных управляющих сигналов.

Формула изобретения

Устройство для дискретной регулировки фазы пооавт. св. IP 779904, отличающееся тем, что, с целью повышения надежности работы при оперативном съеме информации

третий К- вход первого дополнительного триггера соединен с выходом триггера первого разряда счетчика.

Источники информации, принятые во внимание при экспертизе

30

фуг. f

Авторы

Даты

1981-10-07—Публикация

1979-06-25—Подача