Изобретение относится к вычислитель- ной технике, может быть использовано в многоканальных системах обработки информации.

Цель изобретения - повышение быстродействия устройства за счет обслуживания М источников информации п блоками регистрации в любых сочетаниях.

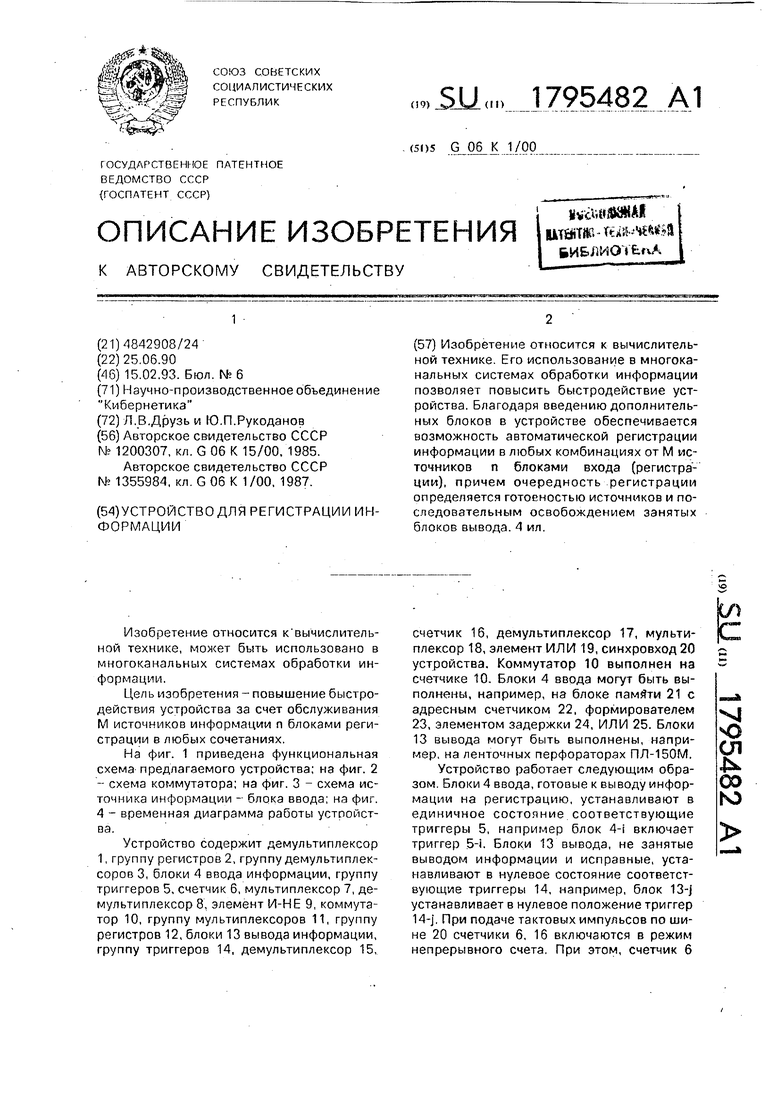

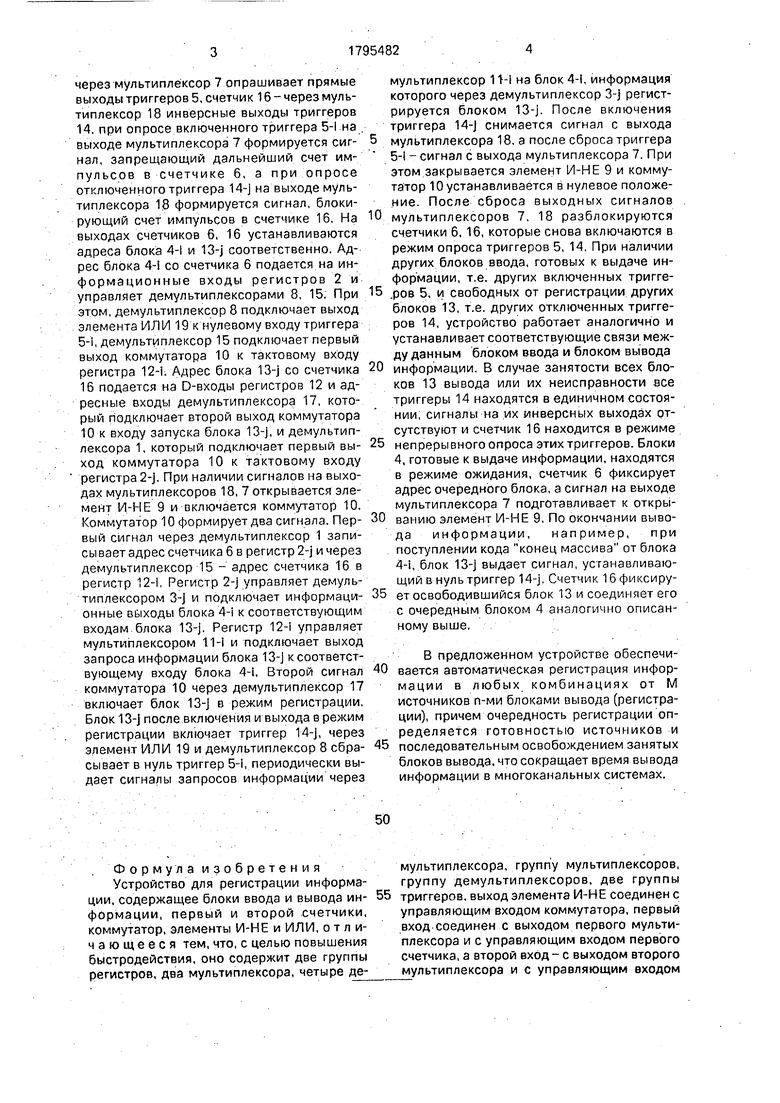

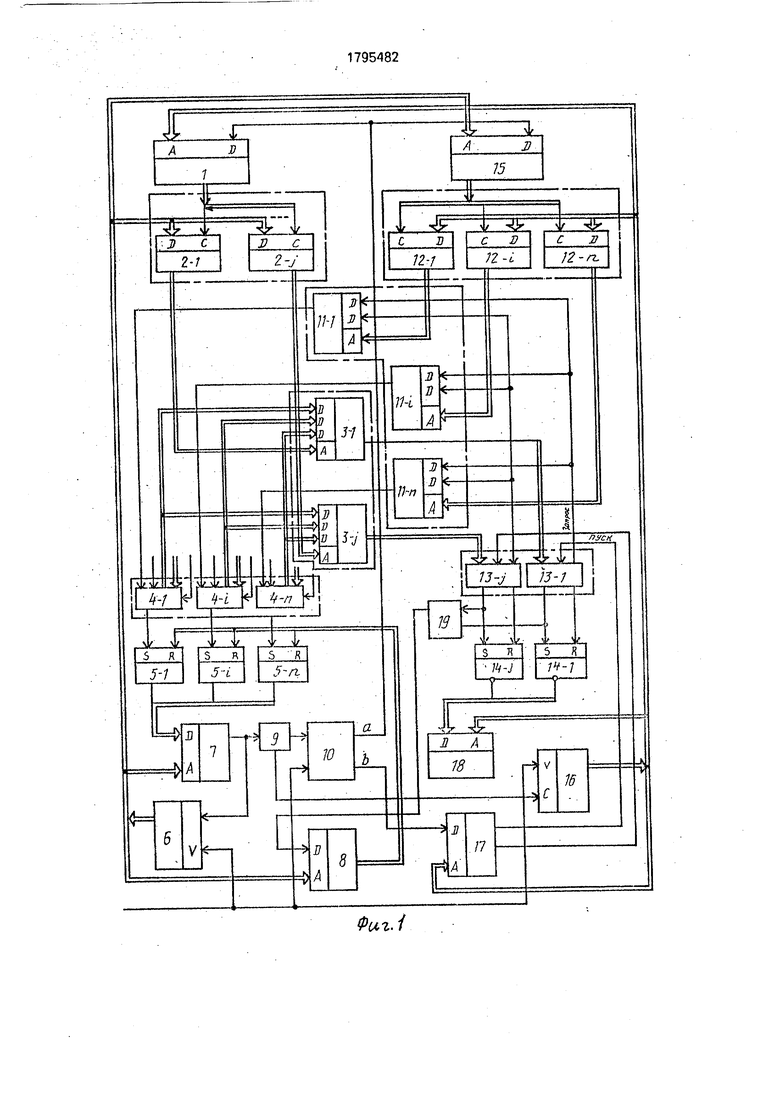

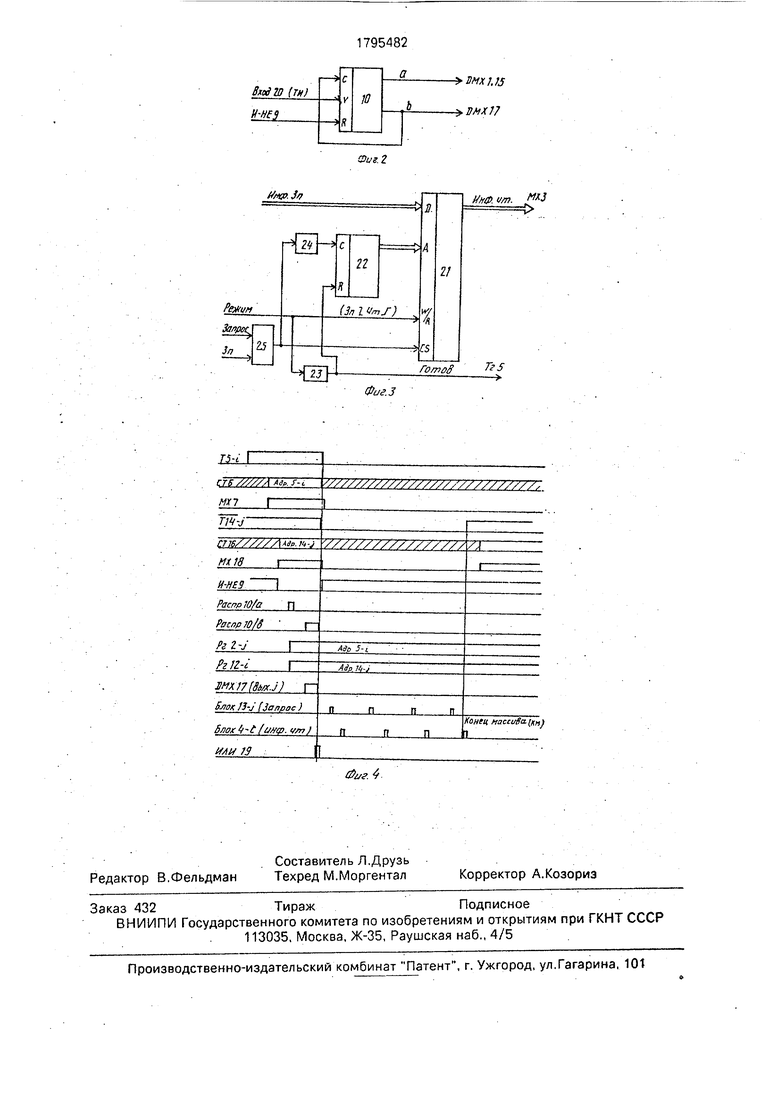

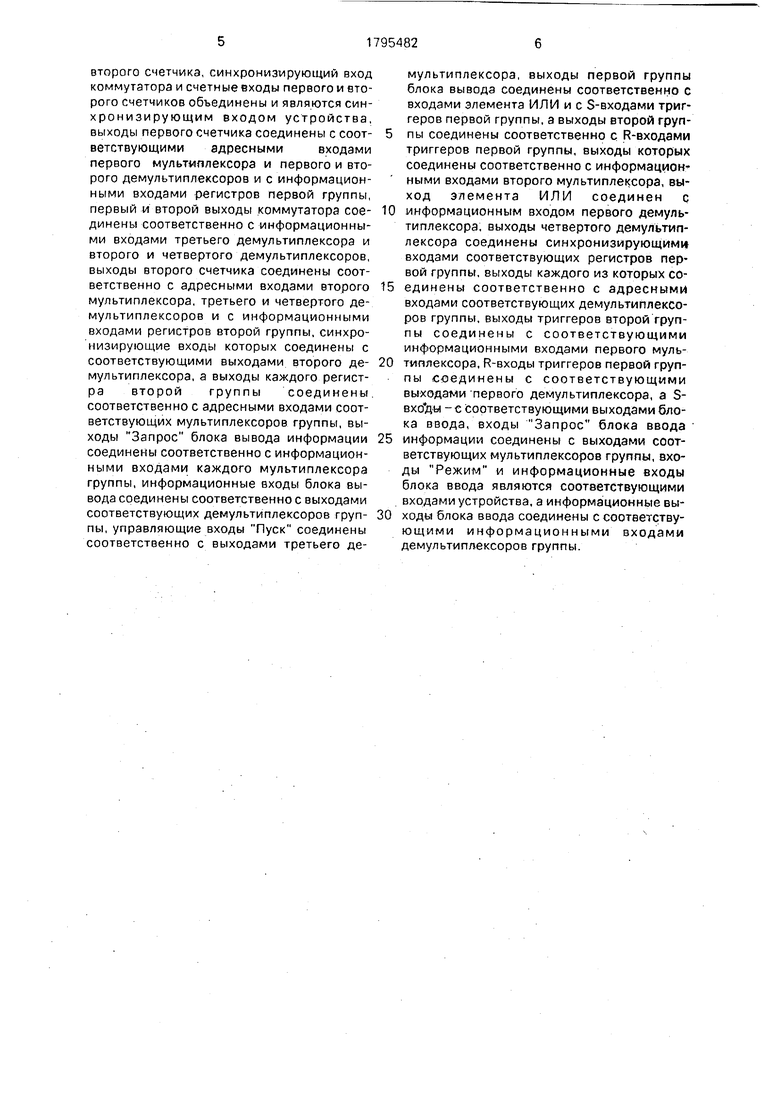

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - схема коммутатора; на фиг. 3 - схема источника информации - блока ввода; на фиг. 4 - временная диаграмма работы устройства.

Устройство содержит демультиплексор 1, группу регистров 2, группу демультиплек- соров 3, блоки 4 ввода информации, группу триггеров 5, счетчик 6, мультиплексор 7, демультиплексор 8, элемент И-НЕ 9, коммутатор 10, группу мультиплексоров 11, группу регистров 12, блоки 13 вывода информации, группу триггеров 14, демультиплексор 15,

счетчик 16, демультиплексор 17, мультиплексор 18, элемент ИЛИ 19, синхровход 20 устройства. Коммутатор 10 выполнен на счетчике 10. Блоки 4 ввода могут быть выполнены, например, на блоке памйти 21 с адресным счетчиком 22, формирователем 23, элементом задержки 24, ИЛИ 25. Блоки 13 вывода могут быть выполнены, например, на ленточных перфораторах ПЛ-150И. Устройство работает следующим образом. Блоки 4 ввода, готовые к выводу информации на регистрацию, устанавливают в единичное состояние соответствующие триггеры 5, например блок 4-i включает триггер 5-i. Блоки 13 вывода, не занятые выводом информации и исправные, устанавливают в нулевое состояние соответствующие триггеры 14, например, блок 13-J устанавливает в нулевое положение триггер 14-j. При подаче тактовых импульсов по шине 20 счетчики 6, 16 включаются в режим непрерывного счета. При этом, счетчик б

СЛ N 00

ю

через мультиплексор 7 опрашивает прямые выходы триггеров 5, счетчик 16 - через мультиплексор 18 инверсные выходы триггеров 14, при опросе включенного триггера 5-I на . выходе мультиплексора 7 формируется сигнал, запрещающий дальнейший счет импульсов в счетчике 6, а при опросе отключенного триггера 14-J на выходе мультиплексора 18 формируется сигнал, блокирующий счет импульсов в счетчике 16. На выходах счетчиков 6, 16 устанавливаются адреса блока 4-I и 13-J соответственно. Адрес блока 4-I со счетчика 6 подается на информационные входы регистров 2 и управляет демультиплексорами 8, 15. При этом, демультиплексор 8 подключает выход элемента ИЛИ 19 к нулевому входу триггера 54 демультиплексор 15 подключает первый выход коммутатора 10 к тактовому входу регистра 124. Адрес блока 13-j со счетчика 16 подается на D-входы регистров 12 и адресные входы демультиплексора 17, который Подключает второй выход коммутатора 10 к входу запуска блока 13-j, и демультиплексора 1, который подключает первый выход коммутатора 10 к тактовому входу регистра 2-J. При наличии сигналов на выходах мультиплексоров 18, 7 открывается элемент И-НЕ 9 и включается коммутатор 10. Коммутатор 10 формирует два сигнала. Первый сигнал через демультиплексор 1 записывает адрес счетчика 6 в регистр 2-j и через демультиплексор 15 - адрес счетчика 16 в регистр 124 Регистр 2-j управляет демуль- типлексором З-j и подключает информационные выходы блока 4-i к соответствующим входам блока 13-j. Регистр 12-i управляет мультиплексором 11-1 и подключает выход запроса информации блока 13-j к соответствующему входу блока 4-i, Второй сигнал коммутатора 10 через демультиплексор 17 включает блок 13-j в режим регистрации. Блок 13-j после включения и выхода в режим регистрации включает триггер 14-j, через элемент ИЛИ 19 и демультиплексор 8 сбрасывает в нуль триггер 54 периодически выдает сигналы запросов информации через

мультиплексор 1 И на блок 4-i, информация которого через демультиплексор З-j регистрируется блоком 13-j. После включения триггера 14-j снимается сигнал с выхода

мультиплексора 18. а после сброса триггера 5-I - сигнал с выхода мультиплексора 7. При этом закрывается элемент И-НЕ 9 и коммутатор 10 устанавливается в нулевое положение. После сброса выходных сигналов

мультиплексоров 7, 18 разблокируются счетчики 6, 16, которые снова включаются в режим опроса триггеров 5, 14, При наличии других блоков ввода, готовых к выдаче информации, т.е. других включенных триггеров 5, и свободных от регистрации других блоков 13, т.е. других отключенных триггеров 14, устройство работает аналогично и устанавливает соответствующие связи между данным блоком ввода и блоком вывода

информации. В случае занятости всех блоков 13 вывода или их неисправности все триггеры 14 находятся в единичном состоянии; сигналы на их инверсных выходах отсутствуют и счетчик 16 находится в режиме

непрерывного опроса этих триггеров. Блоки 4, готовые к выдаче информации, находятся в режиме ожидания, счетчик 6 фиксирует адрес очередного блока, а сигнал на выходе мультиплексора 7 подготавливает к открыванию элемент И-НЕ 9. По окончании вывода информации, например, при поступлении кода конец массива от блока 4-i, блок 13-j выдает сигнал, устанавливающий в нуль триггер 14-j, Счетчик 16фиксирует освободившийся блок 13 и соединяет его с очередным блоком 4 аналогично описанному выше.

В предложенном устройстве обеспечи- вается автоматическая регистрация информации в любых комбинациях от М источников n-ми блоками вывода (регистрации), причем очередность регистрации определяется готовностью источников и последовательным освобождением занятых блоков вывода, что сокращает время вывода информации в многоканальных системах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для измерения скорости перемещения | 1989 |

|

SU1732281A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

Изобретение относится к вычислительной технике. Его использование в многоканальных системах обработки информации позволяет повысить быстродействие устройства. Благодаря введению дополнительных блоков в устройстве обеспечивается возможность автоматической регистрации информации в любых комбинациях от М источников п блоками входа (регистрации), причем очередность регистрации определяется готовностью источников и последовательным освобождением занятых блоков вывода. 4 ил.

Форму л а изобретения Устройство для регистрации информации, содержащее блоки ввода и вывода ин- формации, первый и второй счетчики, коммутатор, элементы И-НЕ и ИЛИ, отличающееся тем, что, с целью повышения быстродействия, оно содержит две группы регистров, два мультиплексора, четыре демультиплексора, группу мультиплексоров, группу демультиплексоров, две группы триггеров, выход элемента И-НЕ соединен с управляющим входом коммутатора, первый вход соединен с выходом первого мультиплексора и с управляющим входом первого счетчика, а второй вход- с выходом второго мультиплексора и с управляющим входом

второго счетчика, синхронизирующий вход коммутатора и счетные входы первого и второго счетчиков объединены и являются синхронизирующим входом устройства, выходы первого счетчика соединены с соот- ветствующими адресными входами первого мультиплексора и первого и второго демультиплексоров и с информационными входами регистров первой группы, первый и второй выходы коммутатора сое- динены соответственно с информационными входами третьего демультиплексора и второго и четвертого демультиплексоров, выходы второго счетчика соединены соответственно с адресными входами второго мультиплексора, третьего и четвертого демультиплексоров и с информационными входами регистров второй группы, синхронизирующие входы которых соединены с соответствующими выходами второго де- мультиплексора, а выходы каждого регистра второй группы соединены соответственно с адресными входами соответствующих мультиплексоров группы, выходы Запрос блока вывода информации соединены соответственно с информационными входами каждого мультиплексора группы, информационные входы блока вывода соединены соответственно с выходами соответствующих демультиплексоров труп- пы, управляющие входы Пуск соединены соответственно с выходами третьего демультиплексора, выходы первой группы блока вывода соединены соответственно с входами элемента ИЛИ и с S-входами триггеров первой группы, а выходы второй группы соединены соответственно с R-входами триггеров первой группы, выходы которых соединены соответственно с информацией ными входами второго мультиплексора, выход элемента ИЛИ соединен q информационным входом первого демультиплексора, выходы четвертого демультиплексора соединены синхронизирующими входами соответствующих регистров первой группы, выходы каждого из которых соединены соответственно с адресными входами соответствующих демультиплексоров группы, выходы триггеров второй группы соединены с соответствующими информационными входами первого мультиплексора, R-входы триггеров первой груп- пы соединены с соответствующими выходами-первого демультиплексора, a S- вхо ды -с соответствующими выходами блока ввода, входы Запрос блока ввода информации соединены с выходами соответствующих мультиплексоров группы, входы Режим и информационные входы блока ввода являются соответствующими входами устройства, а информационные выходы блока ввода соединены с соответствующими информационными входами демультиплексоров группы.

Ahp.j/r

гЧ

ЖН

Ре#ун

(Зп I UmS)

ЗапрмЛ Зп

23

BMX},JS

VMX17

. vm.

-j

22

21

romog Тг5

| Устройство для вывода информации | 1983 |

|

SU1200307A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР N51355984, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-15—Публикация

1990-06-25—Подача