Интегрирующие устройства для коррекции фазы приемного распределителя на регистрах сдвига, построенные на ферритовых сердечниках с прямоугольной петлей гистерезиса, известны. Эти устройства входят как составная часть в устройства корректирования фазы управляющих импульсов распределителя. Интегрирующее устройство может быть включено, например, в синхронную телеграфную аппаратуру между фазовым дискриминатором, и узлом, управляющим фазой импульсов приемного генератора. В известных устройствах запрещается выдача корректирующих импульсов в моменты изменения знака фазы. При емкости интегрирующего устройства в я знаков число корректирующих импульсов в моменты изменения знака фазы уменьшается на п. Это приводит к дополнительному расхождению фаз между передающими и приемными распределителями, определяемому нестабильностью задающ1 Х генераторов.

В предложенном устройстве для сокращения времени фазирования и защиты схемы коррекции от ложного фазирования при приеме одиночных сигналов с искажениями фронтов к выходам регистров сдвига подключены клапанные схемы, а выходы фазового дискриминатора соединены со входами клапанов и управляемым устройством.

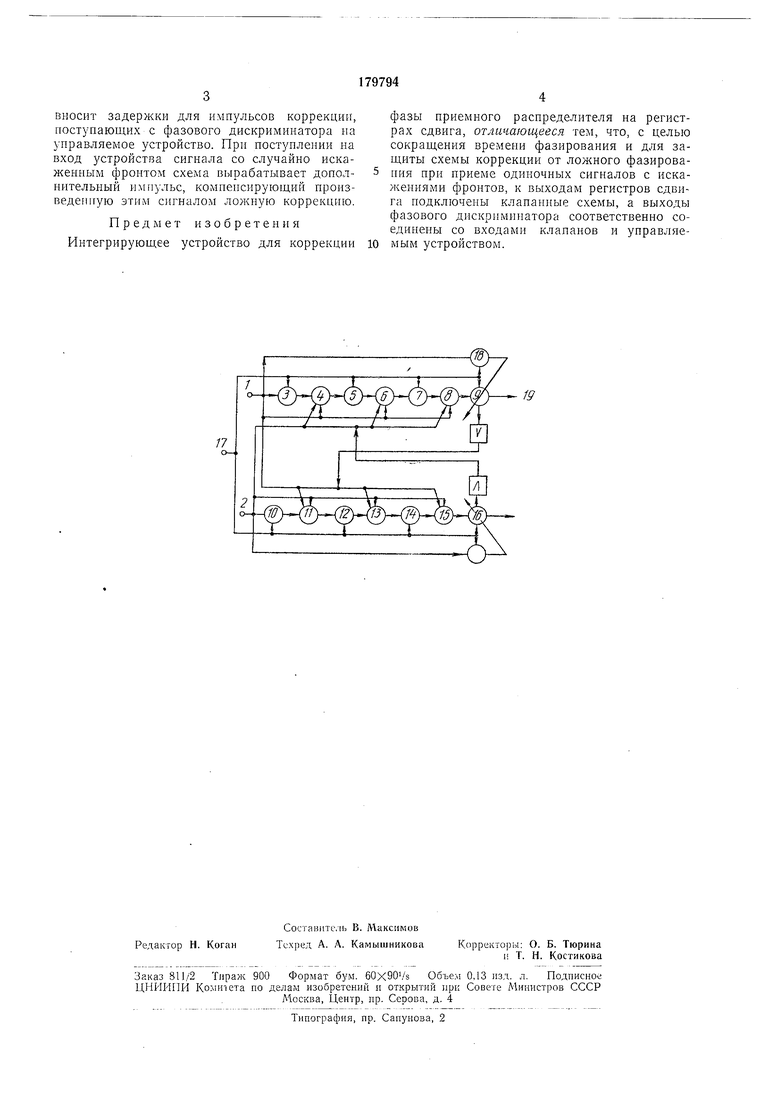

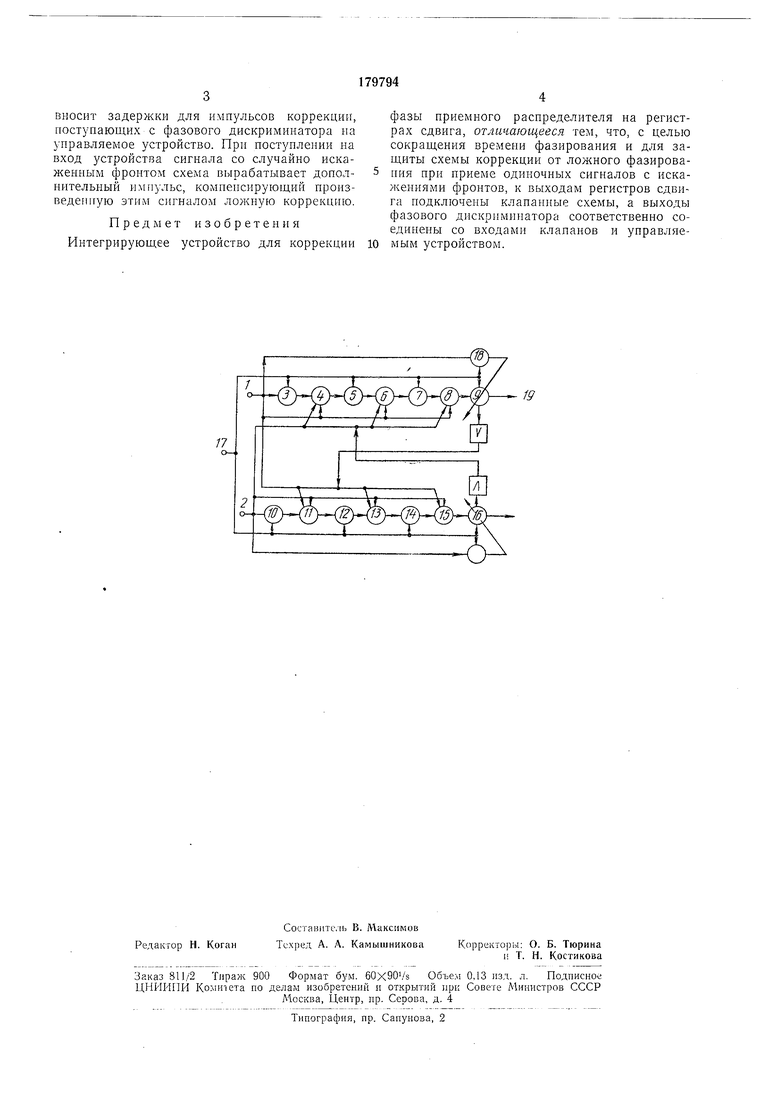

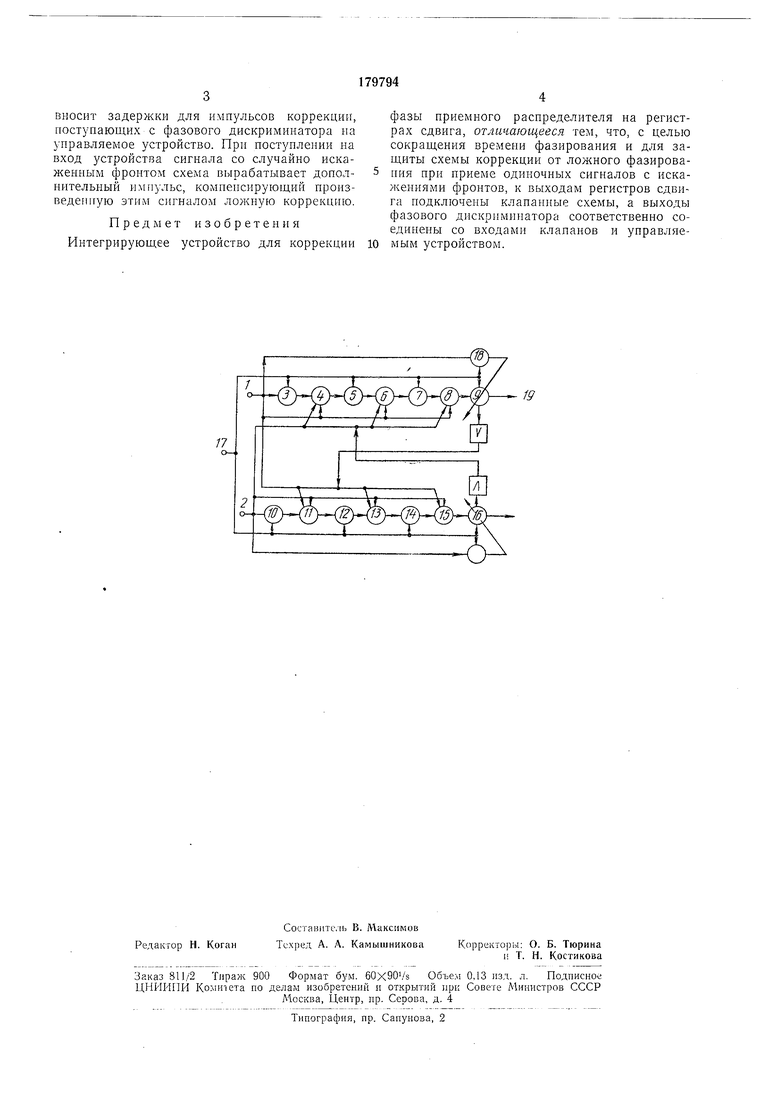

Функциональная схема интегрирующего устройства для коррекции фазы приемного распределителя на регистрах сдвига приведена на чертеже.

Сигналы с фазового дискриминатора поступают на входы / и 2. Со входами связаны регистры сдвига на ферритовых сердечниках с прямоугольной петлей гистерезиса. Первый регистр состоит из ячеек 3-5, а второй регистр из ячеек 10-16. Продвигаюигие им-пульсы подаются на вход 17.

При поступлении сигналов на вход / производится запись «1 в ячейки 3 п 18 считывание «1 с ячеек 4, 6, 8, а с ячеек

П, 13, 15. При продвнженип единиц по регистру они последовательно проходят по ячейкам 5-9, но на выходе регистра сигнал запрещается. Запрещающий импульс поступает с ячейки 18.

При поступлении сигнала на вход 2 производится занись «1 в ячейку 10 и считывание «1 с ячеек 11, 13, 15, а также с ячеек 4, 6, 8, тем самым в регистре происходит сдвнг информации, )1 «1 с ячейки 5 переписывается Б

ячейку 9. Так как в ячейке 18 «1 не записана, то на выходе 19 появляется корректирующий импульс, который поступает затем на управляемое устройство.

вносит задержки для импульсов коррекции, иоступающих с фазового дискриминатора на управляемое устройство. При поступлении на вход Зстройства сигнала со случайно искаженным фронтом схема вырабатывает дополнительный импульс, компенсирующий произведенную этим сигналом ложную коррекцию.

Предмет изобретения Интегрирующее устройство для коррекции

фазы приемного распределителя на регистрах сдвига, отличающееся тем, что, с целью сокращения времени фазирования и для защиты схемы коррекции от фазироваиия при приеме одиночных сигналов с искажениями фронтов, к выходам регистров сдвига подключены клапанные схемы, а выходы фазового дискриминатора соответственно соединены со входами клапанов и управляемым устройством.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФАЗИРОВАНИЯ ИМПУЛЬСОВ | 1969 |

|

SU248757A1 |

| Способ автоподстройки фазы в электронном синхронном телеграфном аппарате и устройство для осуществления этого способа | 1958 |

|

SU117757A1 |

| ДЕШИФРАТОР КОРРЕКТИРУЮЩЕГО КОДА В КАНАЛЕ | 1971 |

|

SU308509A1 |

| Способ фазирования систем с переменным шагом коррекции | 1959 |

|

SU126519A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ДИСКРЕТНЫХ СИГНАЛОВ в СИСТЕМАХ ПРЕРЫВИСТОЙ СВЯЗИ | 1973 |

|

SU405182A1 |

| Устройство синхронизации | 1981 |

|

SU1003376A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

Даты

1966-01-01—Публикация