Данное изобретение относится к области синхронизации в телемеханических системах.

Известны способы фазирования кодов, заключающиеся в многократном анализе «еди«иц, расположенных на определенных позициях передаваемого сообщения.

Предлагаемый способ отличается от известных тем, что в начале каждого цикла передачи информационных импульсов посылают стартовый сигнал в виде серии импульсов, сдвинутых по фазе, в течение приема стартового сигнала накапливают величины рассогласования фаз между информационными импульсами как в сторону опережения, так и в сторону отставания, и после приема стартового сигнала сравнивают накопленные величины рассогласования фаз и корректируют фазу управляющих импульсов по результату сравнения.

Это позволяет повысить точность фазирования.

Сущность способа заключается в том, что фаза колебаний тактового генератора приемника корректируется один раз за цикл, причем корректирующий сигнал вырабатывается по средней величине рассогласования фаз, накапливаемой во время приема в начале цикла специального стартового сигнала, обладающего достаточным числом фронтов.

принимаемых импульсов, восстановленных из искаженного помехами сигнала. Далее тактовый генератор приемника работает независимо до окончания данного цикла, что исключает влияние помех в канале связи на синфазность во время приема кодов каналов информации. Кроме того, стартовая серия молсет нести в себе дополнительные сведения о виде передаваемой в данном цикле информации, для чего

выбирается несколько типов стартового сигнала.

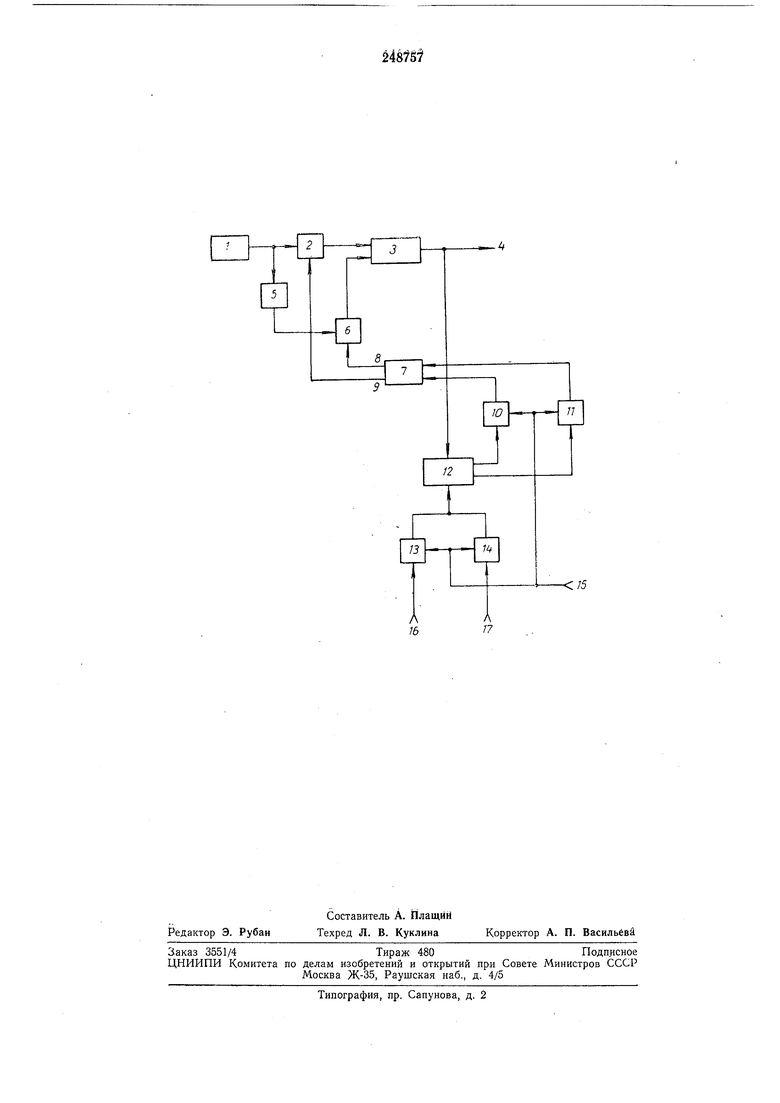

На чертеже приведена упрощенная блок-схема реализации предлагаемого способа фазирования импульсов, где / - задающий генератор; 2 - вентиль; 3 - делитель частоты; 4 - выход; 5 - инвертор; 6 - вентиль; 7 - узел сравнения; 8, 9 - депи управления; 10, 11 - интеграторы; 12 - фазовый дискриминатор; 13, 14 - вентили; 15-,17 - входы.

Во время приема кода каналов информации фазовый дискриминатор 12, интеграторы 10, 11 и узел сравнения 7 не работают, так как на вентили 13, 14 и интеграторы 10, 11 поступает запрещающий сигнал от распределителя каналов информации (вход 15). При этом от узла сравнения 7 на вентиль 2 поступает по цепи 9 разрешающий сигнал, позволяющий основной серии импульсов через вентиль 2 воздействовать на вход делителя частоты 3. Последний

число раз, чтобы частота тактовых импульсов, появляющихся на выходе 4, равнялась скорости передачи системы. На вентиль 6 от узла 7 поступает сигнал по цепи 8, запрещающий импульсам от инвертора 5 воздействовать на вход делителя частоты. Инвертор 5 образует дополнительную серию импульсов, сдвинутую по фазе относительно основной на 180°.

Следовательно, во время приема элементов кода каналов информации на делитель частоты через вентиль 2 поступает непрерывная последовательность импульсов от генератора I, и фаза появляющихся на выходе 4 тактовых импульсов управления не зависит от фазы принимаемых импульсов кода.

После окончания цикла начинается прием элементов кода стартового сигнала, и на вход 15 от распределителя каналов поступает сигнал, разрещающий работу вентилям 13, 14 и интеграторам W, 11. П-риходящие на входы 16, 17 фронты и спады принимаемых элементов кода через вентили 13, 14 воздействуют на фазовый дискриминатор 12, определяющий знак расходования по фазе между тактовыми и принимаемыми импульсами. Если тактовые импульсы опережают принимаемые, то дискриминатор 12 формирует импульсы опережения, которые поступают на вход интегратора 10. Если принимаемые импульсы опережают тактовые, то дискриминатор 12 образует импульсы отставания, воздействующие на вход интегратора 11. Интеграторы 10 и 11 интегрируют поступающие на их входы импульсы опережения и отставания и после приема последнего элемента кода стартового сигнала формируют импульсы, длительности которых пропорциональны накопленным величинам расхождения по фазе. Длительности импульсов опережения и отставания сравниваются в узле 7, и на его выходе образуется сигнал, определяющий среднюю величину и знак расхождения по фазе.

Если длительность импульсов опережений больще длительности импульса отставания, то формируется сигнал опережения (цепь 9), который запрещает прохождение импульсов через вентиль 2. Если же больще длительность импульса отставания, то формируется сигнал отставания (цепь S), который разрещает импульсам от инвертора 5 проходить через вентиль 6.

Следовательно, в первом случае фаза тактовых импульсов смещается в сторону отставания, а во втором - в сторону опережения. Таким образом, при использовании предлагаемого способа фазирование импульсов осуществляется только во время приема стартового сигнала, по окончании которого устройство фазирования вырабатывает выходной сигнал, длительность которого пропорциональна средней величине рассогласования по фазе.

Этот сигнал, запрещающий поступление импульсов на вход делителя частоты при опережении и добавляющий импульсы на вход делителя при отставании, корректирует фаз,у тактовых импульсов генератора приемника.

П.редмет изобретения

Способ фазирования импульсов в телемеханических системах, отличающийся тем, что, с

целью повышения точности (фазирования, в начале каждого цикла передачи информационных импульсов посылают стартовый сигнал в виде серии импульсов, сдвинутых по фазе, в течение приема стартового сигнала накапливают величины рассогласования фаз между информационными импульсами как в сторону опережения, так и в сторону отставания, и после приема стартового сигнала сравнивают накопленные величины рассогласования фаз и

корректируют фазу управляющих импульсов по результату сравнения.

--i/

/5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для асинхронной передачицифРОВОй иНфОРМАции пО СиНХРОННОМуКАНАлу СВязи | 1978 |

|

SU803109A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯХАРАКТЕРИСТИКИ ГРУППОВОГО ВРЕМЕНИЗАПАЗДЫВАНИЯ | 1972 |

|

SU428309A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство тактовой синхронизации | 1986 |

|

SU1411990A1 |

| Устройство фазирования бинарного сигнала | 1981 |

|

SU1075431A1 |

| Преобразователь кода во временной интервал | 1987 |

|

SU1474848A1 |

| ВСЕСОЮаНАЯ i | 1973 |

|

SU372717A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

Авторы

Даты

1969-01-01—Публикация