Изобретение относится к области импульсной техники и предназначено для синхронизации дискретных сигналов в системах передачи дискретной информации по каналам с переменными параметрами (метеорная и КВсвязь), а также по каналам телеуправления, когда команды на объект подаются в течение коротких сеансов связи.

Известны устройства синхронизации дискретных сигналов в системах прерывистой связи, содержащие кварцевый генератор, управляющий соответственно делителем частоты непосредственно и через решающий блок регистром сдвига, выходы разрядов которого подключены к входам блока опознавания стартовой комбинации (ОСК), а также схемы «НЕТ и триггер.

Однако в таких устройствах отсутствует коррекция фазы выходных импульсов в процессе сеанса связи при флуктуациях фазы групп сигналов в каналах с многолучевым распространением, что ведет к дополнительным потерям полезного времени на фазирование.

Цель изобретение - сокращение времени вчождриия в синхронизм.

Это достигается тем, что между дополнительными выходами блока ОСК и одним из входов схемы «НЕТ включен блок опознавания корректирующей комбинации (ОКК), а между основным выходом блока ОСК, соединенным с выходом блока ОКК, и входами делителя частоты включены последовательно соединенные счетчик и блок памяти, причем соответствующий выход кварцевого генератора дополнительно подключен ко второму входу схемы «НЕТ, выход которой подключен непосредственно и через счетчик к входам триггера, выходы которого, в свою очередь, подключены соответственно к входам запуска блока ОКК и блока памяти.

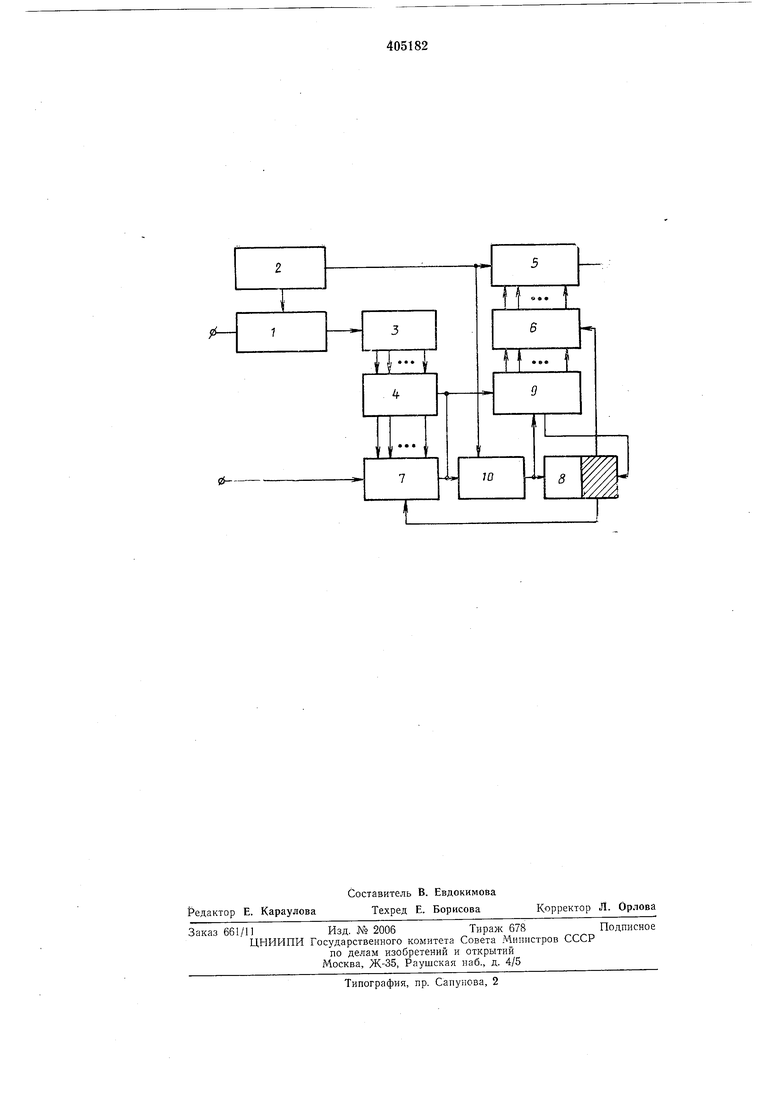

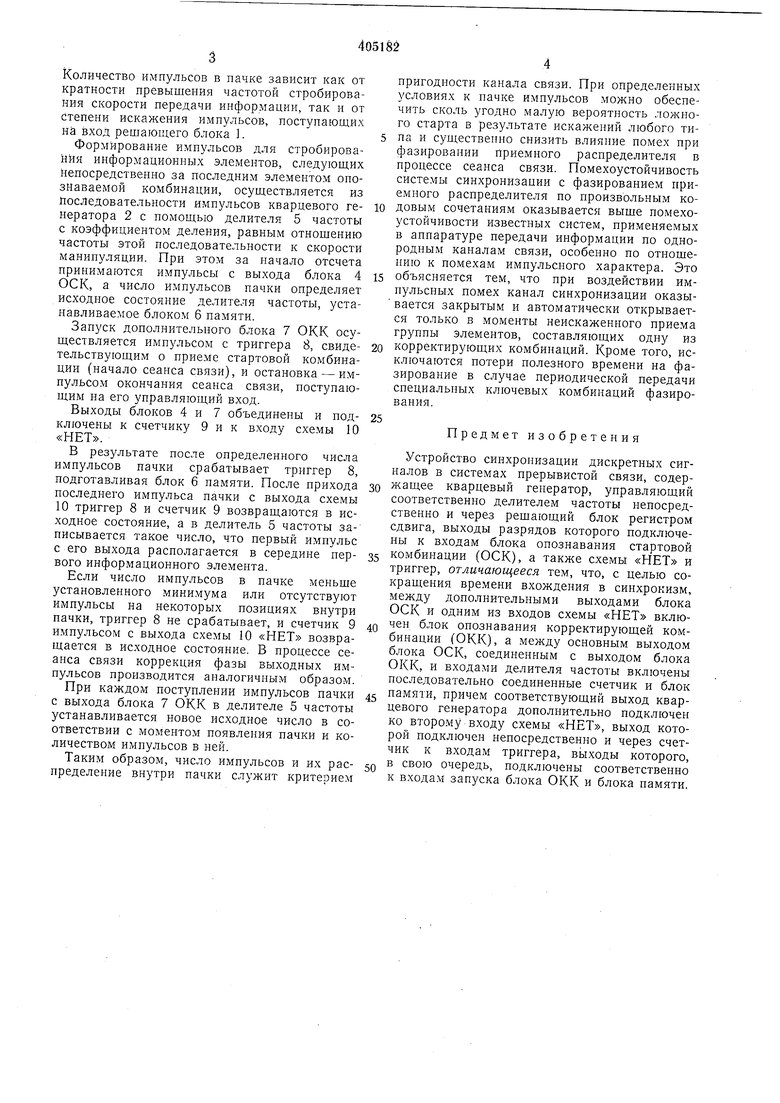

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит решающий блок 1, кварцевый генератор 2, регистр 3 сдвига, блок 4 ОСК, делитель 5 частоты, блок 6 памяти, блок 7 ОКК, триггер 8, счетчик 9 и схему 10 «НЕТ.

Сигнал с выхода приемника поступает на вход решающего блока 1, где стробируется с частотой кварцевого генератора 2, частота которого выше или кратна скорости манипуляции, и записывается в регистр 3 сдвига. Продвижение информации по регистру сдвига осуществляется в такт с импульсами стробирования.

Нмпульсы с выходов ячеек регистра 3 сдвига поступают на блок 4 ОСК, на выходе которого в момент прихолта последнего элемента комбинации ноявляется начка импульсов, Количество импульсов в пачке зависит как от кратности превыщепия частотой стробирования скорости передачи информации, так и от Степени искажения импульсов, поступающих на вход рещающего блока 1. Формирование имнульсов для стробированйя информационных элементов, следующих непосредственно за последним элементом онознаваемой комбинации, осуществляется из последовательности импульсов кварцевого ге- ю нератора 2 с помощью делителя 5 частоты с коэффициентом деления, равным отношению частоты этой последовательности к скорости манипуляции. При этом за начало отсчета принимаются импульсы с выхода блока 4 ОС К, а число импульсов пачки определяет исходное состояние делителя частоты, устанавливаемое блоком 6 памяти. Запуск дополнительного блока 7 ОКК осуществляется импульсом с триггера 8, свидё- 20 тельствующим о приеме стартовой комбинации (начало сеанса связи), и остановка - импульсом окончания сеанса связи, поступающим на его управляющий вход. Выходы блоков 4 и 7 объединены и под- 25 ключены к счетчику 9 и к входу схемы 10 «НЕТ. В результате после определенного числа импульсов пачки срабатывает триггер 8, подготавливая блок 6 памяти. После приходазо последнего импульса пачки с выхода схемы 10 триггер 8 и счетчик 9 возвращаются в исходное состояние, а в делитель 5 частоты записывается такое число, что первый импульс с его выхода располагается в середине пер-35 вого информационного элемента. Если число импульсов в пачке меньще установленного минимума или отсутствуют импульсы на некоторых позициях внутри пачки, триггер 8 не срабатывает, и счетчик 940 импульсом с выхода схемы 10 «НЕТ возвращается в исходное состояние. В процессе сеанса связи коррекция фазы выходных импульсов производится аналогичным образом. При каждом поступлении импульсов пачки45 с выхода блока 7 ОКК в делителе 5 частоты устанавливается новое исходное число в соответствии с моментом появления пачки и количеством импульсов в ней. Таким образом, число импульсов и их рас-50 пределение внутри пачки служит критерием 5 15 пригодности канала связи. При определенных условиях к пачке импульсов можно обеспечить сколь угодно малую вероятность ложного старта в результате искажений любого типа и суш.ествепно снизить влияние помех при фазировании приемного распределителя в процессе сеанса связи. Помехоустойчивость системы синхронизапии с фазированием приемного распределителя по произвольным кодовым сочетаниям оказывается выше помехоустойчивости известных систем, применяемых в аппаратуре передачи информации по однородным каналам связи, особенно по отпошепию к помехам импульсного характера. Это объясняется тем, что при воздействии импульсных помех канал синхронизации оказывается закрытым и автоматически открывается только в моменты неискаженного приема группы элементов, составляющих одну из корректирующих комбинаций. Кроме того, исключаются потери полезного времени на фазирование в случае периодической передачи специальных ключевых комбинаций фазирования. Предмет изобретения Устройство синхронизации дискретных сигналов в системах прерывистой связи, содержащее кварцевый генератор, управляющий соответственно делителем частоты непосредственно и через рещающий блок регистром сдвига, выходы разрядов которого подключены к входам блока опознавания стартовой комбинации (ОСК), а также схемы «НЕТ и триггер, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм, между дополнительными выходами блока ОСК и одним из входов схемы «НЕТ вклю блок опознавания корректирующей комбинации (ОКК), а между основным выходом блока ОСК, соединенным с выходом блока ОКК, и входами делителя частоты включены последовательно соединенные счетчик и блок памяти, причем соответствующий выход кварцевого генератора дополнительно подключен ко второму входу схемы «НЕТ, выход котоРОЙ подключен непосредственно и через счетчик к входам триггера, выходы которого. свою очередь, подключены соответственно к входам запуска блока ОКК и блока памяти.

9

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА ПЕРЕДАЧИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 1986 |

|

SU1840556A2 |

| Устройство для фазовой синхронизации | 1983 |

|

SU1149425A2 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ ДИСКРЕТНЫХ СИГНАЛОВ в СИСТЕМАХ ПРЕРЫВИСТОЙ СВЯЗИ | 1972 |

|

SU353361A1 |

| Устройство для кодирования и декодирования сигналов в системах передачи цифровых данных | 1980 |

|

SU1046959A1 |

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1984 |

|

SU1185617A2 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для определения достоверности передачи дискретной информации | 1989 |

|

SU1674387A1 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1982 |

|

SU1016845A1 |

Авторы

Даты

1973-01-01—Публикация