Изобретение относится к вычислительной технике и предназначено для использования 8 качестве вычислительной ячейки (ВЯ) однородной вычислительной структуры (ОВС), ориентированной на Цифровую обработку сигналов/объединение и распределение информации между различными абонентами,.

Целью изобретения является расширение возможностей В Я.

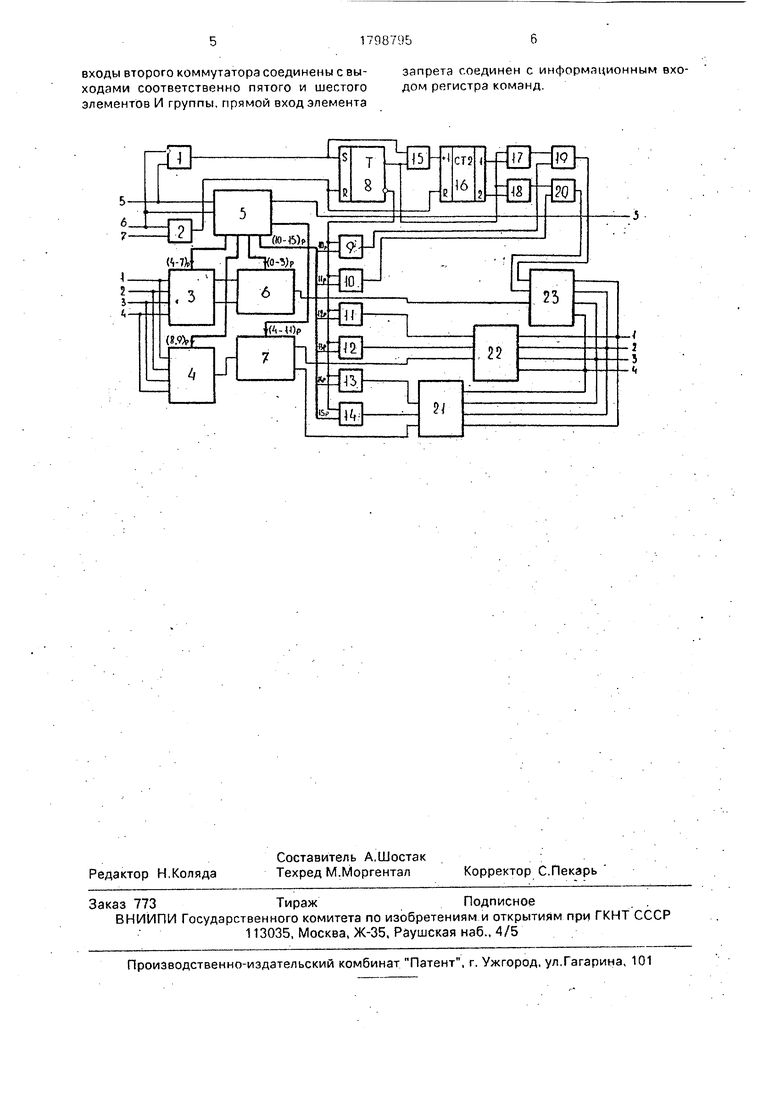

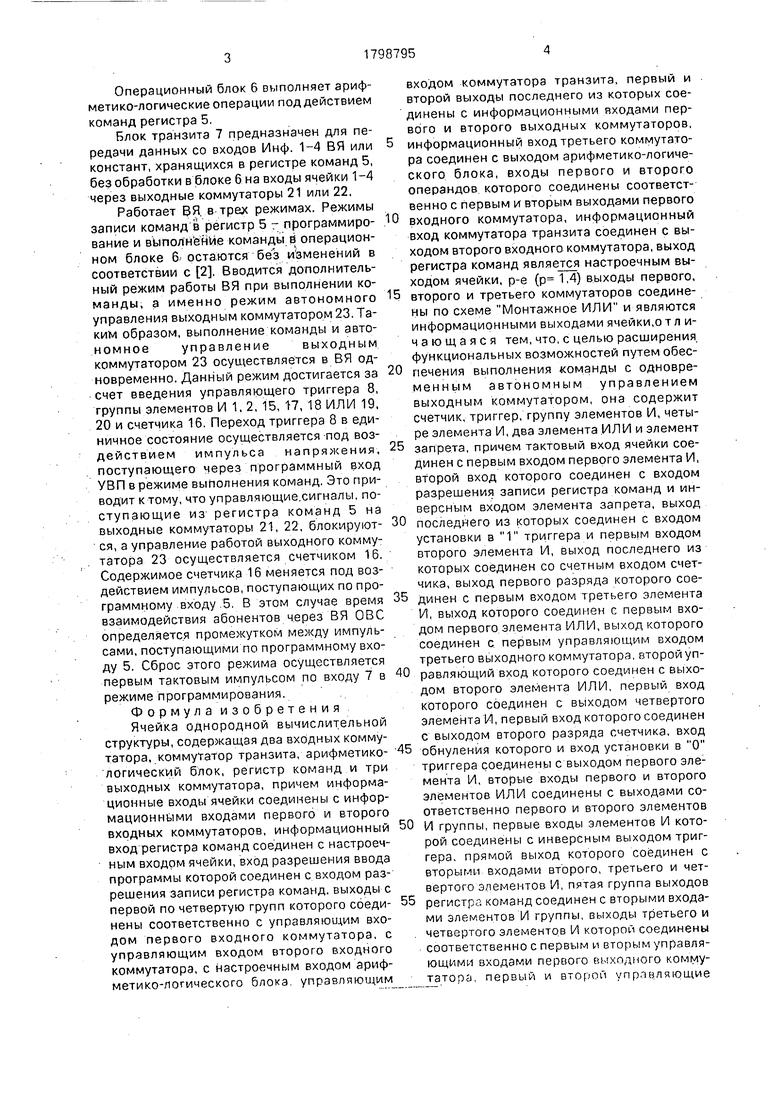

На чертеже показана структурная схема

вя.. ;: : ;. .- ; .

ВЯ содержит элементы И, 1, 2, 9-15, 17 и 18, входные коммутаторы З.и 4, регистр команды 5, операционный блок 6, блок транзита 7, триггер 8, счетчик 16, элементы ИЛИ 19 и 20 и выходные коммутаторы 21, 22. и 23.

ВЯ имеет четыре информационных входа - 1-4, вход программы настройки (Вх.П)- 5, вход управления вводом программы (УВП)- 6, вход синхронизирующих тактовых импульсов (ТИ) - 7, а также четыре информационных выхода - 1-4 и выход программы настройки (Вых.П) ВЯ - 5.

Устройство работает следующим образом. Регистр команд 5 предназначен для приема по входу Вх.П 5 при наличии разрешающего сигнала на входе УВП 6 и передачи по выходу Вых.П 5 управляющей поелёдователЮности - программы настройки ВЯ ОВС на.заданные функции. В 16-раз- рядный. регистр 5 в режиме программирования записывается программа работы ВЯ и через него транслируются программы для Эаписи в другие ВЯ.

V4

О 00 VI О СЛ

Операционный блок 6 выполняет арифметико-логические операции под действием команд регистра 5.

Блок транзита 7 предназначен для передачи данных со входов Инф. 1-4 ВЯ или констант, хранящихся в регистре команд 5, без обработки в блоке 6. на входы ячейки 1-4 через выходные коммутаторы 21 или 22,

Работает ВЯ. в трех режимах. Режимы записи команд в регистр 5 - программирование и выполнение команды а операционном блоке 6 остаются без изменений в соответствии с 2. Вводится дополнительный режим работы ВЯ при выполнении команды, а именно режим автономного управления выходным коммутатором 23. Таким образом, выполнение команды и автономное управление выходным коммутатором 23 осуществляется в ВЯ одновременно. Данный режим достигается за счет введения управляющего триггера 8, труппы элементов И 1, 2, 15, г7, 18 ИЛИ 19, 20 и счетчика 16. Переход триггера 8 в единичное состояние осуществляется под воздействием импульса напряжения, поступающего через программный вход УВП в режиме выполнения команд. Это приводит к тому, что управляющие.сигналы, поступающие из регистра команд 5 на выходные коммутаторы 21, 22, блокируются, а управление работой выходного коммутатора 23 осуществляется счетчиком 16. Содержимое счетчика 16 меняется под воздействием импульсов/поступающих по программному входу.5. В этом случае время взаимодействия абонентов через ВЯ ОВС определяется промежутком между импульсами, поступающими по программному входу 5. Сброс этого режима осуществляется первым тактовым импульсом по входу 7 в режиме программирования.

Формула изобретения

Ячейка однородной вычислительной структуры, содержащая два входных коммутатора, коммутатор транзита, арифметико- логический блок, регистр команд и три выходных коммутатора, причем информационные входы ячейки соединены с информационными входами первого и второго входных коммутаторов, информационный вход регистра команд соединен с настроечным входом ячейки, вход разрешения ввода программы которой соединен с входом разрешения записи регистра команд, выходы с первой по четвертую групп которого соединены соответственно с управляющим входом первого входного коммутатора, с управляющим входом второго входного коммутатора, с настроечным входом арифметико-логического блока, управляющим

0

0

входом коммутатора транзита, первый и второй выходы последнего из которых соединены с информационными входами первого и второго выходных коммутаторов,

информационный вход третьего коммутатора соединен с выходом арифметико-логического блока, входы первого и второго операндов которого соединены соответственно с первым и вторым выходами первого

0 входного коммутатора, информационный вход коммутатора транзита соединен с выходом второго входного коммутатора, выход регистра команд являе гся настроечным выходом ячейки, р-е (р 1,4) выходы первого,

5 второго и третьего коммутаторов соединены по схеме Монтажное ИЛИ и являются информационными выходами ячейки,о т л и- чающаяся тем, что, с целью расширения функциональных возможностей путем обеспечения выполнения команды с одновременным автономным управлением выходным коммутатором, она содержит счетчик, триггер, группу элементов И, четыре элемента И, два элемента ИЛИ и элемент

5 запрета, причем тактовый вход ячейки соединен с первым входом первого элемента И, второй вход которого соединен с входом разрешения записи регистра команд и инверсным входом элемента запрета, выход последнего из которых соединен с входом установки в 1 триггера и первым входом второго элемента И, выход последнего из которых соединен со счетным входом счетчика, выход первого разряда которого сое5 динен с первым входом третьего элемента И, выход которого соединен с первым входом первого.элемента ИЛИ, выход которого соединен с первым управляющим входом третьего выходного коммутатора, второйуп- рэвляющий вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом второго разряда счетчика, вход

5 обнуления которого и вход установки в О триггера соединены с выходом первого элемента И, вторые входы первого и второго элементов ИЛИ соединены с выходами соответственно первого и второго элементов

0 И группы, первые входы элементов И которой соединены с инверсным выходом триггера, прямой выход которого соединен с вторыми входами второго, третьего и четвертого элементов И, пятая группа выходов регистра команд соединен с вторыми входами элементов И группы, выходы третьего и четвертого элементов И которой соединены соответственно с первым и вторым управляющими входами первого выходного коммутатора, первый и второй управляющие

0

5

входы второго коммутатора соединены с выходами соответственно пятого и шестого элементов И группы, прямой вход элемента

запрета соединен с информационным входом регистра команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1443000A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| Ячейка однородной вычислительной среды | 1977 |

|

SU691846A1 |

| ПРОЦЕССОР ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2000 |

|

RU2180969C1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| Ячейка однородной вычислительной среды | 1987 |

|

SU1594519A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве вычислительной ячейки (ВЯ) однородной вычислительной структуры (ОВС), ориентированной на цифровую обработку сигналов, объединение и распределение информации между различными абонентами. Целью изобретения является расширение функциональных возможностей ВЯ. Ячейка содержит два входных коммутатора, три выходных коммутатора, коммутатор транзита, арифметико- логический блок, регистр команд, триггер, счетчик, группу элементов И, два элемента ИЛИ, четыре элемента И и элемент запрета. Ячейка позволяет работать в трех режимах: записи команд, выпопнения команд в арифметико-логическом блоке и автономного управления выходного коммутатора, что позволяет строить на основе таких ячеек вычислительные структуры с распределением потоков данных без дополнительного перепрограммирования ячеек вычислительной структуры, 1 ил. ел

| Авторское свидетельство СССР № 684986, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Однородные вычислительные структуры в системах связи / Под ред, А.А.Алексеева | |||

| Д.; ВАС, 1987, | |||

Авторы

Даты

1993-02-28—Публикация

1990-02-28—Подача