Изобретение относится к вычислительной технике и может быть использовано в специализированных системах цифровой обработки информации.

Целью изобретения является расширение функциональных возможностей за счет вычисления всех собственных значений и соответствующих или собственных векторов матрицы.

Цель решается путем введения архитектурных решений и технических средств реализации, обеспечивающих решение полной проблемы собственных значений. Для этого в устройство введена третья матрица - матрица резисторов и (Н+1)-й вычислительный блок с соответствующими связями, а также особые архитектурные решения блоков памяти и вычислительных блоков первой и второй матриц.

Сущность изобретения состоит в том, что для расширения функциональной возможности устройства введение (N+1)-ro вычислительного блока позволяет вычислять Е нормы векторов и производить операции исчерпывания матриц. Кроме того, введенная матрица регистров обеспечивает возможность такой организации вычислительного процесса, при котором матрицы обрабатываются в конвейерном режиме с высокой эффективностью использования вычислительного ресурса,

Изобретение иллюстрируется функциональной схемой (фиг.1) конкретного примера реализации; на фиг. 2,3 и 4 представлены функциональные схемы блока памяти, i-ro и (N+1)-ro вычислительных блоков соответственно.

Устройство по фиг.1 содержит информационный вход 1, матрицу 2 из N блоков 3 памяти, матрицу 4 из N вычислительных блоковб, матрицу 6 из N регистров, (М+Т)-й вычислительный блок 8 и информационные выходы 9 и 10. Причем первый информационный выход j-ro блока 3 памяти (, N-1)

00 О О

о

ГчЭ

подключен к первому информационному входу (j+fyro блока 3 памяти, первый и второй информационные выходы j-ro вычисли- тельного блока 5 подключены соответственно к первому и второму информационным входам (j+1)-ro вычислительного блока 5, вторые информационные вход и выход i-го (, М блока 3 памяти подключены соответственно к третьим выходу и входу i-ro вычислительного блока 5, первый информационный вход первого блока 3 памяти является информационным входом 1 устройства, первый и второй информационные входы первого вычислительного блока 5 подключены соответственно к первому и второму информационным выходам (N+1)-ro вычислительного блока 8, третий и четвертый информационные выходы которого являются соответственно первым 9 и вторым 10 выходами устройства, выход j-ro регист- ра 7 подключен к входу 0+1)го регистра 7, входу управления записью и чтением j-ro блока 3 памяти и первому настроечному входу j-ro вычислительного блока 5, выход N-rp регистра 7 подключен к первому на- строечному входу N-ro вычислительного блока 5 и входу управления записью и чтением N-ro блока 3 памяти, вход первого регистра 7 подключен к первому настроечному выходу (N+1)-ro вычислитель- ного блока 8, второй настроечный выход которого подключен к вторым настроечным входам i-x вычислительных блоков, четвертые информационные выходы которых подключены к информационному входу(Ы+1)-го вычислительного блока.

Блок 3 памяти (фиг.З) содержит четыре мультиплексора 12, 13, 16, 17, два узла 14 и 15 памяти DIFO. Причем информационные входы первого и второго узлов памяти под- ключены соответственно к выходам первого и второго мультиплексоров (12 и 13), выходы первого и второго узлов памяти подключены соответственно к первым и вторым информационным входам третьего и четвертого мультиплексоров, выход 20 третьего мультиплексора 16 является первым информационным выходом блока памяти, второй информационный выход 19 которого подключен к выходу четвертого мультиплексора и первым, информационным входам первого и второго мультиплек- соров, обьединенные вторые информационные входы которых являются вторым информационным входом 18 блока памяти, первый информационный вход 11 которого подключен к третьим информационным входам первого и второго мультиплексоров, управляющие входы всех мультиплексоров и синхровходы узлов па

0

5

0 5 0 5

0 5

5

0

мяти подключены к входу 21 управления записью и чтением блока памяти.

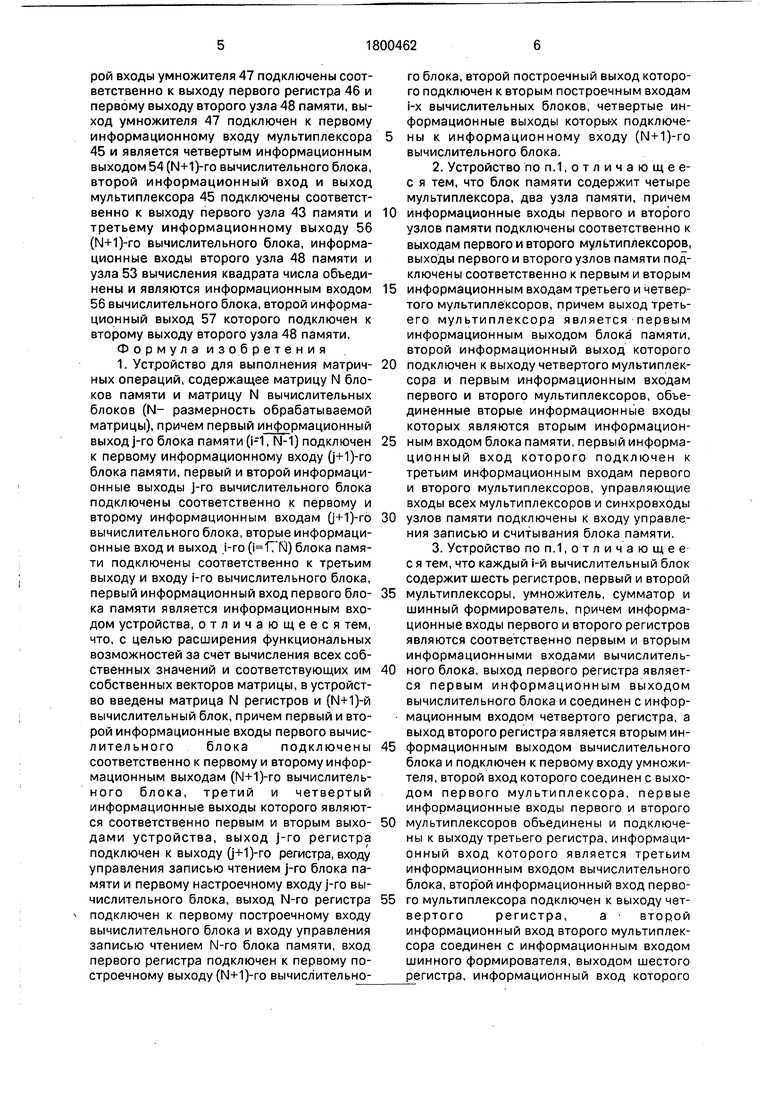

Устройство (фиг.З) i-ro вычислительного блок состоит из шести регистров 27, 28, 29, 31, 36, 35, первого и второго мультиплексоров 30 и 33, умножителя 32, сумматора 34 и шинного формирователя 37. Причем информационные входы первого и второго регистров являются соответственно первым 23 и вторым 24 информационными входами вычислительного блока, выход первого регистра 27 является первым информационным выходом 38 вычислительного блока и соединен с информационным входом четвертого регистра 31, выход второго регистра 28 является вторым информационным выходом 39 вычислительного блока и подключен к первому входу умножителя 32, второй вход которого соединен с выходом первого мультиплексора 30, первые информационные входы первого 30 и второго 33 мультиплексоров объединены и подключены к выходу третьего регистра 29, информационный вход которого является третьим информационным входом 25 вычислительного блока, второй информационный вход первого мультиплексора 30 подключен к выходу четвертого регистра 31, второй информационный вход второго мультиплексора 33 соединен с информационным входом шинного формирователя 37 и выходом шестого регистра 35, информационный вход которого соединен с информационным входом пятого регистра 36 и выходом сумматора 34, первый и второй входы которого подключены соответственно к выходам второго мультиплексора 33 и умножителя 32, выход пятого регистра 36 является третьим выходом 40 вычислительного блока, четвертым выходом 41 которого является выход шинного .формирователя 37, настроечный вход вычислительного блока подключен к управляющим входам первого 30 и второго 33 мультиплексорови входам 26 управления шинного формирователя, синхровходам всех регистров, второй настроечный вход 42 вычислительного блока подключен к входу управления чтением первого регистра 27,

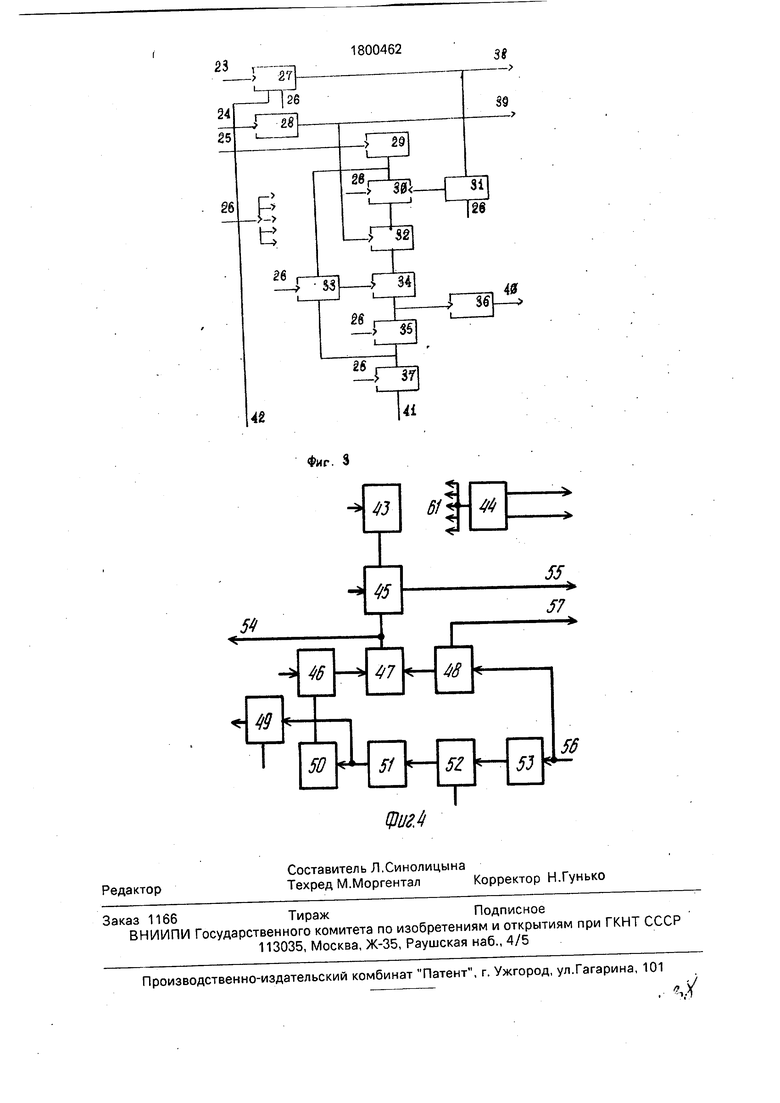

Вычислительный блок (фиг.4) содержит узлы вычисления квадрата 53, квадратного корня 51 и обратной величины 50 числа, накапливающий сумматор 52, два регистра 46, 49, умножитель 47, мультиплексор 45, два узла 43, 48 памяти и блок 44 микропрограммного управления. Причем узел 53 вычисления квадрата числа, накапливающий сумматор52, узел 51 вычисления квадратного корня числа, узел 50 вычисления обратной величины числа и первый регистр 46 срединены последовательно, первый и второй входы умножителя 47 подключены соответственно к выходу первого регистра 46 и первому выходу второго узла 48 памяти, выход умножителя 47 подключен к первому информационному входу мультиплексора 45 и является четвертым информационным выходом 54 (N+1)-ro вычислительного блока, второй информационный вход и выход мультиплексора 45 подключены соответственно к выходу первого узла 43 памяти и третьему информационному выходу 56 (N+1)-ro вычислительного блока, информационные входы второго узла 48 памяти и узла 53 вычисления квадрата числа объединены и являются информационным входом 56 вычислительного блока, второй информационный выход 57 которого подключен к второму выходу второго узла 48 памяти. Формула изобретения 1. Устройство для выполнения матричных операций, содержащее матрицу N блоков памяти и матрицу N вычислительных блоков (N- размерность обрабатываемой матрицы), причем первый информационный выход j-ro блока памяти (И, N-1) подключен к первому информационному входу (j+fyro блока памяти, первый и второй информационные выходы j-ro вычислительного блока подключены соответственно к первому и второму информационным входам (j+1)-ro вычислительного блока, вторые информационные вход и выход j-ro ( N) блока памяти подключены соответственно к третьим выходу и входу i-ro вычислительного блока, первый информационный вход первого блока памяти является информационным входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычисления всех собственных значений и соответствующих им собственных векторов матрицы, в устройство введены матрица N регистров и (N+1)-u вычислительный блок, причем первый и второй информационные входы первого вычислительного блока подключены соответственно к первому и второму информационным выходам (N+1)-ro вычислительного блока, третий и четвертый информационные выходы которого являются соответственно первым и вторым выходами устройства, выход j-ro регистра подключен к выходу (j+1)-ro регистра, входу управления записью чтением j-ro блока памяти и первому настроечному входу j-ro вычислительного блока, выход N-ro регистра подключен к первому построечному входу вычислительного блока и входу управления записью чтением N-ro блока памяти, вход первого регистра подключен к первому построечному выходу (N+1)-ro вычислительного блока, второй построечный выход которого подключен к вторым построечным входам i-x вычислительных блоков, четвертые информационные выходы которых подключе- ны к информационному входу (N+1)-ro вычислительного блока.

2. Устройство по п.1,отличающее- с я тем, что блок памяти содержит четыре мультиплексора, два узла памяти, причем

0 информационные входы первого и второго узлов памяти подключены соответственно к выходам первого и второго мультиплексоров, выходы первого и второго узлов памяти подключены соответственно к первым и вторым

5 информационным входам третьего и четвертого мультиплексоров, причем выход третьего мультиплексора является первым информационным выходом блока памяти, второй информационный выход которого

0 подключен к выходу четвертого мультиплексора и первым информационным входам первого и второго мультиплексоров, объединенные вторые информационные входы которых являются вторым информацион5 ным входом блока памяти, первый информа- ционный вход которого подключен к третьим информационным входам первого и второго мультиплексоров, управляющие входы всех мультиплексоров и синхровходы

0 узлов памяти подключены к входу управления записью и считывания блока памяти.

3. Устройство по п.1, о т л и ч а ю щ е е с я тем, что каждый i-й вычислительный блок содержит шесть регистров, первый и второй

5 мультиплексоры, умножитель, сумматор и шинный формирователь, причем информационные входы первого и второго регистров являются соответственно первым и вторым информационными входами вычислитель0 ного блока, выход первого регистра является первым информационным выходом вычислительного блока и соединен с инфор- мационным входом четвертого регистра, а выход второго регистра является вторым ин5 формационным выходом вычислительного блока и подключен к первому входу умножителя, второй вход которого соединен с выходом первого мультиплексора, первые информационные входы первого и второго

0 мультиплексоров объединены и подключены к выходу третьего регистра, информационный вход которого является третьим информационным входом вычислительного блока, втор ой информационный вход перво5 го мультиплексора подключен к выходу четвертого регистра, а второй информационный вход второго мультиплексора соединен с информационным входом шинного формирователя, выходом шестого регистра, информационный вход которого

соединен с информационным входом пятого регистра и выходом сумматора, первый и второй входы которого подключены соответственно к выходам второго мультиплексора и умножителя, выход пятого регистра является третьим информационным выходом вычислительного блока, четвертым выходом которого является выход шинного формирователя, построечный вход вычислительного блока подключен к управляющим входам первого и второго мультиплексоров и входом управления шинного формирователя, синхровходам всех регистров, второй построечный вход вычислительного блока подключен к входу управления чтением первого регистра.

4. Устройство поп.1,отличающее- с я тем, что (N+lj-й вычислительный блок содержит узлы вычисления квадрата, квадратного корня и обратной величины числа, накапливающий сумматор, два регистра, умножитель, мультиплексор, два узла памяти и блок микропрограммного управления, причем узел вычисления квадрата числа, накапливающий сумматор, узел вычисления

квадратного корня, узел вычисления обратной величины числа и первый регистр соединены последовательно, первый и второй входы умножителя подключены соответственно к выходу первого регистра и первому выходу второго узла памяти, выход умножителя подключен к первому информационному входу мультиплексора и является четвертым информационным выходом

(N+1)-ro вычислительного блока, первый информационный выход которого подключен к выходу второго регистра, информационный вход которого подключен к выходу узла вычисления квадратного корня, второй информационный вход и выход мультиплексора подключены соответственно к выходу первого узла памяти и третьему информационному выходу (N+1)-ro вычислительного блока, информационные входы второго узла

памяти и узла вычисления квадрата числа объединены и являются информационным входом (N+1)-ro вычислительного блока, второй информационный выход которого подключен к второму выходу второго узла

памяти.

Производственно-издательский комбинат Патент, г. Ужгород, ул.Гагарина, 101

.

1

. чУ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обращения матриц | 1990 |

|

SU1778762A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1737461A1 |

| Устройство для вычисления коэффициентов нерекурсивных полосовых фильтров | 1988 |

|

SU1647587A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для решения систем алгебраических уравнений | 1984 |

|

SU1325507A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1737462A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ МАТРИЦ | 1991 |

|

RU2037200C1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1325508A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных системах цифровой обработки информации, основанной на решении полной проблемы собственных значений. Цель изобретения - расширение функциональных возможностей за счет вычисления всех собственных значений и соответствующих им собственных векторов матрицы. Цель достигается тем, что в устройство, содержащее матрицу N. вычислительных блоков, матрицу N блоков памяти, введены матрица регистров и (Ы+1)-й вычислительный блок, позволяющие организовать вычислительный процесс, обеспечивающий решение полной проблемы собственных значений степенным методом. 3 з.п. ф-лы, 4 ил.

| Кухарев Г.А | |||

| и др | |||

| Систолические процессоры для обработки сигналов | |||

| Минск: Беларусь, 1988, с | |||

| Солесос | 1922 |

|

SU29A1 |

| Устройство для выполнения матричных операций | 1986 |

|

SU1388897A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-03-07—Публикация

1989-12-05—Подача