(Л

С

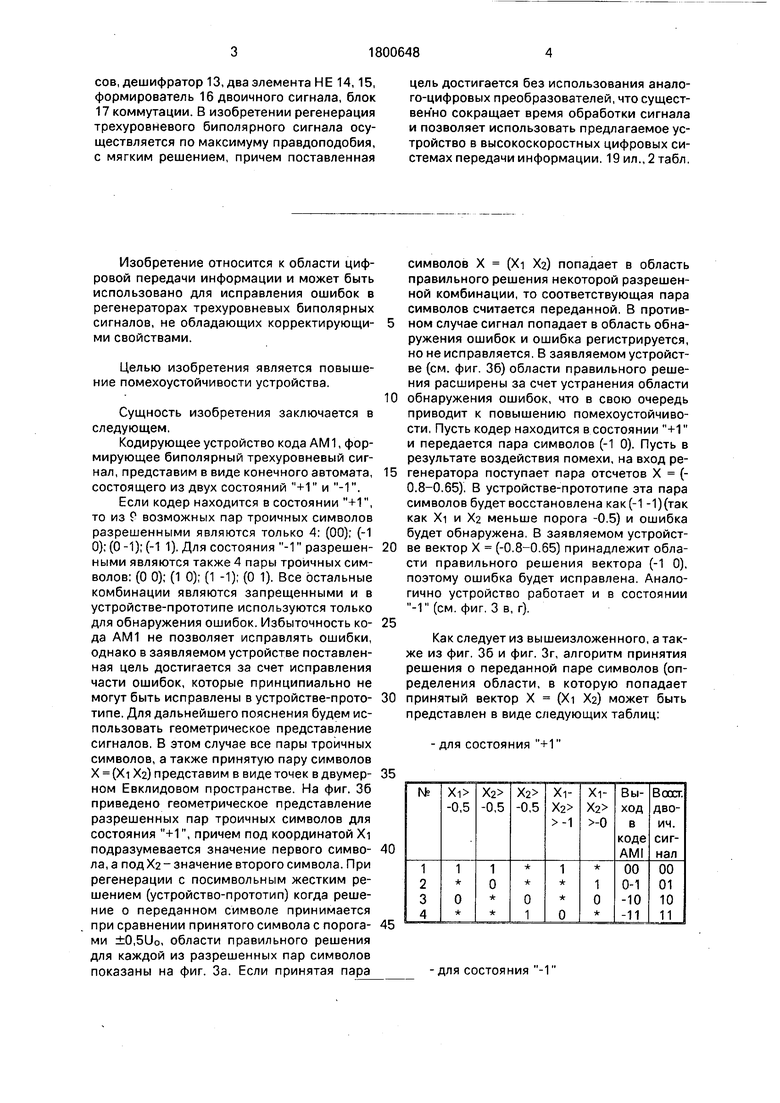

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| ВЕДОМСТВЕННАЯ СИСТЕМА ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА | 2016 |

|

RU2650191C1 |

| Устройство конференц-связи для систем с дельта-модуляцией | 1986 |

|

SU1418926A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| СПОСОБ ВЕДЕНИЯ ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА В ВЕДОМСТВЕННОЙ СИСТЕМЕ СВЯЗИ | 2016 |

|

RU2663200C2 |

| Декодирующее устройство | 1990 |

|

SU1783612A1 |

| Устройство для ввода информации | 1988 |

|

SU1513438A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

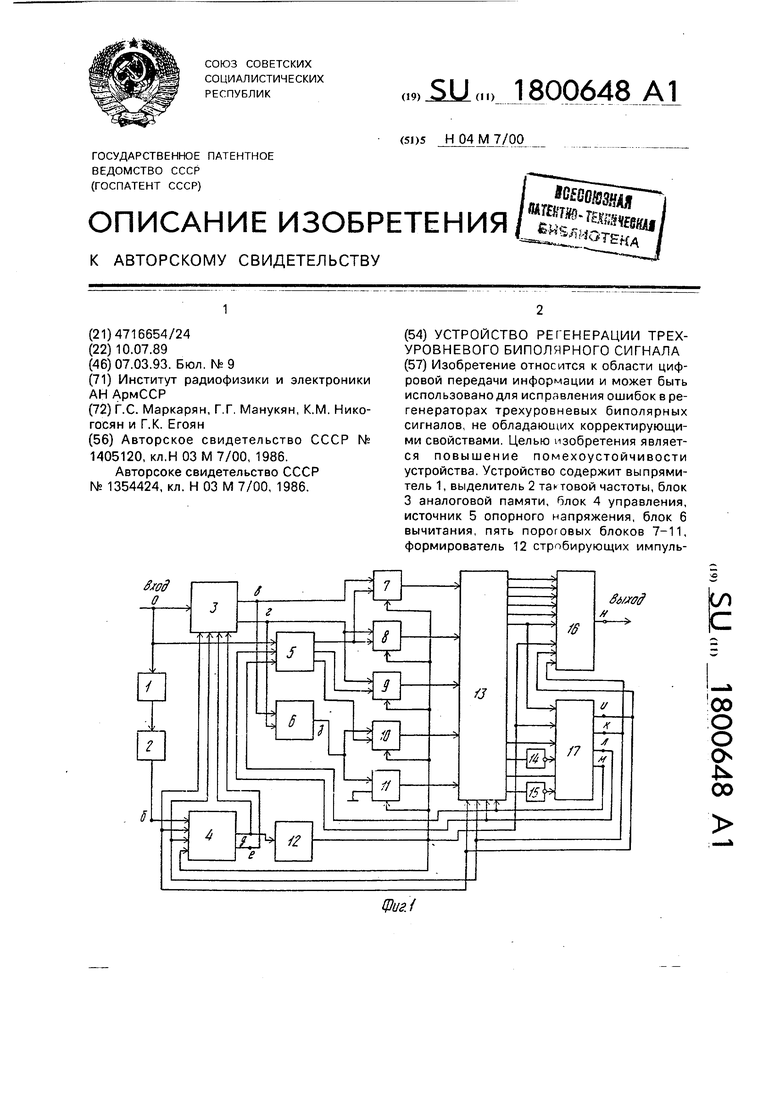

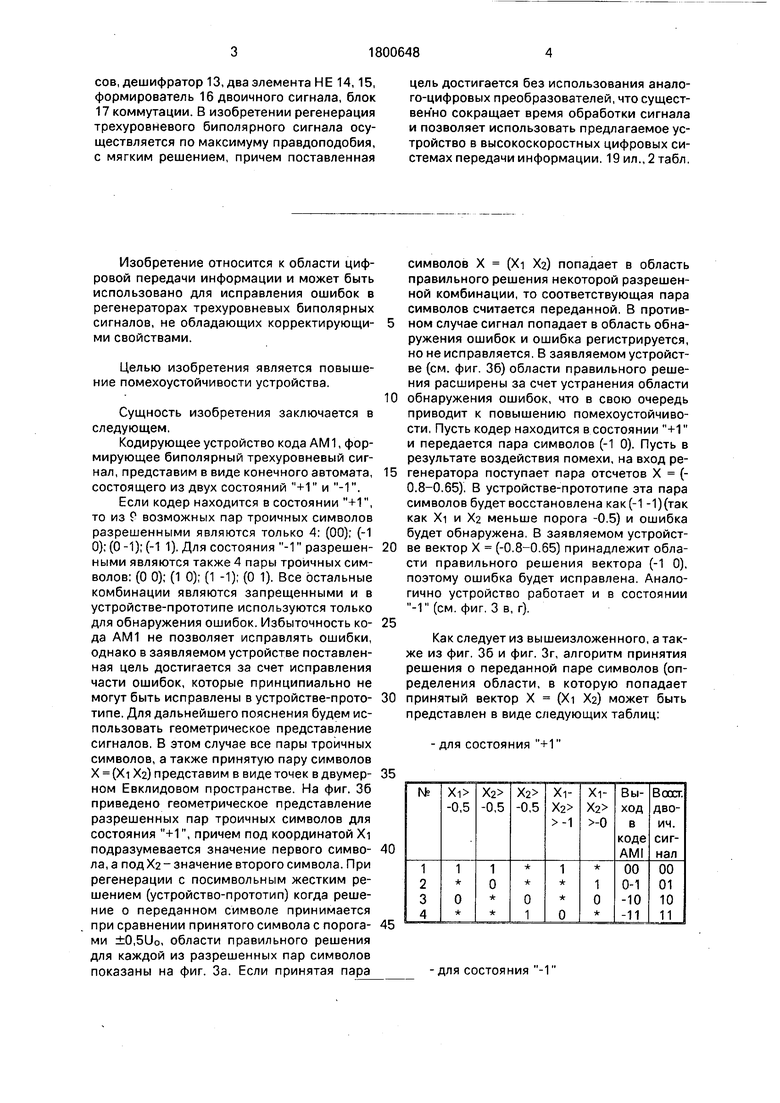

Изобретение относится к области цифровой передачи информации и может быть использовано для исправления ошибок в регенераторах трехуровневых биполярных сигналов, не обладающих корректирующими свойствами. Целью изобретения является повышение помехоустойчивости устройства. Устройство содержит выпрямитель 1, выделитель 2 тактовой частоты, блок 3 аналоговой памяти, блок 4 управления, источник 5 опорного напряжения, блок 6 вычитания, пять пороговых блоков 7-11, формирователь 12 стробирующих импуль

00

о о о

00

сов, дешифратор 13, два элемента НЕ 14,15, формирователь 16 двоичного сигнала, блок 17 коммутации. В изобретении регенерация трехуровневого биполярного сигнала осуществляется по максимуму правдоподобия, с мягким решением, причем поставленная

Изобретение относится к области цифровой передачи информации и может быть использовано для исправления ошибок в регенераторах трехуровневых биполярных сигналов, не обладающих корректирующими свойствами.

Целью изобретения является повышение помехоустойчивости устройства.

Сущность изобретения заключается в следующем.

Кодирующее устройство кода AM 1, формирующее биполярный трехуровневый сигнал, представим в виде конечного автомата, состоящего из двух состояний +1 и -1.

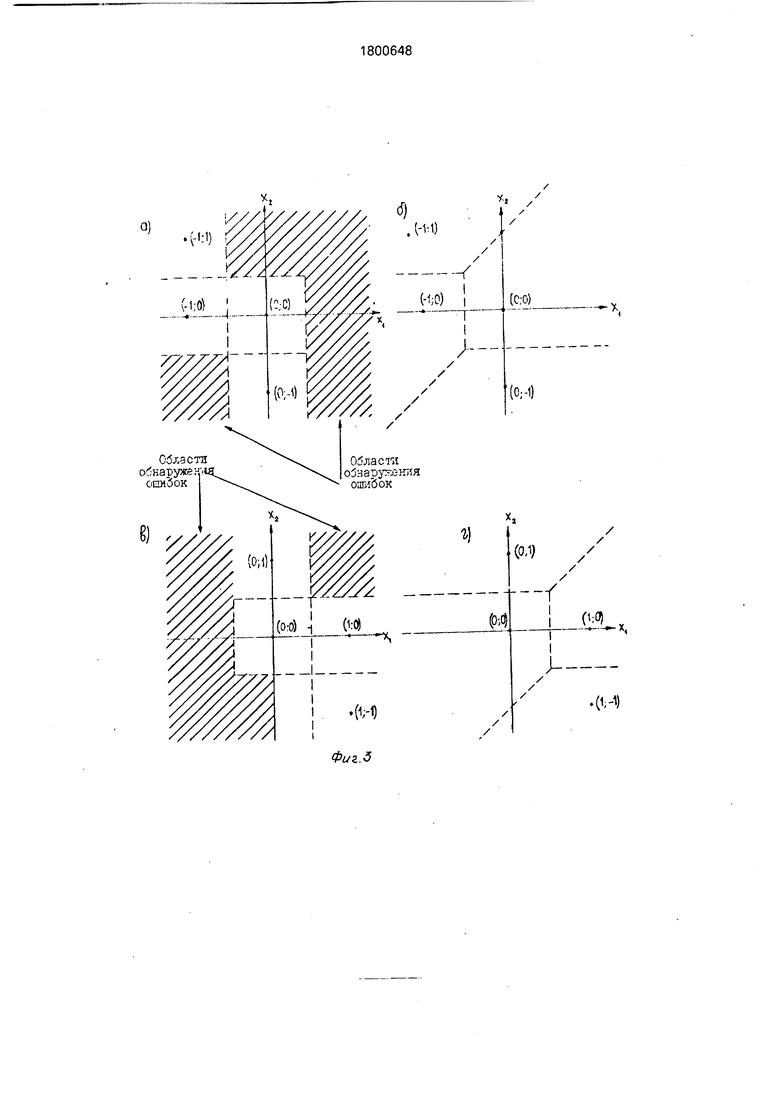

Если кодер находится в состоянии +1, то из возможных пар троичных символов разрешенными являются только 4: (00); (-1 0);(0-1);(-1 1). Для состояния -1 разрешен- ными являются также 4 пары троичных символов: (0 0); (1 0); (1 -1); (0 1). Все остальные комбинации являются запрещенными и в устройстве-прототипе используются только для обнаружения ошибок. Избыточность ко- да АМ1 не позволяет исправлять ошибки, однако в заявляемом устройстве поставленная цель достигается за счет исправления части ошибок, которые принципиально не могут быть исправлены в устройстве-прото- типе. Для дальнейшего пояснения будем использовать геометрическое представление сигналов. В этом случае все пары троичных символов, а также принятую пару символов X (XiX2) представим в виде точек вдвумер- ном Евклидовом пространстве. На фиг. 36 приведено геометрическое представление разрешенных пар троичных символов для состояния +1, причем под координатой Xi подразумевается значение первого симво- ла,а под Х2 значение второго символа. При регенерации с посимвольным жестким решением (устройство-прототип) когда решение о переданном символе принимается при сравнении принятого символа с порога- ми ±0,5Uo, области правильного решения для каждой из разрешенных пар символов показаны на фиг. За. Если принятая пара

цель достигается без использования анало- го-цифровых преобразователей, что существенно сокращает время обработки сигнала и позволяет использовать предлагаемое устройство в высокоскоростных цифровых системах передачи информации. 19 ил., 2 табл.

символов X (Xi X2) попадает в область правильного решения некоторой разрешенной комбинации, то соответствующая пара символов считается переданной. В противном случае сигнал попадает в область обнаружения ошибок и ошибка регистрируется, но не исправляется. В заявляемом устройстве (см. фиг. 36) области правильного решения расширены за счет устранения области обнаружения ошибок, что в свою очередь приводит к повышению помехоустойчивости, Пусть кодер находится в состоянии +1 и передается пара символов (-1 0). Пусть в результате воздействия помехи, на вход регенератора поступает пара отсчетов X (- 0.8-0.65). В устройстве-прототипе эта пара символов будет восстановлена как(-1 -1)(так как Xi и 2 меньше порога -0.5) и ошибка будет обнаружена, В заявляемом устройстве вектор X (-0.8-0.65) принадлежит области правильного решения вектора (-1 0), поэтому ошибка будет исправлена. Аналогично устройство работает и в состоянии -1 (см. фиг. 3 в, г).

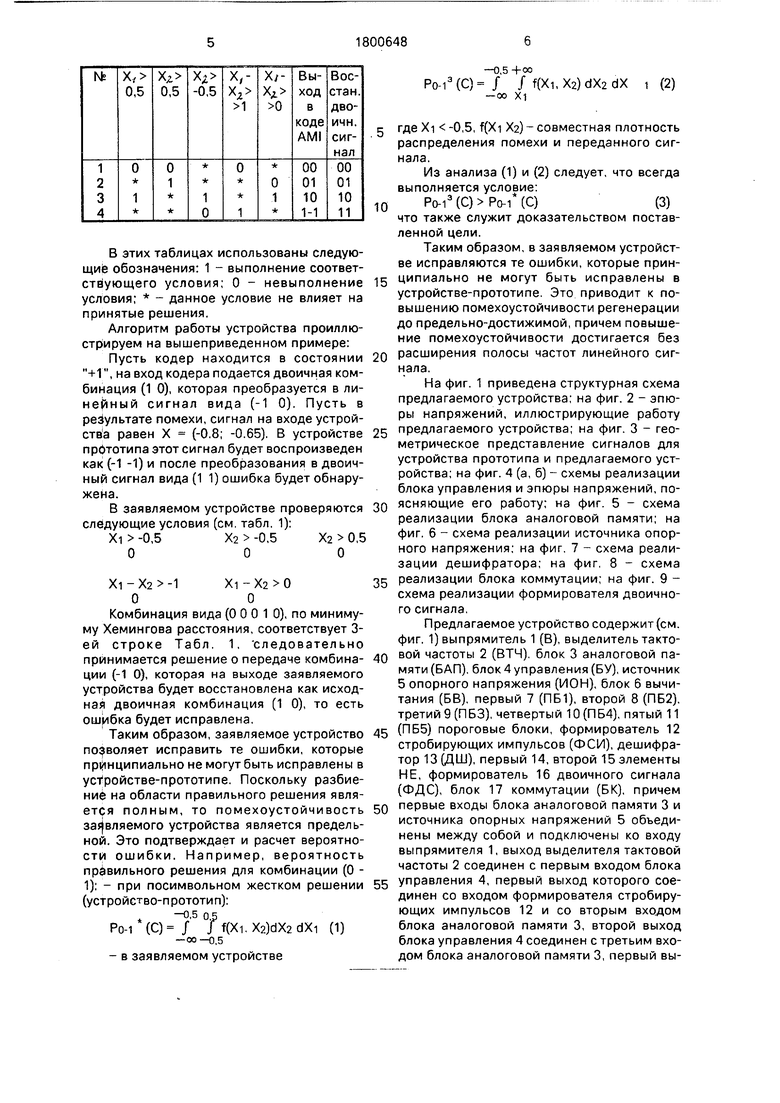

Как следует из вышеизложенного, а также из фиг. 36 и фиг. Зг, алгоритм принятия решения о переданной паре символов (определения области, в которую попадает принятый вектор X (Xi Ха) может быть представлен в виде следующих таблиц:

- для состояния +1

-для состояния -1

В этих таблицах использованы следующие обозначения: 1 - выполнение соответствующего условия; 0 - невыполнение условия; - данное условие не влияет на принятые решения.

Алгоритм работы устройства проиллюстрируем на вышеприведенном примере:

Пусть кодер находится в состоянии +Т, на вход кодера подается двоичная комбинация (1 0), которая преобразуется в линейный сигнал вида (-1 0). Пусть в результате помехи, сигнал на входе устройства равен X (-0.8; -0.65). В устройстве прйтотипа этот сигнал будет воспроизведен как (-1 -1) и после преобразования в двоичный сигнал вида (1 1) ошибка будет обнаружена.

В заявляемом устройстве проверяются следующие условия (см. табл. 1):

Xi -0,5Х2 -0,5 Х2 0,5 О 00

Xi-X2 -1Xi-X2 0 О О

Комбинация вида (0001 0), по минимуму Хемингова расстояния, соответствует 3- ей строке Табл. 1, следовательно принимается решение о передаче комбина- ции (-1 0), которая на выходе заявляемого устройства будет восстановлена как исходная двоичная комбинация (1 0), то есть ошибка будет исправлена.

Таким образом, заявляемое устройство позволяет исправить те ошибки, которые принципиально не могут быть исправлены в устройстве-прототипе. Поскольку разбиение на области правильного решения является полным, то помехоустойчивость заявляемого устройства является предельной. Это подтверждает и расчет вероятности ошибки. Например, вероятность правильного решения для комбинации (0 - 1); - при посимвольном жестком решении (устройство-прототип):

Ро-1(С) / f(Xi,X2)dX2dXi (1)

-00-0,5

- в заявляемом устройстве

-0,5+оо

Ро-13(С) / / f(Xi,X2)dX2dX

- 00 Х1

1 (2)

0

5

0

5

0

5

0

5 0 5

где Хч -0,5, f(Xi X2) - совместная плотность распределения помехи и переданного сигнала.

Из анализа (1) и (2) следует, что всегда выполняется условие:

Ро-13 (С) PoY (С)(3) что также служит доказательством поставленной цели.

Таким образом, в заявляемом устройстве исправляются те ошибки, которые принципиально не могут быть исправлены в устройстве-прототипе. Это приводит к повышению помехоустойчивости регенерации до предельно-достижимой, причем повышение помехоустойчивости достигается без расширения полосы частот линейного сигнала.

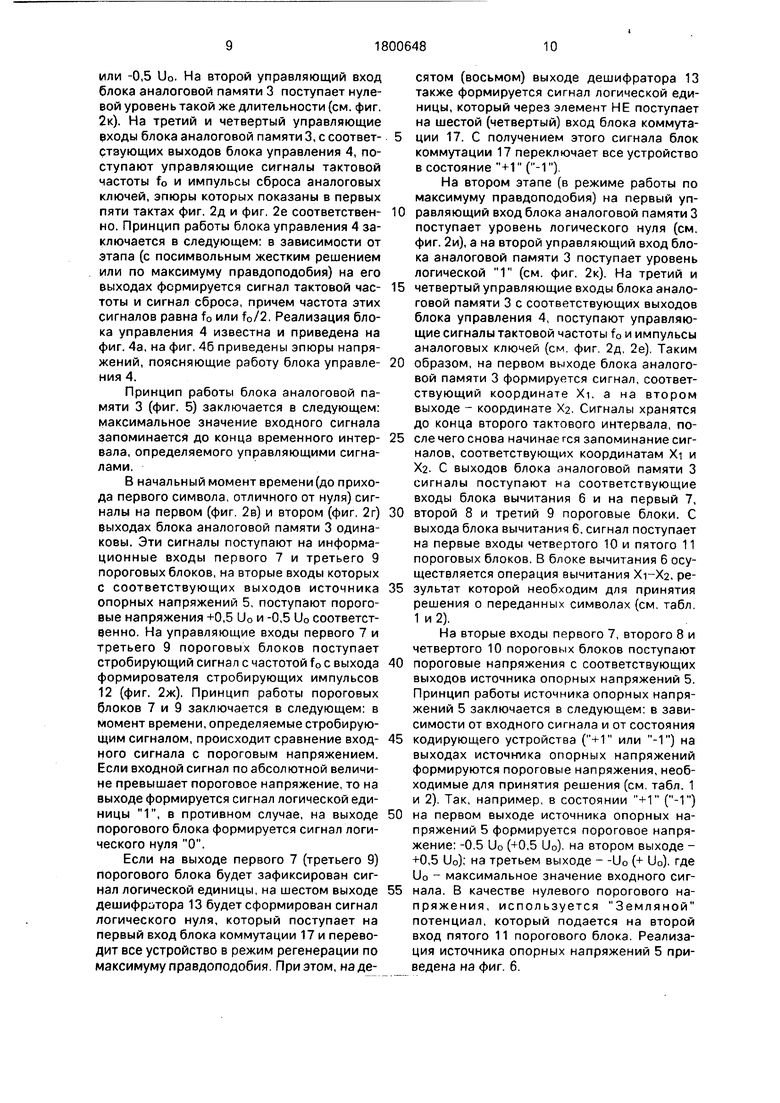

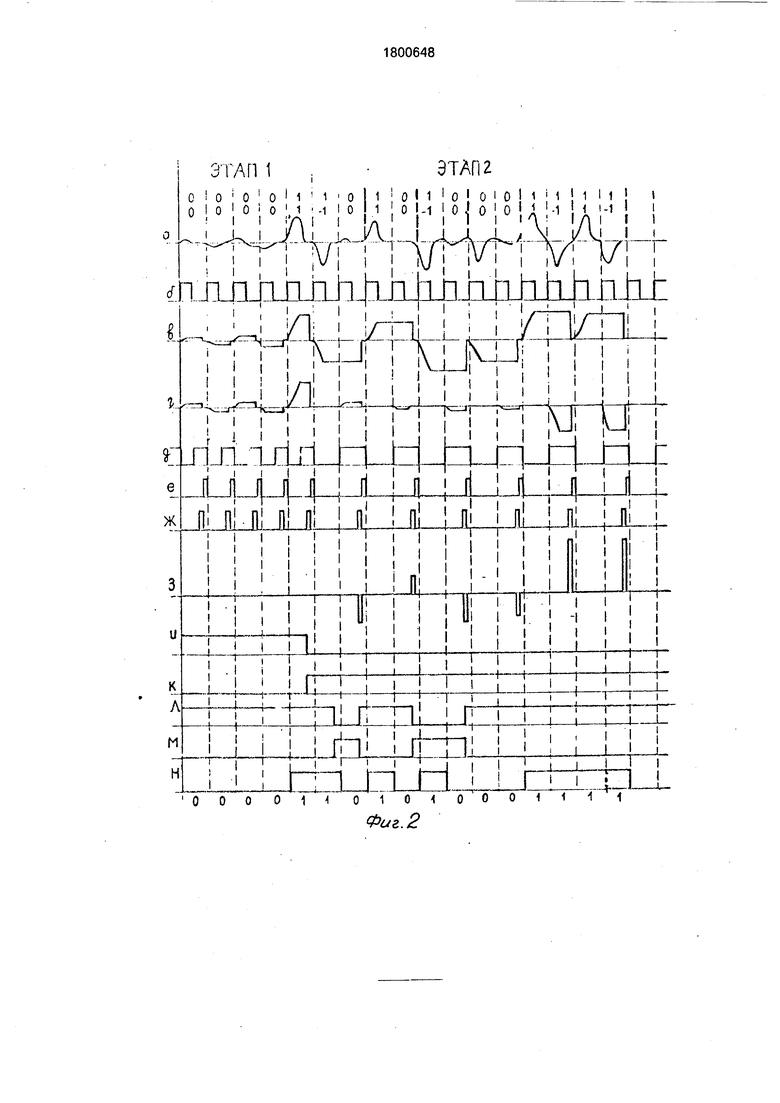

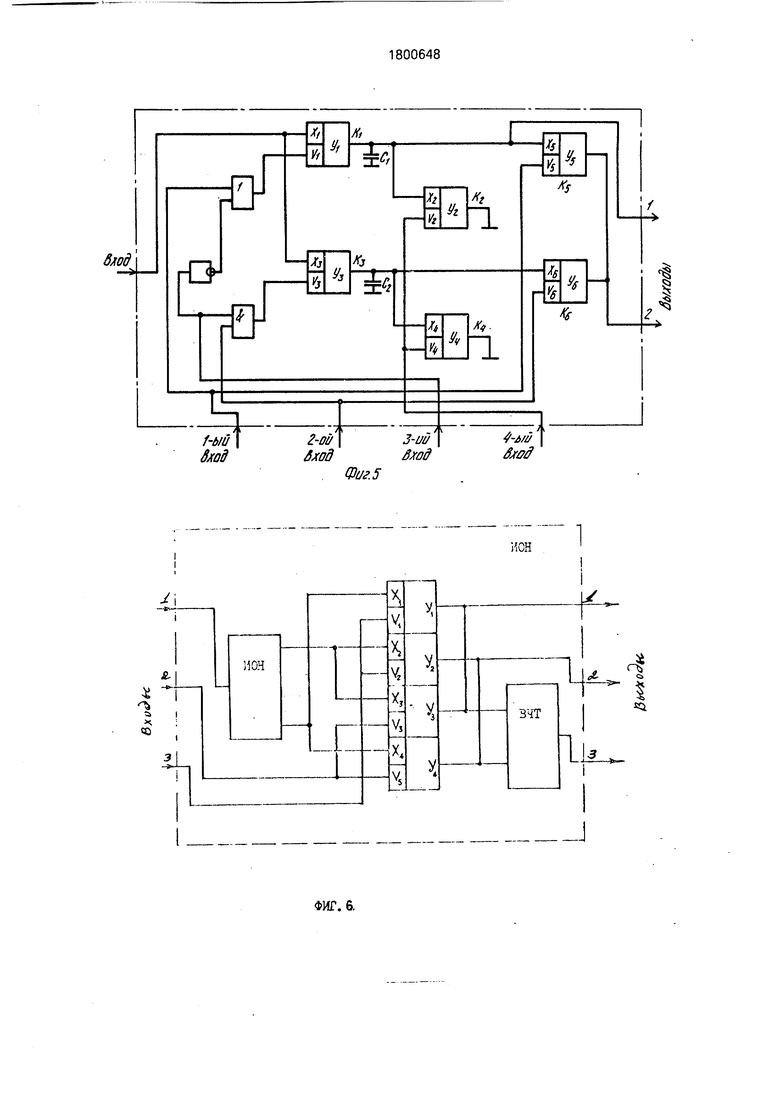

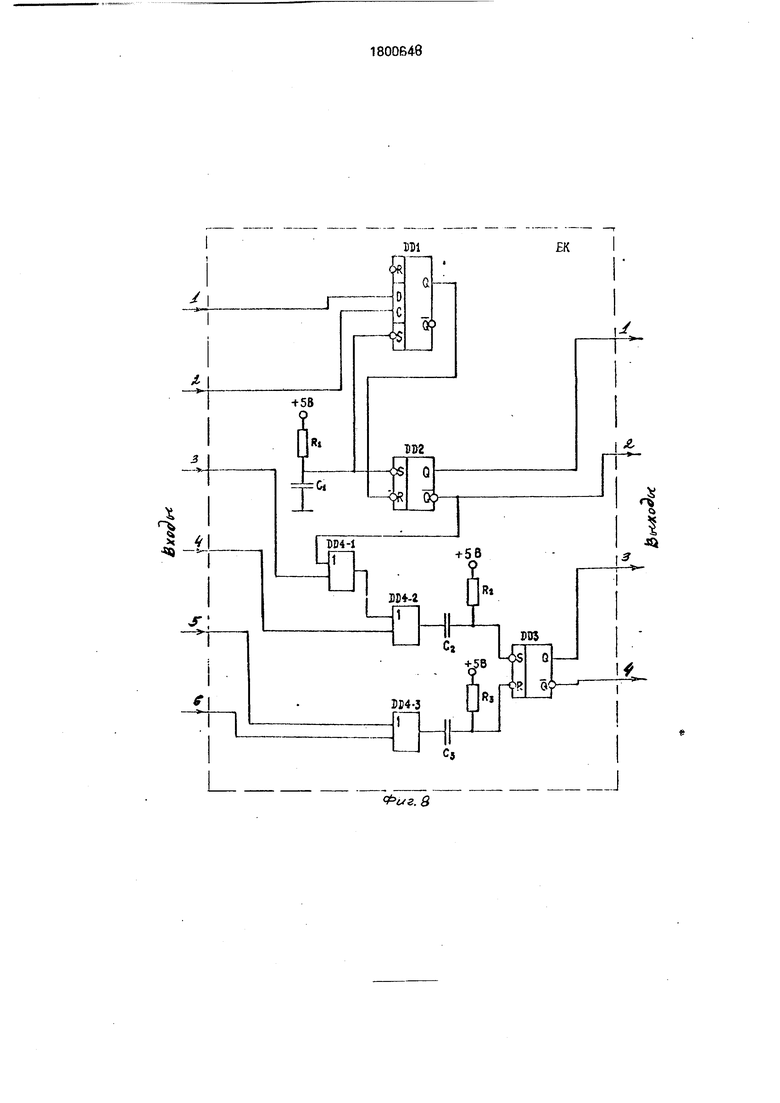

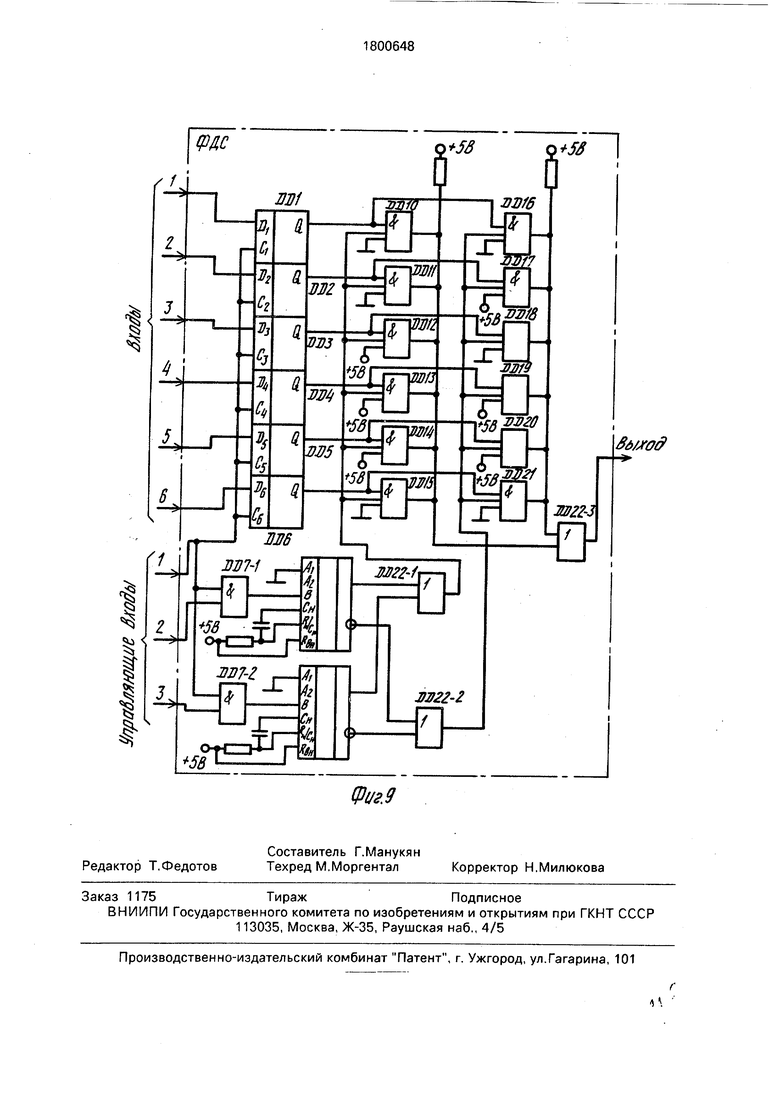

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - эпюры напряжений, иллюстрирующие работу предлагаемого устройства; на фиг. 3 - геометрическое представление сигналов для устройства прототипа и предлагаемого устройства; на фиг. 4 (а, б) - схемы реализации блока управления и эпюры напряжений, поясняющие его работу; на фиг. 5 - схема реализации блока аналоговой памяти; на фиг. 6 - схема реализации источника опорного напряжения; на фиг. 7 - схема реализации дешифратора; на фиг. 8 - схема реализации блока коммутации; на фиг. 9 - схема реализации формирователя двоичного сигнала.

Предлагаемое устройство содержит (см. фиг. 1) выпрямитель 1 (В), выделитель тактовой частоты 2 (ВТЧ). блок 3 аналоговой памяти (БАП), блок 4 управления (БУ), источник 5 опорного напряжения (ИОН), блок 6 вычитания (БВ), первый 7 (ПБ1), второй 8 (ПБ2), третий 9 (ПБЗ), четвертый 10(ПБ4), пятый 11 (ПБ5) пороговые блоки, формирователь 12 стробирующих импульсов (ФСИ), дешифратор 13 (ДШ), первый 14, второй 15 элементы НЕ, формирователь 16 двоичного сигнала (ФДС), блок 17 коммутации (БК), причем первые входы блока аналоговой памяти 3 и источника опорных напряжений 5 объединены между собой и подключены ко входу выпрямителя 1, выход выделителя тактовой частоты 2 соединен с первым входом блока управления 4, первый выход которого соединен со входом формирователя стробирующих импульсов 12 и со вторым входом блока аналоговой памяти 3, второй выход блока управления 4 соединен с третьим входом блока аналоговой памяти 3, первый выход которого соединен с первыми входами вычитателя б и третьего порогового блока 9, второй выход блока аналоговой памяти 3 соединен со вторым входом вычитателя 6, первым входом четвертого порогового блока 10, и третьим входом первого порогового блока 7, третий выход источника опорного напряжения 5 соединен со вторыми входами третьего 9 и четвертого 10 пороговых блоков, выход вычитателя 6 подключен к третьему входу второго порогового блока 8 и первому входу пятого порогового блока 11, второй вход которого соединен с шиной лог. О, выходы первого 7, второго 8, третьего 9, четвертого 10, пятого 11 пороговых блоков подключены к соответствующим информационным входам дешифратора 13, первый, второй, третий, четвертый и пятый выходы дешифратора 13 соединены с соответствующими информационными входами формирователя двоичных сигналов 16, шестой выход дешифратора 13 соединен с соответствующим информационным входом формирователя двоичных сигналов 16 и с первым входом блока коммутации 17, седьмой и восьмой выходы дешифратора 13 соединены соответственно со вторым и третьим входами блока коммутации 17, девятый и десятый выходы дешифратора 13 через первый и второй элементы НЕ соединены соответственно с четвертым и пятым входами блока коммутации 17, третьи входы третьего 9, четвертого 10 и пятого 11 пороговых блоков, первый управляющий вход формирователя двоичных сигналов 16 и второй вход блока управления 4 объединены между собой и подключены к выходу формирователя стробирующих импульсов 12, первый выход блока коммутации 17 соединен со вторым управляющим входом формирователя двоичных сигналов 16, первым управляющим входом дешифратора 13, третьим входом блока управления 4 и четвертым входом блока аналоговой памяти 3, второй выход блока коммутации 17 соединен с третьим управляющим входом формирователя двоичных сигналов 16, вторым управляющим входом дешифратора 13, четвертым входом блока управления 4 и пятым входом блока аналоговой памяти 3, третий и четвертый выходы блока коммутации 17 соединены соответственно с третьим и четвертым входами источника опорных напряжений 5, дешифратора 13 и со вторым и третьим входами источника опорных напряжений 5, выход формирователя двоичных 16 сигналов является выходом устройства.

Устройство работает следующим образом. Пусть на передающей стороне передавалась комбинация вида 00001-10001-11-1

(см. фиг. 2) с тактовой частотой f0. Пусть на входе устройства переданной комбинации соответствует сигнал, представленный на фиг. 2а, Для более наглядного представле- ния процесса исправления ошибок в заявляемом устройстве помеха в линейном тракте выбирается такой, что переданный 12-ый символ (О) в устройстве-прототипе будет восстановлен с ошибкой, которая исправля0 ется в заявляемом устройстве.

Работу заявляемого устройства можно разбить на 2 этапа:

а) 1-ый этап (очень короткий) - регенерация с посимвольным жестким решением;

5 б)2-ой этап (основной)- регенерация по максимуму правдоподобия.

Такое разбиение необходимо по той причине, что на приемном конце, в начальный момент времени не известно состояние

0 кодирующего устройства, а следовательно не известно по какому алгоритму (фиг. 36 или фиг. Зг) принимать решение о переданных символах. Поэтому на первом этапе, до поступления первого символа, отличного от

5 нуля (+1 или -1) устройство работает как обычный регенератор с посимвольным жестким решением. После прихода первого значащего символа (+1 или -1), устройство устанавливается в соответствующее состоя0 ние и начинает работать по максимуму правдоподобия (в соответствии с Табл. 1 или Табл. 2). ,

Входной сигнал (см. фиг. 2а) поступает на вход блока аналоговой памяти 3 и, через

5 выпрямитель 1, на вход выделителя тактовой частоты 2, на выходе которого формируется сигнал с тактовой частотой f0, представленный на фиг. 26. Принцип работы и реализация выпрямителя 1 и выделите0 ля тактовой частоты 2 известны и являются такими же, как в устройстве-прототипе.

Входной сигнал (см. фиг. 2а) поступает на информационный вход источника опорных напряжений 5, принцип работы которо5 го известен и заключается в следующем: в зависимости от входного сигнала, на его входах формируются пороговые напряжения, необходимые для принятия решения о переданных символах.

0Поскольку в начальный момент времени неизвестно состояние кодирующего устройства (+1 или -1), то до прихода символа отличного от нуля (+1 или -1) устройство работает как обычный регенератор с посим5 вольным жестким решением. В этом случае на первый управляющий вход блока аналоговой памяти 3 поступает единичный уровень (см. фиг. 2и); который длится до тех пор, пока входной символ не превысит по абсолютной величине один из порогов: +0,5 Uo

или -0,5 U0. На второй управляющий вход блока аналоговой памяти 3 поступает нулевой уровень такой же длительности (см. фиг. 2к), На третий и четвертый управляющие входы блока аналоговой памяти 3, с соответ- стзующих выходов блока управления 4, поступают управляющие сигналы тактовой частоты f0 и импульсы сброса аналоговых ключей, эпюры которых показаны в первых пяти тактах фиг. 2д и фиг. 2е соответствен- но. Принцип работы блока управления 4 заключается в следующем: в зависимости от этапа (с посимвольным жестким решением или по максимуму правдоподобия) на его выходах формируется сигнал тактовой час- тоты и сигнал сброса, причем частота этих сигналов равна fo или f0/2. Реализация блока управления 4 известна и приведена на фиг. 4а, на фиг. 46 приведены эпюры напряжений, поясняющие работу блока управле- ния 4.

Принцип работы блока аналоговой памяти 3 (фиг. 5) заключается в следующем: максимальное значение входного сигнала запоминается до конца временного интер- вала, определяемого управляющими сигналами.

В начальный момент времени (до прихода первого символа, отличного от нуля) сигналы на первом (фиг. 2в) и втором (фиг. 2г) выходах блока аналоговой памяти 3 одинаковы. Эти сигналы поступают на информационные входы первого 7 и третьего 9 пороговых блоков, на вторые входы которых с соответствующих выходов источника опорных напряжений 5, поступают пороговые напряжения +0,5 U0 и -0,5 U0 соответственно. На управляющие входы первого 7 и третьего 9 пороговых блоков поступает стробирующий сигнал с частотой f0 с выхода формирователя стробирующих импульсов 12 (фиг, 2ж), Принцип работы пороговых блоков 7 и 9 заключается в следующем: в момент времени, определяемые стробирую- щим сигналом, происходит сравнение вход- ного сигнала с пороговым напряжением. Если входной сигнал по абсолютной величине превышает пороговое напряжение, то на выходе формируется сигнал логической единицы 1, в противном случае, на выходе порогового блока формируется сигнал логического нуля О.

Если на выходе первого 7 (третьего 9) порогового блока будет зафиксирован сигнал логической единицы, на шестом выходе дешифратора 13 будет сформирован сигнал логического нуля, который поступает на первый вход блока коммутации 17 и переводит все устройство в режим регенерации по максимуму правдоподобия. При этом, на десятом (восьмом) выходе дешифратора 13 также формируется сигнал логической единицы, который через элемент НЕ поступает на шестой (четвертый) вход блока коммутации 17. С получением этого сигнала блок коммутации 17 переключает все устройство в состояние +1 (-1).

На втором этапе (в режиме работы по максимуму правдоподобия) на первый управляющий вход блока аналоговой памяти 3 поступает уровень логического нуля (см. фиг. 2и), а на второй управляющий вход блока аналоговой памяти 3 поступает уровень логической 1 (см. фиг. 2к). На третий и четвертый управляющие входы блока аналоговой памяти 3 с соответствующих выходов блока управления 4, поступают управляющие сигналы тактовой частоты f0 и импульсы аналоговых ключей (см. фиг. 2д, 2е). Таким образом, на первом выходе блока аналоговой памяти 3 формируется сигнал, соответствующий координате XL а на втором выходе - координате Х2. Сигналы хранятся до конца второго тактового интервала, после чего снова начинав гея запоминание сигналов, соответствующих координатам Xi и Ха. С выходов блока аналоговой памяти 3 сигналы поступают на соответствующие входы блока вычитания 6 и на первый 7, второй 8 и третий 9 пороговые блоки. С выхода блока вычитания 6, сигнал поступает на первые входы четвертого 10 и пятого 11 пороговых блоков. В блоке вычитания 6 осуществляется операция вычитания Xi-X2, результат которой необходим для принятия решения о переданных символах (см. табл. 1 и 2).

На вторые входы первого 7, второго 8 и четвертого 10 пороговых блоков поступают пороговые напряжения с соответствующих выходов источника опорных напряжений 5. Принцип работы источника опорных напряжений 5 заключается в следующем: в зависимости от входного сигнала и от состояния кодирующего устройства (-Н или -1) на выходах источника опорных напряжений формируются пороговые напряжения, необходимые для принятия решения (см. табл. 1 и 2). Так, например, в состоянии +1 (-1) на первом выходе источника опорных напряжений 5 формируется пороговое напряжение: -0,5 Uo (+0,5 Uo). на втором выходе - +0,5 Uo); на третьем выходе - -U0 (+ U0). где Do - максимальное значение входного сигнала. В качестве нулевого порогового напряжения, используется Земляной потенциал, который подается на второй вход пятого 11 порогового блока. Реализация источника опорных напряжений 5 приведена на фиг. 6.

Установка состояния кодирующего устройства (+1 или -1) осуществляется по управляющим сигналам, которые поступают на второй и третий входы источника опорных напряжений 5.

В момент времени, определяемые стро- бирующими импульсами (фиг. 2ж), во всех пороговых блоках происходит сравнение входных сигналов (Xi, X2, Xi-Xz) с пороговыми напряжениями. Принцип работы всех пороговых блоков заключается в следующем: если входной сигнал больше порогового напряжения, то на выходе формируется сигнал логической единицы, в противном случае - нуля.

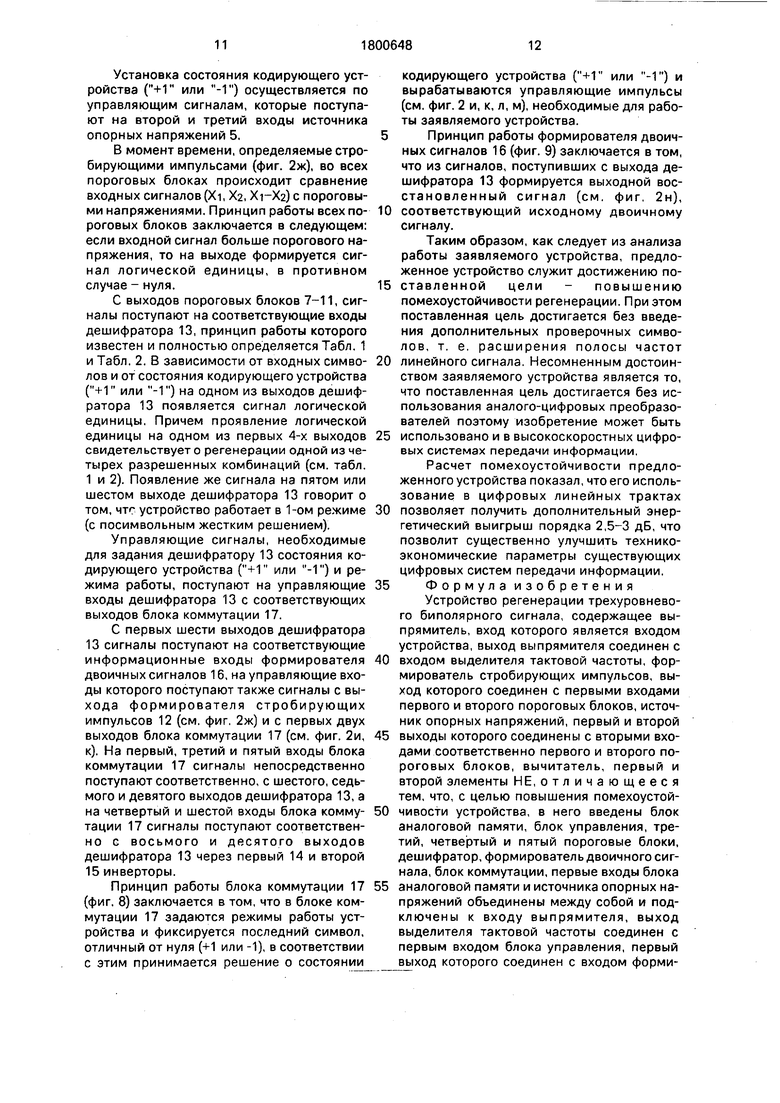

С выходов пороговых блоков 7-11, сигналы поступают на соответствующие входы дешифратора 13, принцип работы которого известен и полностью определяется Табл. 1 и Табл. 2. В зависимости от входных символов и от состояния кодирующего устройства (+1 или -1) на одном из выходов дешифратора 13 появляется сигнал логической единицы. Причем проявление логической единицы на одном из первых 4-х выходов свидетельствует о регенерации одной из четырех разрешенных комбинаций (см. табл. 1 и 2). Появление же сигнала на пятом или шестом выходе дешифратора 13 говорит о том, чтс устройство работает в 1-ом режиме (с посимвольным жестким решением).

Управляющие сигналы, необходимые для задания дешифратору 13 состояния кодирующего устройства (+1 или -1) и режима работы, поступают на управляющие входы дешифратора 13 с соответствующих выходов блока коммутации 17.

С первых шести выходов дешифратора 13 сигналы поступают на соответствующие информационные входы формирователя двоичных сигналов 16, на управляющие входы которого поступают также сигналы с выхода формирователя стробирующих импульсов 12 (см. фиг, 2ж) и с первых двух выходов блока коммутации 17 (см. фиг. 2и, к). На первый, третий и пятый входы блока коммутации 17 сигналы непосредственно поступают соответственно, с шестого, седьмого и девятого выходов дешифратора 13, а на четвертый и шестой входы блока коммутации 17 сигналы поступают соответственно с восьмого и десятого выходов дешифратора 13 через первый 14 и второй 15 инверторы.

Принцип работы блока коммутации 17 (фиг. 8) заключается в том, что в блоке коммутации 17 задаются режимы работы устройства и фиксируется последний символ, отличный от нуля (+1 или -1), в соответствии с этим принимается решение о состоянии

кодирующего устройства (+1 или -1) и вырабатываются управляющие импульсы (см. фиг. 2 и, к, л, м), необходимые для работы заявляемого устройства. Принцип работы формирователя двоичных сигналов 16 (фиг. 9) заключается в том, что из сигналов, поступивших с выхода дешифратора 13 формируется выходной восстановленный сигнал (см. фиг, 2н),

0 соответствующий исходному двоичному сигналу.

Таким образом, как следует из анализа работы заявляемого устройства, предложенное устройство служит достижению по5 ставленной цели - повышению помехоустойчивости регенерации. При этом поставленная цель достигается без введения дополнительных проверочных символов, т. е. расширения полосы частот

0 линейного сигнала. Несомненным достоинством заявляемого устройства является то, что поставленная цель достигается без использования аналого-цифровых преобразователей поэтому изобретение может быть

5 использовано и в высокоскоростных цифровых системах передачи информации.

Расчет помехоустойчивости предложенного устройства показал, что его использование в цифровых линейных трактах

0 позволяет получить дополнительный энергетический выигрыш порядка 2,5-3 дБ, что позволит существенно улучшить технико- экономические параметры существующих цифровых систем передачи информации.

5 Формула изобретения

Устройство регенерации трехуровневого биполярного сигнала, содержащее выпрямитель, вход которого является входом устройства, выход выпрямителя соединен с

0 входом выделителя тактовой частоты, формирователь стробирующих импульсов, выход которого соединен с первыми входами первого и второго пороговых блоков, источник опорных напряжений, первый и второй

5 выходы которого соединены с вторыми входами соответственно первого и второго пороговых блоков, вычитатель, первый и второй элементы НЕ, отличающееся тем, что, с целью повышения помехоустой0 чивости устройства, в него введены блок аналоговой памяти, блок управления, третий, четвертый и пятый пороговые блоки, дешифратор, формирователь двоичного сигнала, блок коммутации, первые входы блока

5 аналоговой памяти и источника опорных напряжений объединены между собой и подключены к входу выпрямителя, выход выделителя тактовой частоты соединен с первым входом блока управления, первый выход которого соединен с входом формирователя стробирующих импульсов и с вторым входом блока аналоговой памяти, второй выход блока управления соединен с третьим входом блока аналоговой памяти, первый выход которого соединен с первыми входами вычитателя и третьего порогового блока, второй выход блока аналоговой памяти соединен с вторым входом вычитателя, первым входом четвертого порогового блока и третьим входом первого порогового блока, третий выход источника опорного напряжения соединен с вторыми входами третьего и четвертого пороговых блоков, выход вычитателя подключен к третьему входу второго порогового блока и первому входу пятого порогового блока, второй вход которого соединен с шиной Лог. О, выходы первого, второго, третьего, четвертого и пятого пороговых блоков подключены к соответствующим информационным входам дешифратора, первый, второй, третий, четвертый и пятый выходы дешифратора соединены С соответствующими информационными входами формирователя двоичных сигналов, шестой выход дешифратора соединен с соответствующим информационным входом формирователя двоичных сигналов и с первым входом блока коммутации, седьмой и восьмой выходы дешифратора соединены соответственно с вторым и третьим входами блока

коммутации, девятый и десятый выходы дешифратора через первый и второй элементы НЕ соединены соответственно с четвертым и пятым входами блока коммутации, третьи входы третьего, четвертого и пятого пороговых блоков, первый управляющий вход формирователя двоичных сигналов и второй вход блока управления объединены между собой и подключены к выходу формирователя стробирующих импульсов, первый выход блока коммутации соединен с вторым управляющим входом формирователя двоичных сигналов, первым управляющим входом дешифратора, третьим входом блока управления и четвертым входом блока аналоговой памяти, второй выход блока коммутации соединен с третьим управляющим входом формирователя двоичных сигналов, вторым управляющим входом дешифратора, четвертым входом блока управления и пятым входом блока аналоговой памяти, третий и четвертый выходы блока коммутации соединены соответственно с третьим и четвертым входами источника опорных напряжений дешифратора и с вторым и третьим входами источника опорных напряжений дешифратора и с вторым и третьим входами источника опорных напряжений, выход формирователя двоичных сигналов является выходом устройства.

1 4

0101

Фаг. 2

о о

Фиг.4$

ФИГ. 6,

Ј

1л

v

«л.

§ %

N §

va

к

1

§

,

1

Фиг. 8

fo/sod

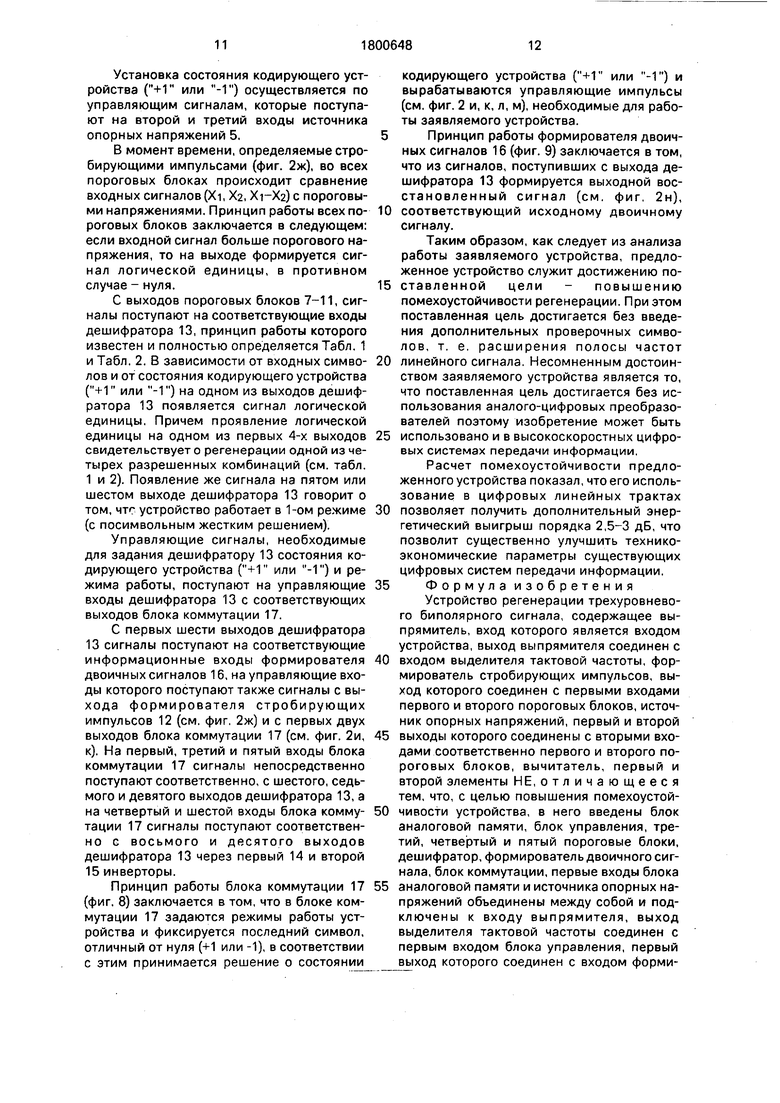

| Многоуровневый регенератор биполярных сигналов | 1986 |

|

SU1405120A1 |

| Устройство контроля трехуровневых биполярных сигналов | 1986 |

|

SU1354424A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-03-07—Публикация

1989-07-10—Подача